ERRATA

FOR

INSTRUCTION MANUAL

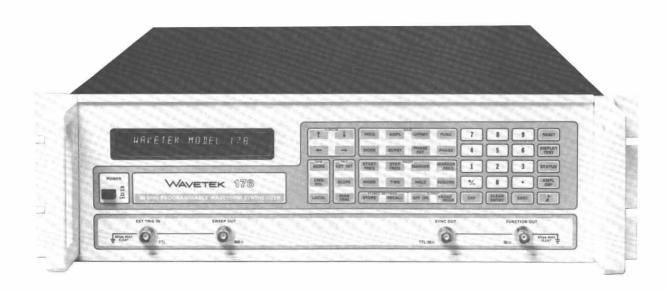

MODEL 178

50 MHz PROGRAMMABLE

WAVEFORM SYNTHESIZER

DATED 7/90

Manual Part Number: 1300-00-0168 Instrument Part Numbera: 1000-00-0169, 1000-00-0169

Make the following changes to the manual:

Pages 5-2, 5-3, 5-4 and 5-5:

Replace specified manual pages with new pages, sheets 2 through 5 of this errata.

Table 5-2. Performance Verification

| Step                                    | Check                                     | Tester                                               | Test Point | Program                     | Minimum Spec                            | Maximum Spec  |

|-----------------------------------------|-------------------------------------------|------------------------------------------------------|------------|-----------------------------|-----------------------------------------|---------------|

|                                         | Frequency Accuracy                        | <del>&amp;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~</del> | FUNC OUT   | Reset                       | 9.99995 MHz                             | 10.00005 MHz  |

| ŕ                                       | (Without Option 002)                      | <b>{</b>                                             | (Use 50Ω   | FREQ: 1E7                   |                                         |               |

| 2                                       | ,                                         |                                                      | Termina-   | FREQ: 499.99999             | 499.99749 Hz                            | 500.00249 Hz  |

| *************                           | Frequency Accuracy                        |                                                      | tion)      | FREQ: 1E7                   | 9.9999995MHz                            | 10.0000005MHz |

| 4                                       | (With Option 002)                         |                                                      | ·          | FREQ: 499.99999             | 499.9999749Hz                           | 500.0000249Hz |

|                                         | Amplitude Accuracy                        | Oscilloscope                                         |            | FREQ: 1E3                   | 9.89V                                   | 10.11V        |

|                                         | ,                                         | Plug-Ins                                             |            | AMPL: 10                    |                                         |               |

| 6                                       | ·                                         | 7A13                                                 |            | FUNC: 1                     | 9.79V                                   | 10.21V        |

| 7                                       |                                           | 7892A                                                |            | FUNC: 2                     |                                         |               |

| 8                                       |                                           |                                                      |            | FUNC: 3                     | 9.39V                                   | 10.61V        |

| 9                                       | Offset Accuracy                           |                                                      |            | FUNC: 2                     | -0.14                                   | 0.14          |

| 10                                      |                                           |                                                      |            | FUNC: 1                     |                                         |               |

| 11                                      |                                           |                                                      | ·          | FUNC: 0                     |                                         |               |

| 12                                      | Amplitude Resolution                      | t :                                                  |            | AMPL: 2.56                  | 892 mV                                  | 918 mV        |

| 3                                       |                                           | (Vrms)                                               | ·          | AMPL: 1.28                  | 444 mV                                  | 461 mV        |

| 14                                      |                                           |                                                      |            | AMPL: 1.29                  | 447 mV                                  | 465 mV        |

| 15                                      |                                           |                                                      |            | AMPL: 1.30                  | 451 mV                                  | 468 mV        |

| 16                                      |                                           |                                                      |            | AMPL: 1.32                  | 458 mV                                  | 475 mV        |

| 17                                      |                                           |                                                      |            | AMPL: 1.36                  | 470 mV                                  | 490 mV        |

| 18                                      |                                           |                                                      |            | AMPL: 1.44                  | 500 mV                                  | 518 mV        |

| 19                                      |                                           |                                                      |            | AMPL: 1.60                  | 556 mV                                  | 575 mV        |

| 20                                      |                                           | ***************************************              |            | AMPL: 1.92                  | 668 mV                                  | 690 mV        |

| 21                                      | DC Voltage Accuracy                       | : 4                                                  |            | FUNC: 4                     | 9.860V                                  | 10.140V       |

|                                         |                                           | (Vdc)                                                |            | AMPL: 0                     |                                         |               |

| 22                                      |                                           |                                                      |            | OFST: 10.00<br>OFST: -10.00 | -10,140V                                | -9.860V       |

| 23                                      |                                           |                                                      |            | OFST: 5.00                  | 4.910V                                  | 5.090V        |

| 24                                      |                                           |                                                      |            | OFST: 2.56                  | 2.494V                                  | 2.625V        |

| 25                                      |                                           |                                                      |            | OFST: 1.00                  | 0.950V                                  | 1.050V        |

| 26                                      |                                           |                                                      |            | OFST: -1.00                 | -1.050V                                 | -0.950V       |

| 27                                      |                                           | 8                                                    |            | OFST: 0                     | -40mV                                   | +40mV         |

| 28                                      |                                           |                                                      |            | OFST: 1.28                  | 1.227V                                  | 1.332V        |

| 29                                      |                                           |                                                      |            | OFST: 1.29                  | 1.23V                                   | 1.34V         |

| 30                                      |                                           |                                                      |            | OFST: 1.30                  | 1.24V                                   | 1.35V         |

| 31                                      |                                           |                                                      |            | OFST: 1.32                  | 1.26V                                   | 1.37V         |

| 32                                      | 8                                         |                                                      |            | OFST: 1.36                  | 1.30V                                   | 1.41V         |

| 33_                                     |                                           |                                                      |            | OFST: 1.44                  | 1.38V                                   | 1.49V         |

| 34                                      | 2000                                      |                                                      |            | OFST: 1.60                  | 1.54V                                   | 1.66V         |

| 35                                      | ***************************************   | ***************************************              |            | OFST: 1.92                  | 1.86V                                   | 1.98V         |

| 36                                      | Attenuator                                |                                                      | 2          | FUNC: 4                     | 3.95V                                   | 4.05V         |

| *************************************** | Accuracy                                  |                                                      |            | OFST: 4.00                  |                                         |               |

|                                         |                                           | ***************************************              | <b>3</b>   | AMPL: 0                     | *************************************** |               |

| 37                                      |                                           | ***************************************              | <b>3</b>   | OFST: 0.4                   | 0.386V                                  | 0.414V        |

| -38                                     |                                           | S S S S S S S S S S S S S S S S S S S                | 5-         | OFST: 0.04                  | 0.038V                                  | 0.042V        |

| 39_[                                    | 8<br>000000000000000000000000000000000000 | ·····                                                |            | OFST: 0.004                 | 0.00378V                                | 0.00422V      |

Table 5-2. Performance Verification (Continued)

| Step                                    | Check                                  | Tester                                 | Test Point                              | Program                                 | Minimum Spec                                      | Maximum                                   | Spec                                    |

|-----------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------------------------|-------------------------------------------|-----------------------------------------|

|                                         | For steps 40 through                   | 1 42, record th                        | e indicated if                          | ems at the worst ca                     | ise harmonic (typic                               | ally the seco                             | ond                                     |

| ******************************          | or third)                              | ************************************** |                                         | ***                                     |                                                   |                                           |                                         |

| 40                                      | Sine Distortion                        | Spectrum                               | Connect                                 | AMPL: 2.82                              | Fundamental:                                      |                                           | *************************************** |

|                                         |                                        | Analyzer                               | front panel                             | FREQ: 5kHz to                           | Frequency                                         |                                           | kHz                                     |

|                                         |                                        | Settings:                              | TUNC OUT<br>through X5                  | 50kHz in 5kHz                           | Amplitude:                                        |                                           | d8m                                     |

|                                         |                                        | State;                                 | atten. to                               | Steps                                   | Harmonic:                                         |                                           |                                         |

|                                         |                                        | Preset                                 | analyzer                                |                                         | Amplitude:                                        |                                           | dBm                                     |

|                                         |                                        | Atten;                                 | *100 Hz<br>1.5 GHz                      | (Harmonic Amplitud                      | le must be at least                               | 55 dBm beli                               | OW.                                     |

| *************************************** |                                        | 30 dB                                  | INPUT                                   | the Fundamental A                       | mplitude)                                         | ************                              | ************                            |

| 41                                      |                                        | Ref Level;                             |                                         | FREQ: 50kHz to                          | Fundamental:                                      |                                           |                                         |

|                                         |                                        | 0 dB                                   | 4                                       | 300kHz in 50kHz                         |                                                   |                                           |                                         |

|                                         |                                        | Mixer Level;                           |                                         | Steps                                   | Amplitude                                         |                                           | dBm                                     |

|                                         | '                                      | -30 <b>dB</b> m                        |                                         | FREQ: 300kHz to                         | 2                                                 |                                           |                                         |

|                                         |                                        | Start Freq;                            |                                         | 500kHz in 20kHz                         | Amplitude:                                        |                                           | dBm                                     |

|                                         |                                        | 1.2 X Freq.                            |                                         | Steps                                   | <b>*</b>                                          |                                           |                                         |

|                                         |                                        | Stop Freq;                             |                                         | (Harmonic Amplitud                      | le must be at least                               | 40 dBm beli                               | OW                                      |

|                                         |                                        | 3.5 X Start                            |                                         | the Fundamental A                       | mplitude)                                         |                                           |                                         |

| *************************************** |                                        | freq.                                  |                                         | *************************************** | googoooooo                                        | ^^^^                                      | *************************************** |

| 42                                      |                                        |                                        |                                         | FUNC: 0                                 | Fundamental:                                      |                                           |                                         |

|                                         |                                        |                                        |                                         | FREQ: 5MHz to                           |                                                   |                                           |                                         |

|                                         |                                        |                                        |                                         | 50MHz in 5MHz                           | Amplitude;                                        | ***************************************   | dBm                                     |

|                                         |                                        |                                        |                                         | }                                       | Harmonic:                                         |                                           | -                                       |

|                                         |                                        |                                        |                                         | 27.5MHz                                 |                                                   |                                           |                                         |

|                                         |                                        |                                        |                                         | (Harmonic Amplitud                      |                                                   | 30 d8m bek                                | )W                                      |

|                                         | ······································ | ************************************   | *************************************** | the Fundamental A                       | <del>qaankaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa</del> |                                           |                                         |

| 43                                      | Spurious Level                         | Spectrum                               | Connect                                 | ¥                                       | All spurs at least                                | 44 dBc belo                               | W                                       |

|                                         |                                        | Analyzer                               | front panel<br>FUNCOUT                  |                                         | fundamental                                       |                                           |                                         |

|                                         |                                        | Settings:                              | through X5                              | <b>3</b>                                | ***************************************           |                                           |                                         |

|                                         |                                        | 3                                      | atten. to                               |                                         |                                                   |                                           |                                         |

|                                         |                                        | Ref. Level;                            | analyzer<br>*100 Hz                     |                                         | •                                                 |                                           |                                         |

|                                         |                                        | 20dB                                   | 1.5 GHz                                 |                                         |                                                   |                                           |                                         |

|                                         |                                        | opan,                                  | INFO.                                   |                                         | 5000                                              |                                           |                                         |

|                                         |                                        | 20kHz                                  |                                         |                                         |                                                   |                                           |                                         |

|                                         |                                        | Center Freq;                           |                                         | -                                       |                                                   |                                           |                                         |

|                                         |                                        | 1.005 MHz                              |                                         |                                         |                                                   |                                           |                                         |

| 44                                      |                                        | 24.005 MHz                             |                                         | FREO: 24005E3                           |                                                   |                                           |                                         |

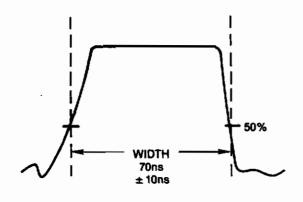

| 4.5                                     |                                        | 48.005 MHz                             |                                         | FREQ: 48005E3                           | Rise/Fall Time                                    |                                           |                                         |

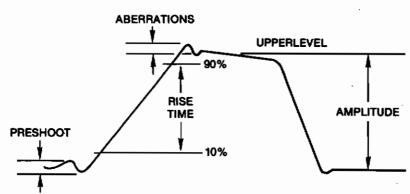

| 46                                      | Rise/Fall Time                         | Oscilloscope                           | FUNCOUT<br>(Use 50Ω                     | FREQ: 6E6                               | ruse/ran inne                                     | ≤12ns (E                                  | 1                                       |

|                                         | (Measured between                      | Plug-in                                | Termina-                                | FUNC: 2                                 | Aberrations                                       | transiti<br>≤5% ± 50                      |                                         |

|                                         | 10 and 90% points)                     | 7S14                                   | tion and                                | AMPL: 20                                | A06118110118                                      |                                           | 3                                       |

|                                         | and Aberrations                        |                                        | X5 Atten.*                              |                                         |                                                   | (Of peak to voltage)                      | manage.                                 |

| A ==                                    |                                        |                                        |                                         | AMPL: 10                                | Rise/Fall Time                                    | vonaye/<br>≤10ns (E:                      | art                                     |

| 47                                      |                                        |                                        |                                         | AMPL: 5                                 | 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2           | transiti                                  | :                                       |

| 48                                      |                                        |                                        |                                         | LY(4)(£ 2° € ∩                          | Aberrations                                       | ≤5% ± 50                                  |                                         |

|                                         |                                        |                                        |                                         |                                         | rwa:anviia                                        | (Of peak to                               |                                         |

|                                         |                                        |                                        |                                         |                                         |                                                   | voitage)                                  | moon                                    |

|                                         |                                        |                                        |                                         | L                                       |                                                   | * # # 1 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |                                         |

Table 5-2. Performance Verification (Continued)

| Step                                    | Check                | Tester        | Test Point                              | Program                              | Minimum Spec                            | Maximum Spec                            |

|-----------------------------------------|----------------------|---------------|-----------------------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------|

| 49                                      | Trigger Baseline     | Multimeter    | FUNCOUT                                 | FREQ: 200kHz                         | -100mV                                  | 100mV                                   |

|                                         | (Without Trigger     | (Vdc)         | (Use 50Ω                                | AMPL: 10                             | <i>*</i>                                |                                         |

|                                         | Input)               |               | Termina-                                | MODE (Main): 1                       |                                         |                                         |

| *************************************** |                      |               | tion)                                   | FUNC: 0                              | *************************************** |                                         |

| 50                                      |                      |               |                                         | MODE (Main): 4                       | -5.1V                                   | -4.9V                                   |

| 51                                      | Trigger Baseline     | Counter       |                                         | MODE (Main): 0                       | 199,9kHz                                | 200.1kHz                                |

| 52                                      | (With Trigger Input) |               |                                         | MODE (Main): 1                       | 10.05kHz                                | 10.15kHz                                |

|                                         |                      |               |                                         | (Connect 10.1kHz                     |                                         |                                         |

|                                         |                      |               |                                         | TTL signal to TRIG                   |                                         |                                         |

|                                         |                      |               |                                         | (N connector)                        | *************************************** |                                         |

| 53                                      |                      |               |                                         | MODE (Main): 2                       | 100.5kHz                                | 101.5kHz                                |

| 54                                      |                      |               | X<br>6<br>8                             | MODE (Main): 3                       | 70.35kHz                                | 71.05kHz                                |

| *************************************** |                      |               | *************************************** | BURST Count: 7                       | 000000000000000000000000000000000000000 |                                         |

| 55                                      |                      |               |                                         | MODE (Main): 4                       | 10.05kHz                                | 10.15kHz                                |

| 56                                      |                      |               |                                         | MODE (Main): 5                       | 100.5kHz                                | 101.5kHz                                |

| 57                                      |                      |               |                                         | MODE (Main): 6                       | 70.35kHz                                | 71.05kHz                                |

|                                         |                      |               |                                         | BURST Count: 7                       | 222.220.000000000000000000000000000000  |                                         |

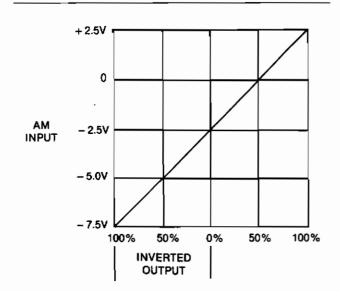

| 58                                      | AM Input             | Multimeter    |                                         | MODE: 0                              | Record Results                          | s les l'homes                           |

|                                         |                      | (Vrms)        |                                         | FUNC: 5                              | (Should be approxing                    |                                         |

|                                         |                      |               |                                         | (Connect 0Vdc to                     |                                         | , , , , , , , , , , , , , , , , , , , , |

|                                         | ·                    |               |                                         | AM IN connector)                     |                                         |                                         |

| 59                                      | ·                    |               |                                         | Step AM IN from                      | Record AM IN do vo                      | itage corre-                            |

|                                         | ·                    |               |                                         | -3.5Vdc to -2Vdc                     | aponding to a minimum Ymms              |                                         |

|                                         |                      |               |                                         | in 0.1Vdc steps                      | output (-0.1 to +0.1)                   |                                         |

| 60                                      |                      |               |                                         | Step AM IN from                      | Record AM IN do vo                      | Itage corre-                            |

|                                         |                      |               |                                         | 2Vdc to 3.5Vdc                       | sponding to an inpu                     | voltage of                              |

|                                         |                      |               |                                         | in 0.1Vdc steps                      | twice step 58 Resul                     | ts.                                     |

| 61                                      |                      | Calculation   |                                         | Step 60 Results -<br>Step 59 Results | 4.752V                                  | 6.048V                                  |

| 62                                      | Reference Input/     | Counter       | REFOUT                                  | Reset                                | 999.993 kHz                             | (No deviation)                          |

|                                         | Output               | Signal Source | Connect                                 |                                      |                                         |                                         |

|                                         | •                    | Func; Square  | Signal                                  |                                      |                                         |                                         |

|                                         |                      | Ampl; 2.5V    |                                         |                                      |                                         |                                         |

|                                         |                      | Freq:         | *Function                               | ·                                    |                                         |                                         |

|                                         |                      | 999.993 kHz   | }                                       | 1.                                   |                                         | ·                                       |

| 63                                      |                      | Signal Source |                                         |                                      | 1.000007 MHz                            | (No deviation)                          |

|                                         |                      | Freq change   | 3                                       |                                      | w                                       | ,                                       |

| į                                       |                      | 1.000007MHz   | 2 .                                     | .*                                   |                                         |                                         |

| 64                                      |                      | Signal Source | t :                                     |                                      | 9.99993 MHz                             | (No deviation)                          |

| ~ .                                     |                      | Freq change   |                                         |                                      |                                         |                                         |

|                                         |                      | 9.99993 MHz   |                                         |                                      |                                         |                                         |

| 65                                      |                      | Signal Source | 5                                       |                                      | 10.00007MHz                             | (No deviation)                          |

| *                                       |                      | Freq change   |                                         |                                      |                                         |                                         |

|                                         |                      | 10.00007MHz   |                                         |                                      |                                         |                                         |

Table 5-2. Performance Verification (Continued)

| Step                                    | DOGGAMANAWAWAWAWAWAWAWAWAWAWAWAWAWAWAWAWAWAW | Tester     | Test Point                                       | Program           | Minimum Spec                            | Maximum Spec                            |

|-----------------------------------------|----------------------------------------------|------------|--------------------------------------------------|-------------------|-----------------------------------------|-----------------------------------------|

| 66                                      | Linear Sweep                                 | Connect;   | See                                              | SWEEP MODE: 3     | -100 mVdc                               | +100 mVdc                               |

|                                         | Start Voltage/Freq.                          | SWEEPOUT   | "Tester"                                         | Trig. Linear Ramp | 9.999 kHz                               | 10.001 kHz                              |

| 67                                      | Linear Sweep                                 | to DMM     | column                                           | START FREQ:       | 4.5 Vdc                                 | 5.5 Vdc                                 |

| *************************************** | Stop Voltage/Freq.                           |            |                                                  | 10 kHz            | 19.999 kHz                              | 10.001 kHz                              |

| 68                                      | Log Sweep                                    | SYNCOUT    |                                                  | STOP FREQ:        | 9.999 kHz                               | 10.001 kHz                              |

| 300000000000000000000000000000000000000 | Start Frequency                              | to Counter |                                                  | 20 kHz            | *************************************** |                                         |

| . 69                                    | Log Sweep                                    |            |                                                  | SWEEP TIME:       | 19.999 kHz                              | 20.001 kHz                              |

|                                         | Stop Frequency                               |            |                                                  | 0.01              |                                         |                                         |

|                                         |                                              |            |                                                  | Use "MAN TRIG"    |                                         |                                         |

|                                         | <u>~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~</u> |            | <del>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,</del> | to initiate sweep | *************************************** | *************************************** |

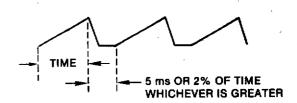

| 70                                      | Sweep Time                                   | Counter    | FUNCOUT                                          | Reset             | 1233.9 ms                               | 1234.1 ms                               |

|                                         |                                              |            | (Use 50Ω                                         | FREQ: 200 kHz     |                                         |                                         |

|                                         |                                              |            | Termina-                                         | AMPL: 2.5         |                                         |                                         |

| 000                                     |                                              |            | tion)                                            | FUNC: Square      |                                         |                                         |

|                                         |                                              |            |                                                  | MODE: Trig        |                                         |                                         |

|                                         |                                              |            |                                                  | TRIG Mode: INT    |                                         |                                         |

|                                         |                                              |            |                                                  | SWEEP TIME:       |                                         |                                         |

|                                         |                                              |            |                                                  | 1234 ms           | *************************************** |                                         |

| 71                                      |                                              |            |                                                  | Sweep Time;       | 43.205 ms                               | 43.215 ms                               |

|                                         |                                              | ~~~~       |                                                  | 43.21 ms          | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~  | ·····                                   |

| 72                                      | Marker/Output                                | Multimeter | MARKER                                           | Reset             |                                         | m n 1/ .                                |

|                                         | Status                                       | (Vdc)      | OUT (TTL)                                        | FREQ: 999.99 Hz   |                                         | 0.5 Vdc                                 |

| 73                                      |                                              |            |                                                  | FREQ: 5000.01 Hz  | 2.5V                                    | 5.0V                                    |

| 74                                      |                                              |            |                                                  | MARKER #: 10      | 0 V                                     | ,0.5 Vdc                                |

|                                         |                                              |            |                                                  | MARKER FREQ:      |                                         |                                         |

| 30000                                   |                                              | 80         |                                                  | 5 kHz             |                                         |                                         |

| 5000                                    |                                              |            |                                                  | MAIN FREQ:        | <b>、</b>                                |                                         |

|                                         |                                              |            |                                                  | 4.99999 kHz       | 2.4 Vdc                                 |                                         |

| 75                                      |                                              |            |                                                  | MAIN FREQ:        |                                         | 5.0 Vdc                                 |

|                                         | 1                                            |            |                                                  | 5.00001 kHz       |                                         |                                         |

**OPERATOR'S & MAINTENANCE MANUAL**

# Model 178 50 MHz Programmable Waveform Synthesizer

© 1986 Wavetek

This document contains information proprietary to Wavetek and is provided solely for instrument operation and maintenance. The information in this document may not be duplicated in any manner without the prior approval in writing from Wavetek.

WAVETEK SAN DIEGO, INC. 9045 Balboa Ave., San Diego, CA 92123 P. O. Box 85265, San Diego, CA 92138 Tel 619/279-2200 TWX 910/335-2007

Manual Revision: 7/90 Manual Part Number: 1300-00-0168 Instrument Part Number: 1000-00-0168

#### WARRANTY

Wavetek warrants that all products manufactured by Wavetek conform to published Wavetek specifications and are free from defects in materials and workmanship for a period of one (1) year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Wavetek arising from a Warranty claim shall be limited to repairing, or at its option, replacing without charge, any product which in Wavetek's sole opinion proves to be defective within the scope of the Warranty. In the event Wavetek is not able to modify, repair or replace non-conforming defective parts or components to a condition as warrantied within a reasonable time after receipt thereof, Buyers shall be credited for their value at the original purchase price.

Wavetek must be notified in writing of the defect or nonconformity within the Warranty period and the affected product returned to Wavetek's factory or to an authorized service center within (30) days after discovery of such defect or nonconformity.

For product warranties requiring return to Wavetek, products must be returned to a service facility designated by Wavetek. Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Wavetek for warranty service. Except for products returned to Buyer from another country, Wavetek shall pay for return of products to Buyer.

Wavetek shall have no responsibility hereunder for any defect or damage caused by improper storage, improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, accident or for any product which has been repaired or altered by anyone other than Wavetek or its authorized representative and not in accordance with instructions furnished by Wavetek.

#### **Exclusion of Other Warranties**

The Warranty described above is Buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Wavetek specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. No statement, representation, agreement, or understanding, oral or written, made by an agent, distributor, representative, or employee of Wavetek, which is not contained in the foregoing Warranty will be binding upon Wavetek, unless made in writing and executed by an authorized Wavetek employee. Under no circumstances shall Wavetek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

## **CONTENTS**

| SECTION 1 | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|           | 1.1 THE MODEL 178 1.2 ADDITIONAL STORED SETTINGS OPTION 1.3 SPECIFICATIONS 1.3.1 Versatility 1.3.2 Main Generator 1.3.2.1 Frequency Resolution 1.3.2.2 Frequency Precision 1.3.2.3 Amplitude Precision 1.3.2.4 Waveform Characteristics 1.3.3 Sweep Generator 1.3.3.1 Sweep Modes 1.3.3.2 Sweep Characteristics 1.3.3.3 Pulses 1.3.4 General 1.4 OPTIONS                                     | 1-1<br>1-1<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4                                           |

| SECTION 2 | INSTALLATION AND INTERFACE                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

|           | 2.1 MECHANICAL INSTALLATION 2.2 ELECTRICAL INSTALLATION 2.2.1 Power Connection 2.2.2 Signal Connections 2.2.3 GPIB Connections 2.2.4 GPIB Address 2.2.5 Intial Checkout and Operation                                                                                                                                                                                                        | 2-1<br>2-1<br>2-1<br>2-2<br>2-2                                                                       |

| SECTION 3 | OPERATION                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|           | 3.1 DATA ENTRY 3.2 POWER 3.3 BASIC COMMAND STRUCTURE 3.3.1 Characters 3.3.2 Action Vs Parameters 3.3.3 Programming Parameter Values 3.4 ERRORS 3.4.1 Class 1 Errors 3.4.2 Class 2 Errors 3.4.3 Class 3 Errors 3.5 EXECUTING THE PROGRAM 3.6 CURSOR 3.7 TRIGGER MODE AND SLOPE 3.8 MAIN GENERATOR 3.8.1 Frequency 3.8.2 Amplitude 3.8.3 Offset 3.8.4 Function 3.8.5 Modes 3.9 SWEEP GENERATOR | 3-2<br>3-2<br>3-3<br>3-4<br>3-4<br>3-5<br>3-5<br>3-5<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8<br>3-8<br>3-8 |

## **CONTENTS (Continued)**

|           | 3.3.1 Start and Stop Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|           | 3.9.2 Sweep Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-11   |

|           | 3.9.3 Sweep Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-11   |

|           | 3.9.4 Sweep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-11   |

|           | 3.9.5 Hold and Resume                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-11   |

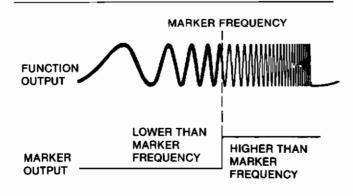

|           | 3.9.6 Marker, Marker Frequency and Marker Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-12   |

|           | 3.10 STORED SETTINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|           | 3.10.1 Storing Program Sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|           | 3.10.2 Recalling Stored Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|           | 3.10.3 High Speed Recall of Stored Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |