# SERVICING HANDBOOK

Volume 1

4920M

Alternating Voltage Measurement Standard

Datron Instruments Ltd. 52 Hurricane Way, Norwich Airport, Norwich, Norfolk NR6 6JB, England. Documentation Part No. 850262-1

# SERVICING HANDBOOK

for

# THE DATRON 4920M

# ALTERNATING VOLTAGE MEASUREMENT STANDARD

Volume 1

Calibration and Servicing Information

**Technical Descriptions**

For any assistance contact your nearest Datron Sales and Service center.

Addresses can be found at the back of this handbook.

850262

Issue 1 (July 1990)

@ 1990 Datron Instruments

# DANGER HIGH VOLTAGE

# THIS INSTRUMENT IS CAPABLE OF DELIVERING A LETHAL ELECTRIC SHOCK! when connected to a high voltage source

Input plugs carry the Full Input Voltage

THIS CAN KILL!

Overvoltage can damage your instrument!

Unless you are sure that it is safe to do so, DO NOT TOUCH

any terminals connected to the inputs

DANGER

#### **Volume 1 Contents**

Servicing Diagrams and Component Lists.

General Description, Installation, Controls, Operation, Remote Applications; Specifications, Specification Verification and Routine Calibration.

Refer to Volume 2

Refer to User's Handbook

|       | Section | n    | Title                                                                                                                                           | Page |  |  |  |

|-------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| 1 CAL |         | CALI | LIBRATION                                                                                                                                       |      |  |  |  |

|       |         | 1.1  | Routine Calibration References                                                                                                                  | 1.1  |  |  |  |

|       |         | 1.2  | Internal Access                                                                                                                                 |      |  |  |  |

|       |         | 1.3  |                                                                                                                                                 |      |  |  |  |

|       |         |      | Remote Calibration via the IEEE 488 Interface                                                                                                   |      |  |  |  |

|       |         | 1.4  | Special Calibration                                                                                                                             | 1-1  |  |  |  |

|       |         |      | 1.4.2 Wideband Linearity Calibration - WLin' Key                                                                                                | 1-2  |  |  |  |

|       |         |      | 1.4.3 10Hz Filter Calibration - 'Filt' Key                                                                                                      | 1-4  |  |  |  |

|       |         |      | 1.4.4 Flatness Calibration - 'Flat' Key                                                                                                         | 1-5  |  |  |  |

|       |         |      | 1.4.5 ACV Linearity Calibration - 'ALin' Key                                                                                                    | 1-13 |  |  |  |

|       |         |      | 1.4.6 Clear the Non-Volatile RAM Calibration Memory - 'ClrNV' Key                                                                               | 1-14 |  |  |  |

|       | 2       | GUID | E TO 4920M FAULT DIAGNOSIS                                                                                                                      |      |  |  |  |

|       |         | 2.1  | Introduction                                                                                                                                    | 2-1  |  |  |  |

|       |         |      | 2.1.1 Use of Error Codes                                                                                                                        | 2-1  |  |  |  |

|       |         |      | 2.1.2 Code Groupings                                                                                                                            | 2-1  |  |  |  |

|       |         |      | 2.1.3 'Operational' and 'Diagnostic' Selftest                                                                                                   | 2-2  |  |  |  |

|       |         |      |                                                                                                                                                 |      |  |  |  |

|       |         | 2.2  | 9000 Series Codes - Fatal System Errors                                                                                                         | 2-2  |  |  |  |

|       |         |      | 2.2.1 Introduction                                                                                                                              | 2-2  |  |  |  |

|       |         |      | 2.2.2 Immediate Action                                                                                                                          | 2-2  |  |  |  |

|       |         | • •  |                                                                                                                                                 |      |  |  |  |

|       | Ė       | 2.3  | Command Errors                                                                                                                                  | 2-3  |  |  |  |

|       |         |      | 2.3.1 Introduction                                                                                                                              | 2-3  |  |  |  |

|       |         |      | 2.3.3 Remote Operation                                                                                                                          | 2-3  |  |  |  |

|       |         | 2.4  | 1000 Series Codes - Execution Errors                                                                                                            |      |  |  |  |

|       |         | 2.4  | 2.4.1 Introduction                                                                                                                              |      |  |  |  |

|       |         |      | 2.4.2 Local Operation                                                                                                                           | 2-3  |  |  |  |

|       |         |      | 2.4.3 Remote Operation                                                                                                                          | 2-3  |  |  |  |

|       |         |      | 2.4.4 Execution Error Codes                                                                                                                     | 2-3  |  |  |  |

|       |         | 2.5  | Device-Dependent Errors - Index                                                                                                                 | 2-4  |  |  |  |

|       |         |      | 2.5.1 Introduction                                                                                                                              | 2-4  |  |  |  |

|       |         |      | 2.5.2 Local Operation                                                                                                                           | 2-4  |  |  |  |

|       |         |      | 2.5.3 Remote Operation                                                                                                                          | 2-4  |  |  |  |

|       |         |      | 2.5.4 Index of Device-Dependent Error Codes - Normal and Calibration Operations     Index of Device-Dependent Error Codes - Selftest Operations | 2-5  |  |  |  |

|       |         |      |                                                                                                                                                 |      |  |  |  |

|       |         | 2.6  | 4000 Series Codes - Fault Localization                                                                                                          |      |  |  |  |

|       |         | 2.7  | Test Descriptions                                                                                                                               | 2-8  |  |  |  |

|       |         |      | 2.7.1 General                                                                                                                                   | 2-8  |  |  |  |

|       |         |      | 2.7.2 Selftest Error Codes                                                                                                                      | 2-8  |  |  |  |

|       |         |      | 2.7.3 Test Pathways                                                                                                                             | 2-8  |  |  |  |

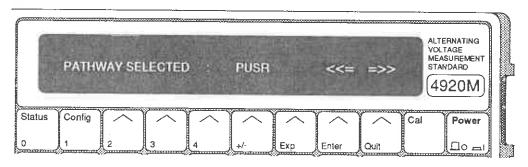

|       |         |      | 2.7.4 Access to Test Pathways via the 4920M Menu Keys                                                                                           | 2-8  |  |  |  |

|       |         |      | 2.7.5 Activating the Test Pathway                                                                                                               | 2-9  |  |  |  |

|       |         |      |                                                                                                                                                 |      |  |  |  |

| Sect | ion  | Title                                                                                                                                                                                                                                                     | Pag                                           |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 3    | DIS  | MANTLING AND REASSEMBLY                                                                                                                                                                                                                                   |                                               |

|      | 3.1  | General Precautions                                                                                                                                                                                                                                       | 2 4                                           |

|      | 3.2  | General Mechanical Layout 3.2.1 Front Panel 3.2.2 Rear Panel                                                                                                                                                                                              | 3-1                                           |

|      | 3.3  | Location and Access 3.3.1 External Construction 3.3.2 Internal Construction                                                                                                                                                                               | 3-2                                           |

|      | 3.4  | General Access 3.4.1 Top Cover 3.4.2 Bottom Cover 3.4.3 Front Bezel 3.4.4 Rear Panel Assembly                                                                                                                                                             | 3-3<br>3-3<br>3-3                             |

|      | 3.5  | Sub-Assembly Removal and Fitting  3.5.1 Digital PCB  3.5.2 Display PCB  3.5.3 Front Panel Switch PCB  3.5.4 'ACV' N-Type Input Socket  3.5.5 A-D / Control PCB  3.5.6 AC Wide Band PCB  3.5.7 High Accuracy ACV Preamplifier  3.5.8 High Accuracy ACV PCB | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8 |

|      | 3.6  | Transformer Assemblies                                                                                                                                                                                                                                    | 3-10                                          |

| 4    | SERV | /ICING                                                                                                                                                                                                                                                    |                                               |

|      | 4.1  | Routine Servicing                                                                                                                                                                                                                                         | A-1                                           |

|      | 4.2  | Adjustment Following Replacement of PCBs                                                                                                                                                                                                                  | 40<br>40                                      |

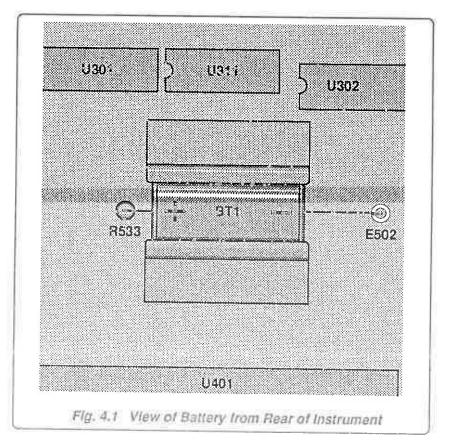

|      | 4.3  | Lithlum Battery - Replacement                                                                                                                                                                                                                             | 4-3                                           |

| 5    | TECH | INICAL DESCRIPTIONS                                                                                                                                                                                                                                       |                                               |

|      | 5.1  | Principles of Operation                                                                                                                                                                                                                                   | <b>5-3</b><br>5-3<br>5-3                      |

|      |      | FCB Descriptions 5.2.1 High Accuracy AC Pre-amp PCB 5.2.2 High Accuracy AC PCB 5.2.3 Wide Band AC PCB 5.2.4 Analog-to-Digital Conversion 5.2.5 Internal References 5.2.6 Digital PCB 5.2.7 Serial Data Interface                                          | 5-7<br>5-7<br>5-8<br>5-14<br>5-16             |

### **List of Illustrations**

| Se     | ection      | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page |  |  |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| 1 CALI |             | BRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |  |  |

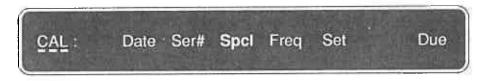

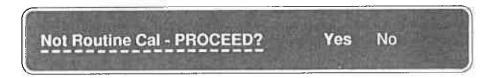

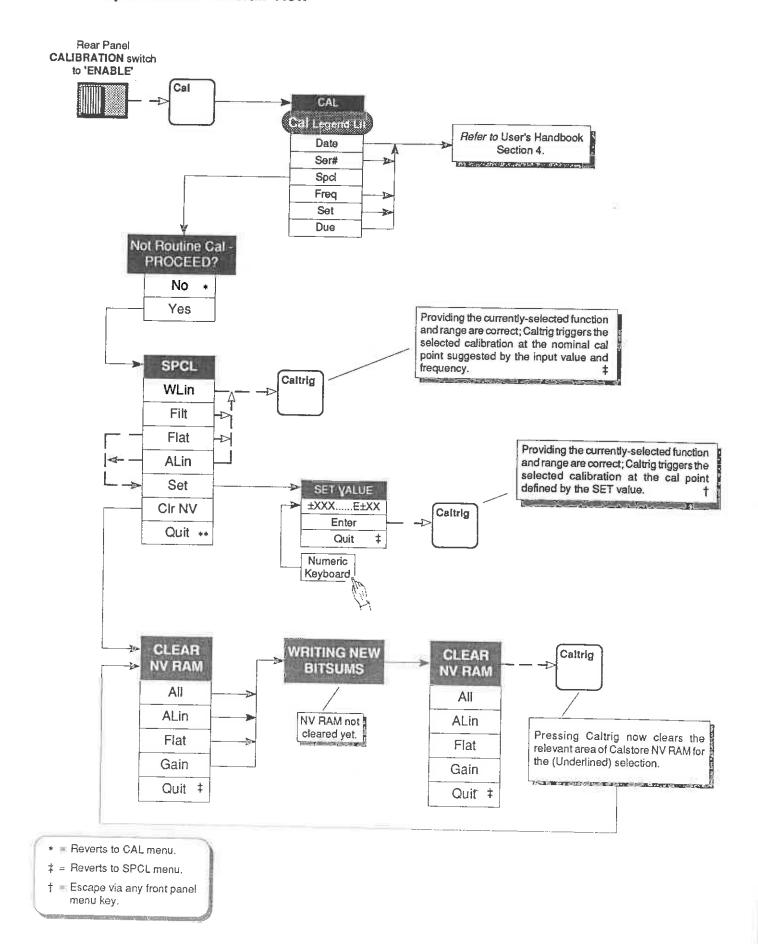

| ٠      |             | CAL and SPCL Menus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-2  |  |  |

|        |             | SPCL Group of Menus - Overall View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |  |  |

| Eid    | g. 1,4.1    | Flatness Calibration - Interconnections for ACV Ranges and 1V WBV Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |  |  |

|        | g. 1,4.2    | WBV 3V Range Flatness Calibration - Interconnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |  |  |

|        | g. 1.8.3    | "ALIn" ACV Linearity Calibration - Interconnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |  |  |

| 1 17   | g. 10.0     | Act directly construct the second sec |      |  |  |

| 2      | GUID        | DE TO 4920M FAULT DIAGNOSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |  |  |

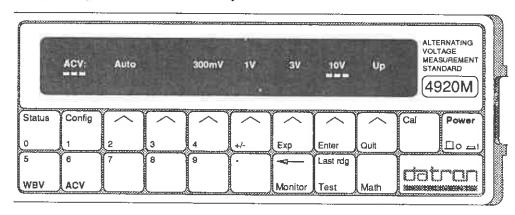

|        |             | Activating the Test Pathway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-9  |  |  |

| 2      | DIEN        | JANTLING AND REASSEMBLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| 3      | אופוע       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |  |

|        |             | No illustrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |  |  |

| 4      | CEDI        | WICING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |  |  |

| 4      | _           | VICING  View of Battery from Rear of Instrument                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3  |  |  |

| Fl     | g. 4.1      | View of Battery from Hear of Instrument                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . •  |  |  |

| 5      | TEC         | HNICAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |  |  |

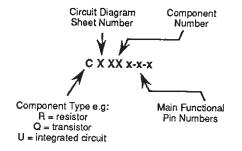

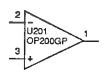

| Fl     | g. 5.1.1.1  | 4920M Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |  |  |

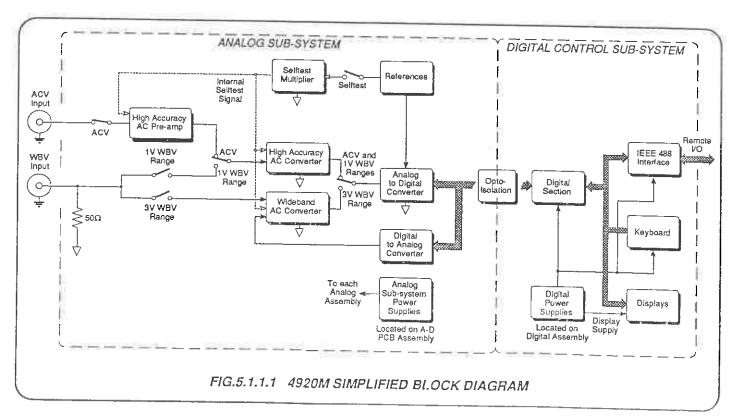

| FI     | g. 5.1.2.1  | High Accuracy AC Measurement Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |  |  |

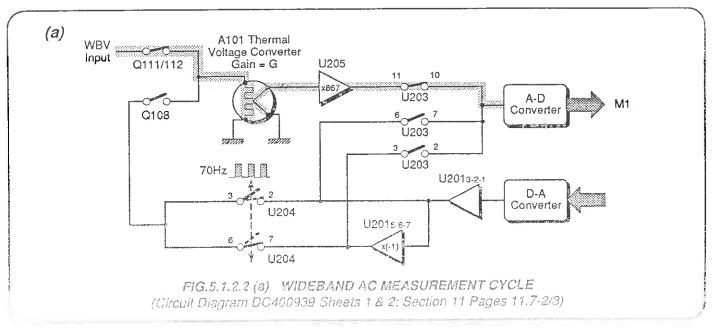

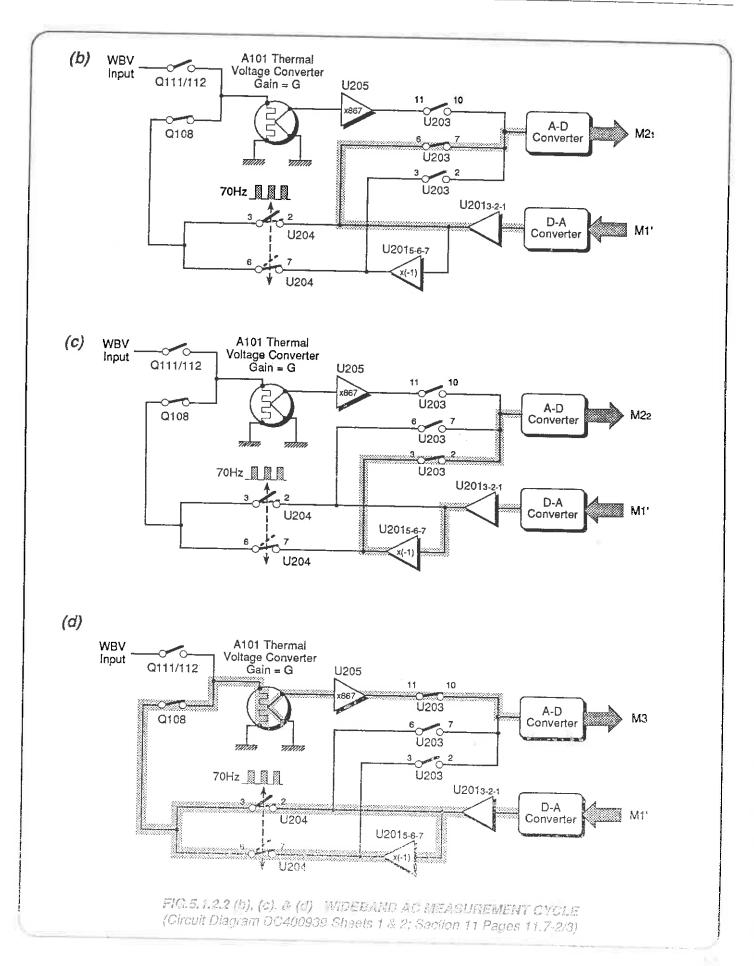

| Fi     | g. 5.1.2.2  | Wideband AC Measurement Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |  |  |

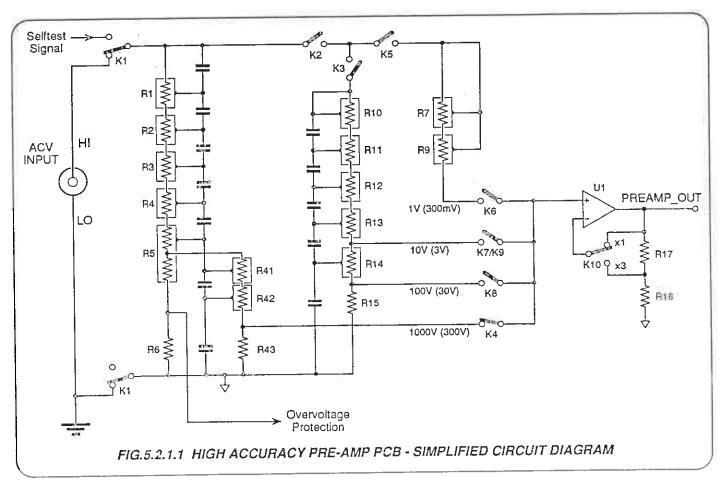

| F      | g. 5.2.1.1  | High Accuracy Pre-amp PCB - Simplified Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |  |  |

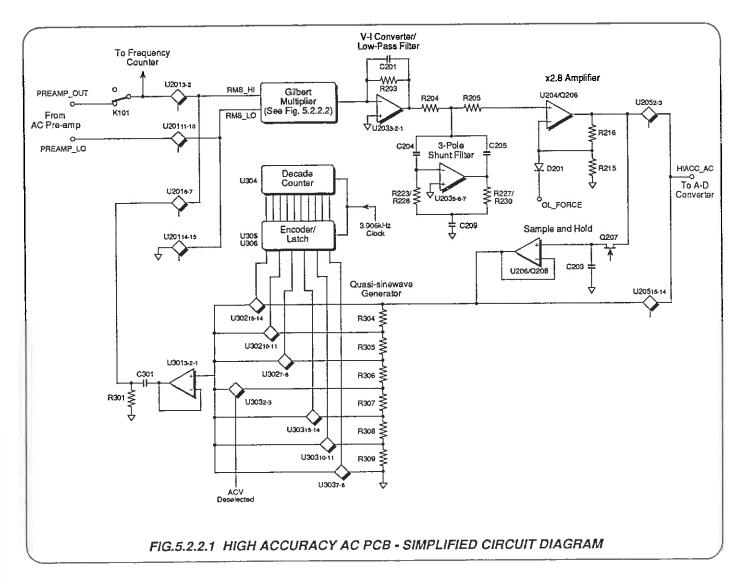

| FI     | g. 5.2.2.1  | High Accuracy AC PCB - Simplified Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |  |  |

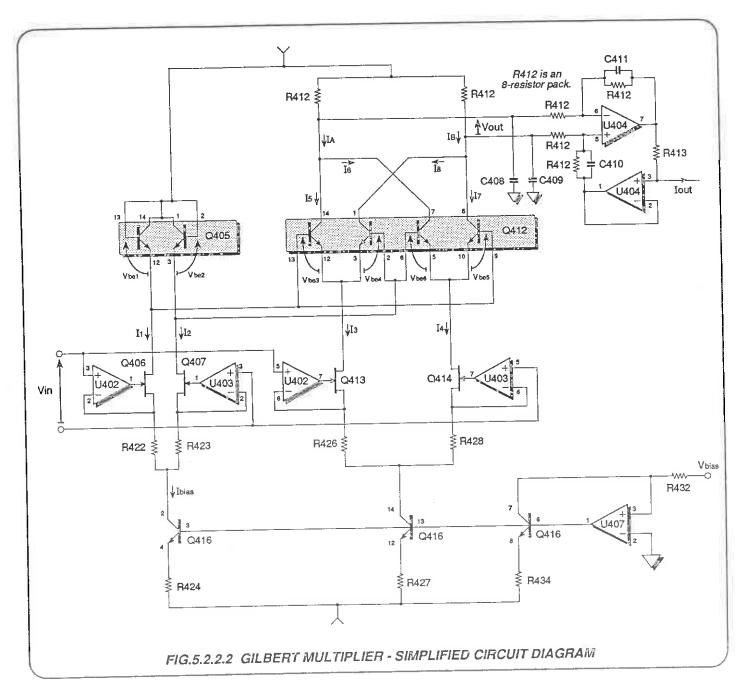

| F      | g. 5.2.2.2  | Glibert Multiplier - Simplified Circuit Dizgram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |  |

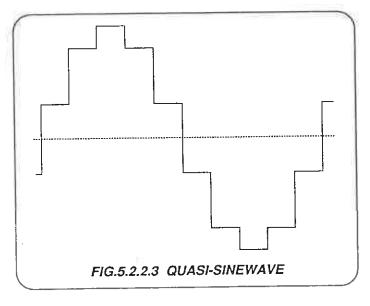

| FI     | g. 5.2.2.3  | Quasi-Sinewave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |  |  |

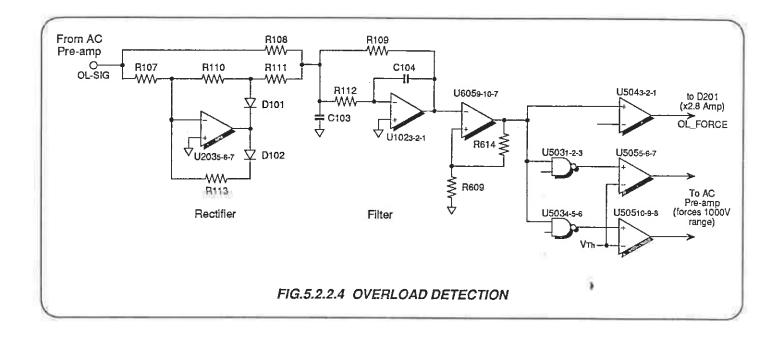

| Fi     | g. 5.2.2.4  | Overload Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |  |  |

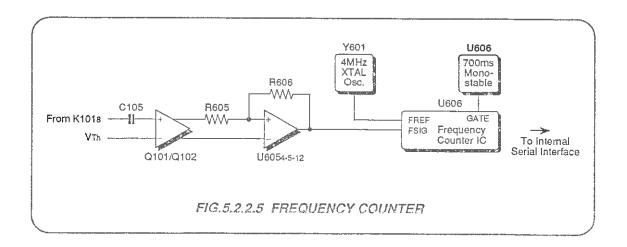

| FI     | g. 5.2.2.5  | Frequency Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |  |  |

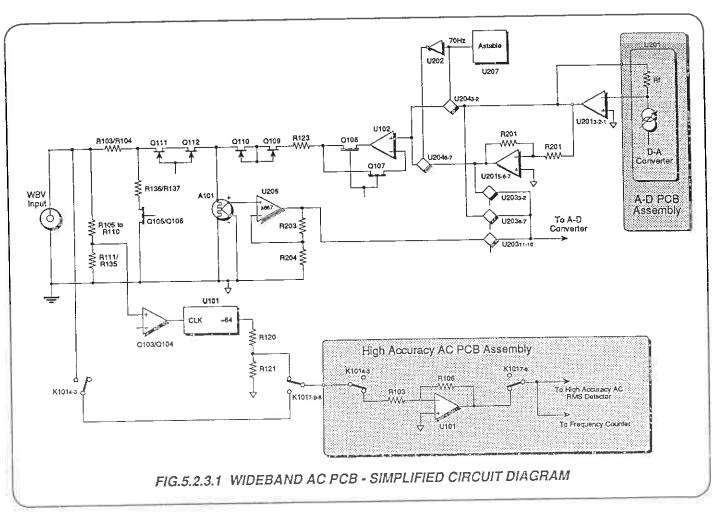

| FI     | g. 5.2.3.1  | Wideband AC PCB - Simplified Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |  |  |

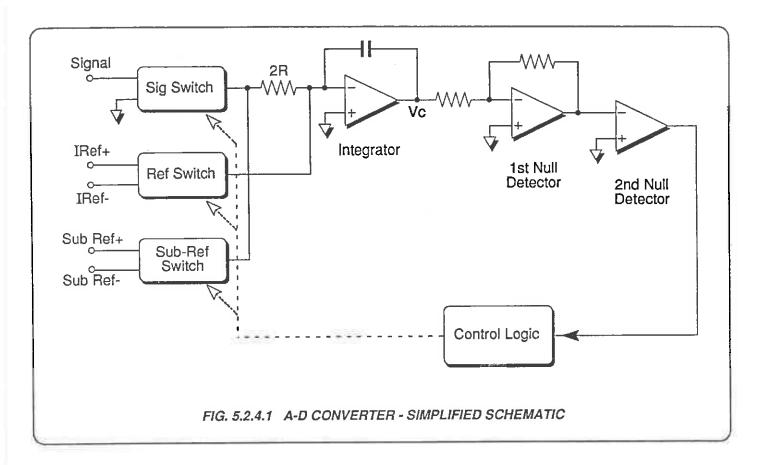

| FI     | g. 5.2.4.1  | A-D Converter - Simplified Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |  |  |

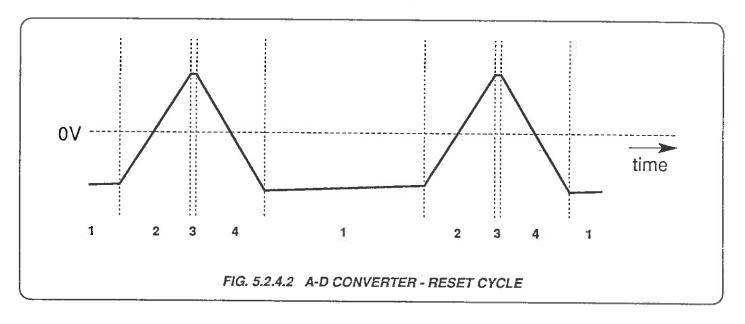

| FI     | g. 5.2.4.2  | A-D Converter - Reset Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |  |  |

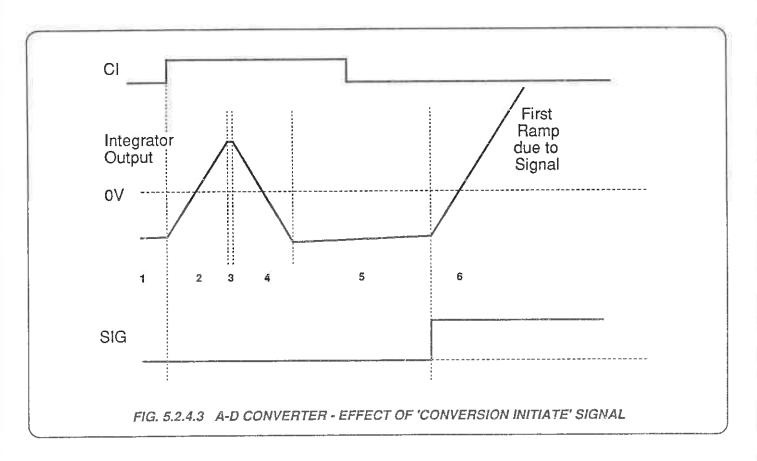

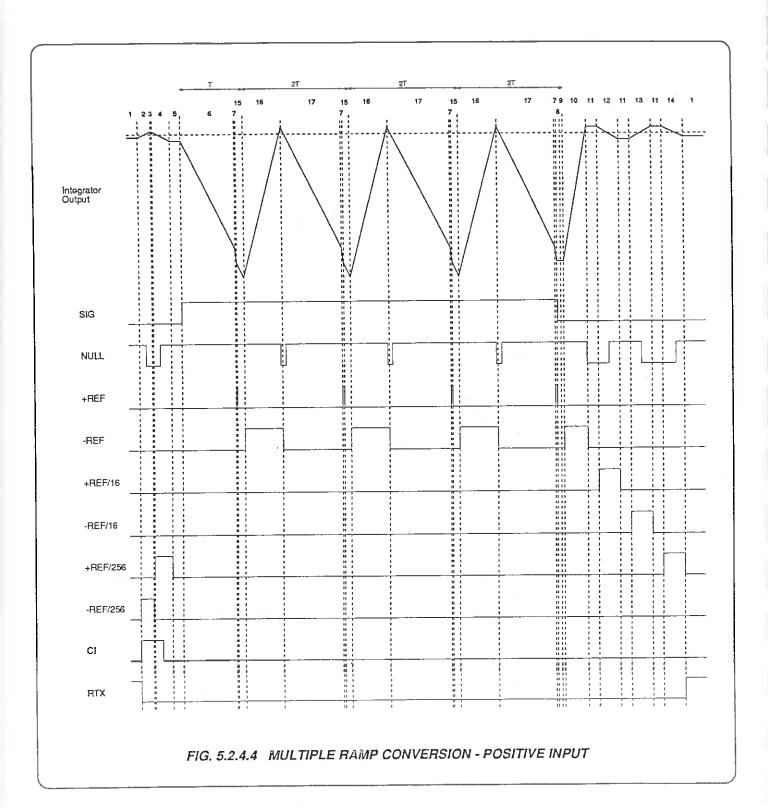

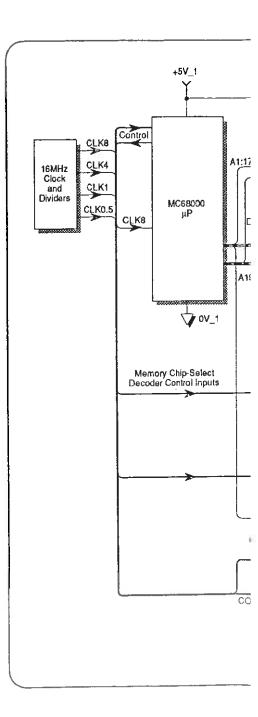

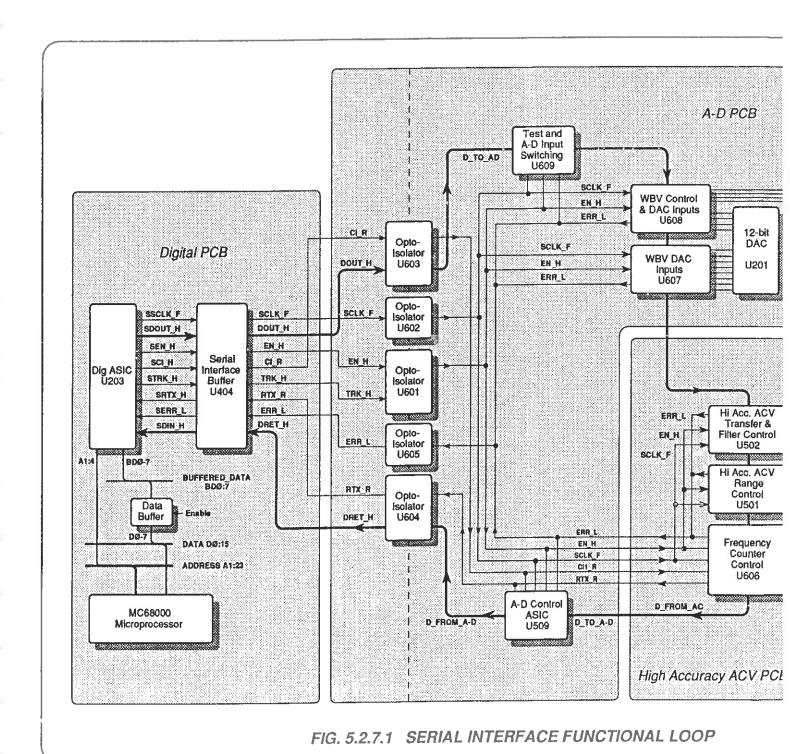

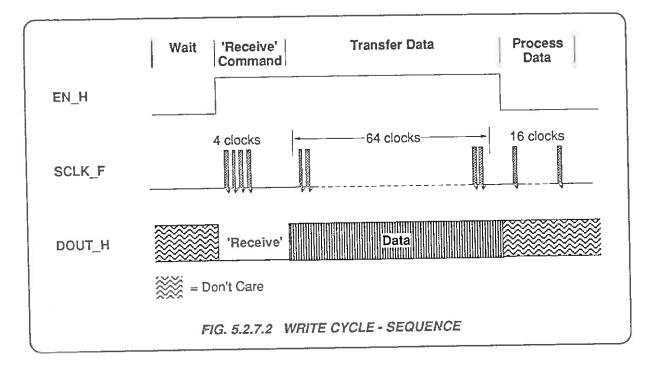

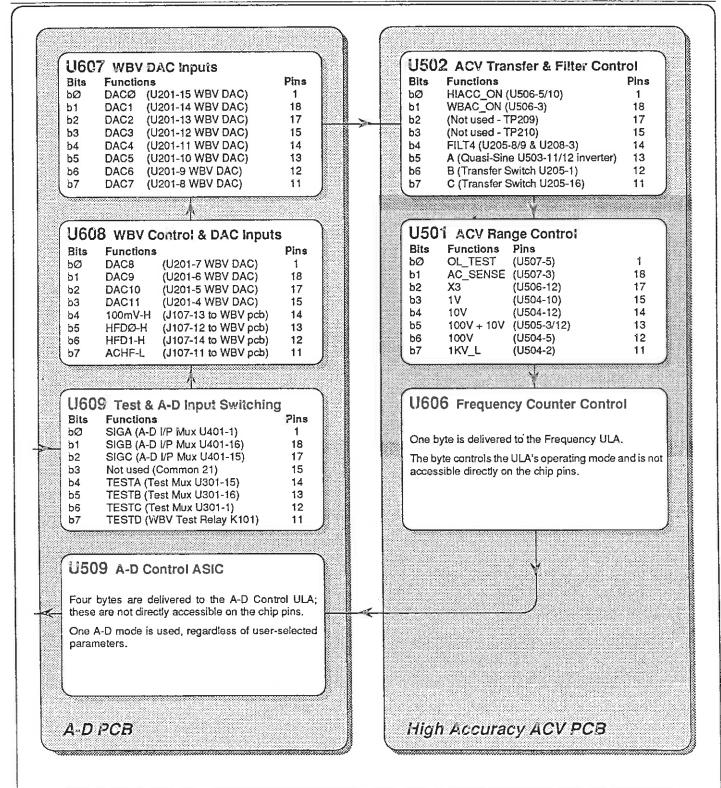

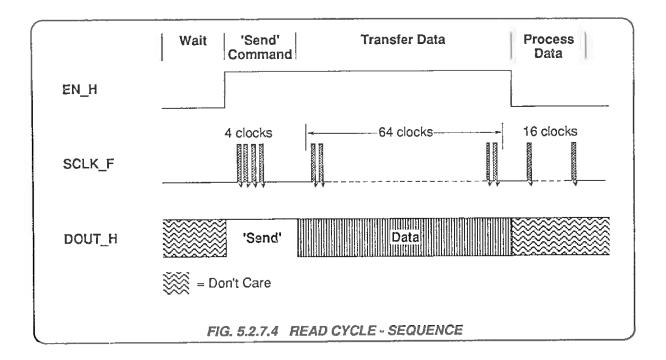

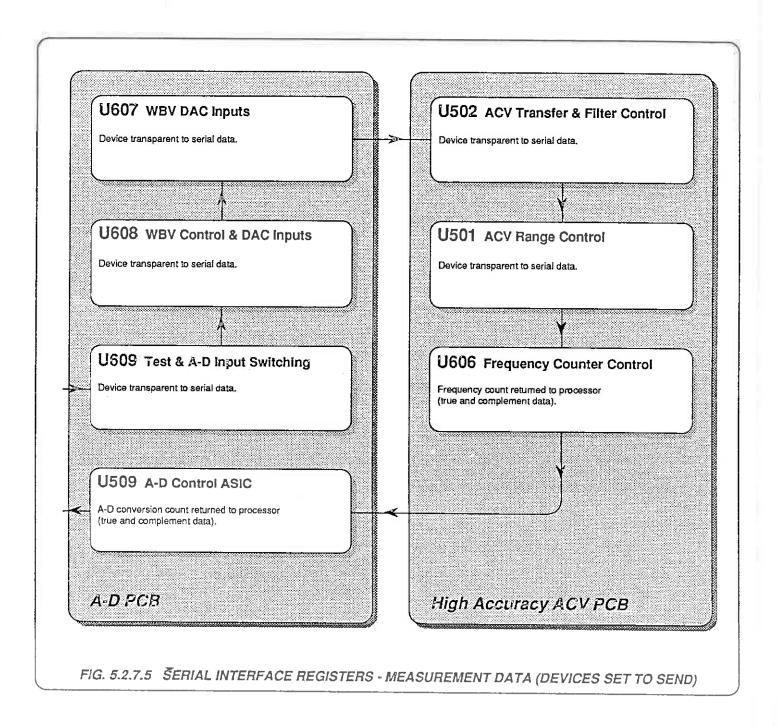

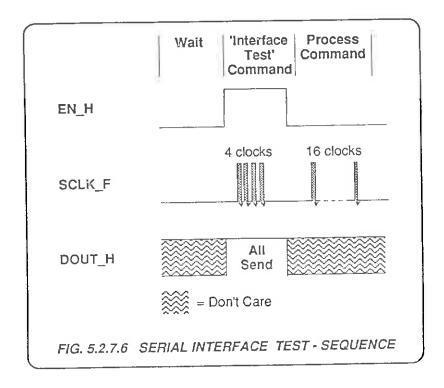

| FI     | g. 5.2.4.3  | A-D Converter - Effect of 'Conversion Initiate' Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |  |  |