#### **USER GUIDE**

# PXIe-6509

### 96-channel, 5 V TTL/CMOS, 24 mA PXI Digital I/O Module

This document contains information about using the PXIe-6509 data acquisition device with the NI-DAQmx driver software. Read the *PXIe-6509 Safety, Environmental, and Regulatory Information* document on *ni.com/manuals* before beginning.

The PXIe-6509 is a 96-bit, high-drive digital input/output (DIO) device. The PXIe-6509 features 96 TTL/CMOS-compatible digital I/O lines, 24 mA high-drive output, digital filtering, programmable power-up states, change detection, and a watchdog timer.

### Contents

| Configuration                         | 1 |

|---------------------------------------|---|

| Programming the Device in Software.   |   |

| Functional Overview                   |   |

| I/O Connector                         |   |

| Device Pinouts                        | 3 |

| Signal Descriptions.                  | 5 |

| Digital I/O                           |   |

| Static DIO on the Device              |   |

| I/O Protection                        |   |

| I/O Pull-Up/Pull-Down Resistors       |   |

| Signal Connections                    |   |

| Protecting Inductive Loads            |   |

| Sinking and Sourcing Examples.        |   |

| Power Connections                     |   |

| +5 V Power Available at I/O Connector |   |

| Industrial DIO Features               |   |

| Digital Filtering1                    |   |

| Programmable Power-Up States          |   |

| Change Detection 1                    |   |

| Watchdog Timer 1                      |   |

| Cables and Accessories1               |   |

| Related Documentation 1               |   |

# Configuration

The PXIe-6509 device is fully compliant with the *PCI Local Bus Specification Revision 2.2*, the *PXI Hardware Specification Revision 2.1*, and the *PCI Express Electromechanical Specification Revision 1.1*, respectively. The PXI Express system automatically allocates all

device resources, including the base address and interrupt level. The device base address is mapped into PCI memory space. It is not necessary to perform configuration steps after the system powers up.

Before installing the device, you must install NI-DAQmx 19.6 or later you plan to use with the device. Refer to the software documentation for configuration instructions.

After you install the software and the device, the device appears under the **Device and Interfaces** branch of the Measurement & Automation Explorer (MAX) chassis tree under Device and Interfaces.

If the does not appear in MAX, use the following troubleshooting guidelines:

- Verify that you are using the correct version of the NI-DAQmx driver software (version 19.6 or later). To download the most recent NI drivers, visit *ni.com* and select Support»Download Software»NI Drivers»NI-DAQmx.

- Press <F5> to refresh the MAX window, or close and reopen MAX.

- Restart the computer.

- Power off and unplug the computer or chassis, and install the device in a different slot. Refer to the DAQ Getting Started guides for installation instructions and safety guidelines.

## Programming the Device in Software

To use the PXIe-6509 in software, you must install NI-DAQmx 19.6 or later.

NI measurement devices are packaged with the NI-DAQmx driver software, an extensive library of functions and VIs you can call from your application software, such as LabVIEW or LabWindows<sup>TM</sup>/CVI<sup>TM</sup>, to program all the features of your NI measurement devices. NI-DAQmx provides an application programming interface (API), which is a library of VIs, functions, classes, attributes, and properties for creating applications for your device. NI-DAQmx also includes a collection of programming examples to help you get started developing an application. You can modify example code and save it in an application. You can use examples to develop a new application or add example code to an existing application. Refer to the *DAQ Getting Started* guides for more information about NI-DAQmx.

To Locate LabVIEW, LabWindows/CVI, Measurement Studio, Visual Basic, and ANSI C examples, refer to the document *NI-DAQmx Example Locations for LabVIEW and Text-Based in Windows* by going to *ni.com/r/daqmxexp*.

# **Functional Overview**

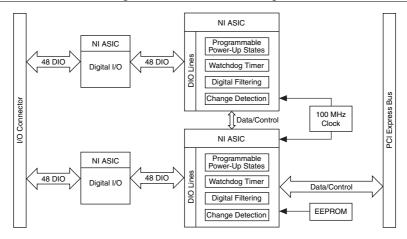

The following figure shows the key functional components of the PXIe-6509.

Figure 1. PXIe-6509 Block Diagram

### I/O Connector

**Notice** Operate this product only with shielded cables and accessories. Do not use unshielded cables or accessories unless they are installed in a shielded enclosure with properly designed and shielded input/output ports and connected to the product using a shielded cable. If unshielded cables or accessories are not properly installed and shielded, the EMC specifications for the product are no longer guaranteed.

The 100-pin high-density SCSI connector on the device front panel provides access to 96 digital inputs and outputs. Use this connector to connect to external devices, such as solid-state relays (SSRs) and LEDs. For easy connection to the digital I/O connector, use the SH100M-100M<sup>1</sup> shielded digital I/O cable with the SCB-100A connector block, or use the R1005050 ribbon cable with the CB-50 or CB-50LP connector block.

**Notice** Do not make connections to the digital I/O that exceed the maximum I/O specifications. Doing so may permanently damage the device and the computer. Refer to the PXIe-6509 Specifications on ni.com/manuals for more information about the maximum I/O specifications.

### **Device Pinouts**

#### SH100M-100M Flex Cable Pinout

The following figure shows the pinout for the PXIe-6509 using the SH100M-100M Flex cable. The naming convention for each pin is PX.Y, where X is the port (P) number, and Y is the line number or name.

Formerly known as the SH100-100-F cable.

| P2.7 |  | 1  | 51  | 1) | P8.7  |  |  |  |

|------|--|----|-----|----|-------|--|--|--|

| P5.7 |  | 2  | 52  |    | P11.7 |  |  |  |

| P2.6 |  | 3  | 53  |    | P8.6  |  |  |  |

| P5.6 |  | 4  | 54  |    | P11.6 |  |  |  |

| P2.5 |  | 5  | 55  |    | P8.5  |  |  |  |

| P5.5 |  | 6  | 56  |    | P11.5 |  |  |  |

| P2.4 |  | 7  | 57  |    | P8.4  |  |  |  |

| P5.4 |  | 8  | 58  |    | P11.4 |  |  |  |

| P2.3 |  | 9  | 59  |    | P8.3  |  |  |  |

| P5.3 |  | 10 | 60  |    | P11.3 |  |  |  |

| P2.2 |  | 11 | 61  |    | P8.2  |  |  |  |

| P5.2 |  | 12 | 62  |    | P11.2 |  |  |  |

| P2.1 |  | 13 | 63  |    | P8.1  |  |  |  |

| P5.1 |  | 14 | 64  |    | P11.1 |  |  |  |

| P2.0 |  | 15 | 65  |    | P8.0  |  |  |  |

| P5.0 |  | 16 | 66  |    | P11.0 |  |  |  |

| P1.7 |  | 17 | 67  |    | P7.7  |  |  |  |

| P4.7 |  | 18 | 68  |    | P10.7 |  |  |  |

| P1.6 |  | 19 | 69  |    | P7.6  |  |  |  |

| P4.6 |  | 20 | 70  |    | P10.6 |  |  |  |

| P1.5 |  | 21 | 71  |    | P7.5  |  |  |  |

| P4.5 |  | 22 | 72  |    | P10.5 |  |  |  |

| P1.4 |  | 23 | 73  |    | P7.4  |  |  |  |

| P4.4 |  | 24 | 74  |    | P10.4 |  |  |  |

| P1.3 |  | 25 | 75  |    | P7.3  |  |  |  |

| P4.3 |  | 26 | 76  |    | P10.3 |  |  |  |

| P1.2 |  | 27 | 77  |    | P7.2  |  |  |  |

| P4.2 |  | 28 | 78  |    | P10.2 |  |  |  |

| P1.1 |  | 29 | 79  |    | P7.1  |  |  |  |

| P4.1 |  | 30 | 80  |    | P10.1 |  |  |  |

| P1.0 |  | 31 | 81  |    | P7.0  |  |  |  |

| P4.0 |  | 32 | 82  |    | P10.0 |  |  |  |

| P0.7 |  | 33 | 83  |    | P6.7  |  |  |  |

| P3.7 |  | 34 | 84  |    | P9.7  |  |  |  |

| P0.6 |  | 35 | 85  |    | P6.6  |  |  |  |

| P3.6 |  | 36 | 86  |    | P9.6  |  |  |  |

| P0.5 |  | 37 | 87  |    | P6.5  |  |  |  |

| P3.5 |  | 38 | 88  |    | P9.5  |  |  |  |

| P0.4 |  | 39 | 89  |    | P6.4  |  |  |  |

| P3.4 |  | 40 | 90  |    | P9.4  |  |  |  |

| P0.3 |  | 41 | 91  |    | P6.3  |  |  |  |

| P3.3 |  | 42 | 92  |    | P9.3  |  |  |  |

| P0.2 |  | 43 | 93  |    | P6.2  |  |  |  |

| P3.2 |  | 44 | 94  |    | P9.2  |  |  |  |

| P0.1 |  | 45 | 95  |    | P6.1  |  |  |  |

| P3.1 |  | 46 | 96  |    | P9.1  |  |  |  |

| P0.0 |  | 47 | 97  |    | P6.0  |  |  |  |

| P3.0 |  | 48 | 98  |    | P9.0  |  |  |  |

| +5 V |  | 49 | 99  |    | +5 V  |  |  |  |

| GND  |  | 50 | 100 | IJ | GND   |  |  |  |

|      |  | _  | _   | _  |       |  |  |  |

#### R1005050 Pinout

The following figure shows the pinout for the PXIe-6509 using the R1005050 cable. The naming convention for each pin is PX.Y, where X is the port (P) number, and Y is the line number or name.

Figure 3. R1005050 Connector Pinout

| Positio | ns 1 | thro | ugh 50 | F | Position | s 51 | thro | ugh 100 |

|---------|------|------|--------|---|----------|------|------|---------|

| P2.7    | 1    | 2    | P5.7   |   | P8.7     | 1    | 2    | P11.7   |

| P2.6    | 3    | 4    | P5.6   |   | P8.6     | 3    | 4    | P11.6   |

| P2.5    | 5    | 6    | P5.5   |   | P8.5     | 5    | 6    | P11.5   |

| P2.4    | 7    | 8    | P5.4   |   | P8.4     | 7    | 8    | P11.4   |

| P2.3    | 9    | 10   | P5.3   |   | P8.3     | 9    | 10   | P11.3   |

| P2.2    | 11   | 12   | P5.2   |   | P8.2     | 11   | 12   | P11.2   |

| P2.1    | 13   | 14   | P5.1   |   | P8.1     | 13   | 14   | P11.1   |

| P2.0    | 15   | 16   | P5.0   |   | P8.0     | 15   | 16   | P11.0   |

| P1.7    | 17   | 18   | P4.7   |   | P7.7     | 17   | 18   | P10.7   |

| P1.6    | 19   | 20   | P4.6   |   | P7.6     | 19   | 20   | P10.6   |

| P1.5    | 21   | 22   | P4.5   |   | P7.5     | 21   | 22   | P10.5   |

| P1.4    | 23   | 24   | P4.4   |   | P7.4     | 23   | 24   | P10.4   |

| P1.3    | 25   | 26   | P4.3   |   | P7.3     | 25   | 26   | P10.3   |

| P1.2    | 27   | 28   | P4.2   |   | P7.2     | 27   | 28   | P10.2   |

| P1.1    | 29   | 30   | P4.1   |   | P7.1     | 29   | 30   | P10.1   |

| P1.0    | 31   | 32   | P4.0   |   | P7.0     | 31   | 32   | P10.0   |

| P0.7    | 33   | 34   | P3.7   |   | P6.7     | 33   | 34   | P9.7    |

| P0.6    | 35   | 36   | P3.6   |   | P6.6     | 35   | 36   | P9.6    |

| P0.5    | 37   | 38   | P3.5   |   | P6.5     | 37   | 38   | P9.5    |

| P0.4    | 39   | 40   | P3.4   |   | P6.4     | 39   | 40   | P9.4    |

| P0.3    | 41   | 42   | P3.3   |   | P6.3     | 41   | 42   | P9.3    |

| P0.2    | 43   | 44   | P3.2   |   | P6.2     | 43   | 44   | P9.2    |

| P0.1    | 45   | 46   | P3.1   |   | P6.1     | 45   | 46   | P9.1    |

| P0.0    | 47   | 48   | P3.0   |   | P6.0     | 47   | 48   | P9.0    |

| +5 V    | 49   | 50   | GND    |   | +5 V     | 49   | 50   | GND     |

# Signal Descriptions

The following table lists the signal and descriptions for all signals available on the PXIe-6509 device.

Table 1. PXIe-6509 Signal Descriptions

| Pin                               | Signal Name | Description                          | MSB  | LSB  |

|-----------------------------------|-------------|--------------------------------------|------|------|

| 1, 3, 5, 7, 9, 11, 13, 15         | P2.<70>     | Bi-directional data lines for port 2 | P2.7 | P2.0 |

| 2, 4, 6, 8, 10, 12, 14, 16        | P5.<70>     | Bi-directional data lines for port 5 | P5.7 | P5.0 |

| 17, 19, 21, 23, 25, 27, 29,<br>31 | P1.<70>     | Bi-directional data lines for port 1 | P1.7 | P1.0 |

Table 1. PXIe-6509 Signal Descriptions (Continued)

| Pin                               | Signal Name | Description                                     | MSB   | LSB   |

|-----------------------------------|-------------|-------------------------------------------------|-------|-------|

| 18, 20, 22, 24, 26, 28, 30, 32    | P4.<70>     | Bi-directional data lines for port 4            | P4.7  | P4.0  |

| 33, 35, 37, 39, 41, 43, 45,<br>47 | P0.<70>     | Bi-directional data lines for port 0            | P0.7  | P0.0  |

| 34, 36, 38, 40, 42, 44, 46,<br>48 | P3.<70>     | Bi-directional data lines for port 3            | P3.7  | P3.0  |

| 49, 99                            | +5 V supply | +5 volts; provide +5 V power source             | _     | _     |

| 50, 100                           | GND         | Ground; connected to the computer ground signal | _     | _     |

| 51, 53, 55, 57, 59, 61, 63,<br>65 | P8.<70>     | Bi-directional data lines for port 8            | P8.7  | P8.0  |

| 52, 54, 56, 58, 60, 62, 64,<br>66 | P11.<70>    | Bi-directional data lines for port 11           | P11.7 | P11.0 |

| 67, 69, 71, 73, 75, 77, 79,<br>81 | P7.<70>     | Bi-directional data lines for port 7            | P7.7  | P7.0  |

| 68, 70, 72, 74, 76, 78, 80,<br>82 | P10.<70>    | Bi-directional data lines for port 10           | P10.7 | P10.0 |

| 83, 85, 87, 89, 91, 93, 95,<br>97 | P6.<70>     | Bi-directional data lines for port 6            |       | P6.0  |

| 84, 86, 88, 90, 92, 94, 96,<br>98 | P9.<70>     | Bi-directional data lines for port 9            | P9.7  | P9.0  |

# Digital I/O

#### Static DIO on the Device

$\textbf{Note} \quad \text{The PXIe-6509 can be configured for DI and DO on a line-by-line basis}.$

The PXIe-6509 provides 96 lines of bi-directional DIO signals, P<0..11>.<0..7>. You can configure the PXIe-6509 for digital input (DI) and digital output (DO) on a line-by-line basis and use each of the DIO lines as a static DI or DO line. All samples of DI lines and updates of DO lines are software-timed.

#### I/O Protection

You should avoid electrostatic discharge (ESD) events and overvoltage, undervoltage, and overcurrent fault conditions by using the following guidelines:

- If you configure a DIO line as an output, do not connect it to any external signal source, ground signal, or power supply.

- If you configure a DIO line as an output, understand the current requirements of the load

connected to these signals. Do not exceed the specified current output limits of the DAQ

device. NI has several signal conditioning solutions for digital applications requiring high

current drive

- If you configure a DIO line as an input, do not drive the line with voltages outside of its normal operating range.

- Treat the DAQ device as you would any static sensitive device. Always properly ground yourself and the equipment when handling the DAQ device or connecting to it.

# I/O Pull-Up/Pull-Down Resistors

The PXIe-6509 has user-configurable pull-up and pull-down resistors. The DIO lines on the PXIe-6509 are connected to an NI ASCI that contains a weak pull-down resistor (47 k $\Omega$ , typical), and each DIO line is connected to a software-selectable strong pull-up resistor (4.7 k $\Omega$ , typical), as the following figure shows.

Software Controlled • 4.7 kΩ, typical

NI ASIC

I/O Protection

O Digital I/O Line

GND

Figure 4. PXIe-6509 Digital I/O Circuitry

If you set the software to pull-down, the weak pull-down resistor in the NI ASIC pulls the DIO line low. If you set the software to pull-up, the strong pull-up resistor pulls the DIO line high. You can set the pull setting regardless of the I/O direction, but it affects only the state of DIO lines that are configured for input.

To use MAX to configure the I/O pull resistor, select the device and click the **Properties** button. Refer to the software documentation for information about how to program the pull setting using NI-DAQmx with LabVIEW or other NI application development environments (ADEs).

# **Signal Connections**

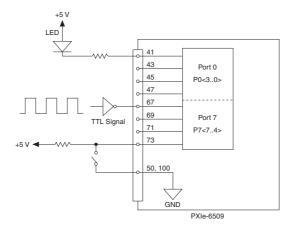

The following figure shows an example of signal connections for three typical digital I/O applications. Port 0 is configured for digital output, and port 7 is configured for digital input.

Figure 5. PXIe-6509 Signal Connections

Digital output applications include sending TTL signals and driving external devices such as the LED shown in the figure above. Digital input applications include receiving TTL signals and sensing external device states such as the state of the switch in the figure above.

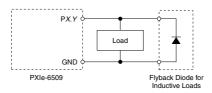

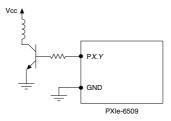

# Protecting Inductive Loads

When inductive loads are connected to output lines, a large counter-electromotive force may occur at switching time because of the energy stored in the inductive load. These flyback voltages can damage the outputs and/or the power supply.

To limit these flyback voltages at the inductive load, install a flyback diode across the inductive load. For best results, mount the flyback diode within 18 inches of the load. The following figure shows an example of using an external flyback diode to protect inductive loads.

Figure 6. Limiting Flyback Voltages at the Inductive Load

# Sinking and Sourcing Examples

The following sections provide examples of driving a relay with no more than 24 mA, driving a relay with more than 24 mA, and driving a solid-state relay (SSR).

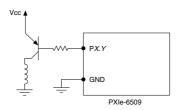

#### Driving a Relay ≤ 24 mA

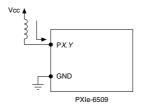

The following figures show examples of connecting the PXIe-6509 to a relay that does not require more than 24 mA of current.

Figure 7. PXIe-6509 Sinking Connection Example, ≤ 24 mA

Figure 8. PXIe-6509 Sourcing Connection Example, ≤ 24 mA

## Driving a Relay > 24 mA

The following figures are examples of connecting the PXIe-6509 to a relay that requires more than 24 mA of current. These examples use an additional transistor circuit.

Figure 9. PXIe-6509 Sinking Connection Example, > 24 mA

Figure 10. PXIe-6509 Sourcing Connection Example, > 24 mA

### Driving an SSR

The following figure shows an example of connecting the PXIe-6509 to an SSR.

Figure 11. PXIe-6509 SSR Connection Example

### **Power Connections**

### +5 V Power Available at I/O Connector

Pins 49 and 99 supply +5 V power to the I/O connector. The I/O connector power has a fuse for overcurrent protection. This fuse is not customer replaceable. If the fuse is blown, return the device to NI for repair.

**Notice** Do *not* connect the +5 V power pin directly to ground or any other voltage source on any other device. Doing so may permanently damage the PXIe-6509 and the computer.

# Industrial DIO Features

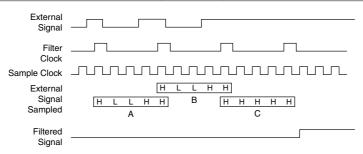

# Digital Filtering

Use the digital filter option available on the PXIe-6509 input lines to eliminate glitches on input data. When used with change detection, filtering can also reduce the number of changes to examine and process.

You can configure the digital input channels to pass through a digital filter, and you can control the timing interval the filter uses. The filter blocks pulses that are shorter than half of the specified timing interval and passes pulses that are longer than the specified interval.

Intermediate-length pulses-pulses longer than half of the interval but less than the interval-may or may not pass the filter.

The following table lists the pulse widths guaranteed to be passed and blocked.

Table 2. PXIe-6509 Digital Filtering

| Filter Setting                           | Pulse Width Guaranteed to<br>Pass Filter | Pulse Width Guaranteed to Not<br>Pass Filter |

|------------------------------------------|------------------------------------------|----------------------------------------------|

| 200 ns <t<sub>interval&lt;200 ms</t<sub> | t <sub>interval</sub>                    | t <sub>interval</sub> /2                     |

You can enable digital filtering on as many input lines as necessary for your application. The PXIe-6509 supports three timing intervals: 160 ns,  $10.24 \mu \text{s}$ , and 5.12 ms.

Internally, the digital filter uses two clocks: a sample clock and a filter clock. The filter clock is generated by a counter and has a period equal to one half of the specified timing interval. The device samples the input signal on each rising edge of the sample clock, but the device recognizes a change in the input signal only if the input signal maintains its new state for at least two consecutive rising edges of the filter clock. The filter clock is programmable and allows you to control how long a pulse must last to be recognized by the device.

### Digital Filtering Example

The following figure shows an example of digital filtering.

Figure 12. Digital Filtering Example

In periods of A and B, the filter blocks the glitches because the external signal does not remain steadily high from one rising edge of the filter clock to the next. In period C, the filter passes the transition, because the external signal remains steadily high. Depending on when the transition occurs, the filter may require up to two filter clocks—one full filter interval—to pass a transition. The figure shows a rising (0 to 1) transition. The same filtering applies to falling (1 to 0) transitions.

# Programmable Power-Up States

You can program the DIO lines on the device to power up at a predefined state: input, high output, or low output. Programmable power-up states ensure that the device powers up in a known state

**Note** The DIO lines on the device can be pulled high or low. For more information, refer to the *I/O Pull-Up/Pull-Down Resistors* section.

The typical response time of programmable power-up states is 500 ms.

To use MAX (recommended) to program the power-up states, select the device and click the **Properties** button. Refer to the software documentation for information about how to program the power-up states using NI-DAQmx with LabVIEW or other NI application development environments (ADEs).

# Change Detection

You can program the PXIe-6509 to send an interrupt when a change occurs on any input line. The PXIe-6509 can monitor changes on selected input lines or on all input lines. It can monitor for rising edges (0 to 1), falling edges (1 to 0), or both.

When an input change occurs, the PXIe-6509 generates an interrupt and notifies the software. However, the PXIe-6509 does not report which line changed or if the line was rising or falling. After a change, you can read the input lines to determine the current line states. The rate of change detection is determined by the software response time, which varies from system to system.

**Note** Excessive change detections may affect system performance. Use digital filtering to minimize the effects of noisy input lines.

An overflow bit indicates that the PXIe-6509 detects an additional rising or falling edge before the software processes the previous change.

Refer to the software documentation for information about how to set up and implement the change detection feature.

### Change Detection Example

The following table shows a change detection example for six bits of one port.

|                               | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|-------------------------------|----------|----------|----------|----------|-------|-------|-------|----------|

| Changes to detect             | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | _     | _     | 1     | <b>1</b> |

| Enable rising-edge detection  | yes      | yes      | yes      | yes      | no    | no    | yes   | no       |

| Enable falling-edge detection | yes      | yes      | yes      | yes      | no    | no    | no    | yes      |

Table 3. Change Detection Example

This example assumes the following line connections:

- Bits 7, 6, 5, and 4 are connected to data lines from a four-bit TTL output device. The PXIe-6509 detects any change in the input data so you can read the new data value.

- Bit 1 is connected to a limit sensor. The PXIe-6509 detects rising edges on the sensor, which correspond to over-limit conditions.

- Bit 0 is connected to a switch. The PXIe-6509 can react to any switch closure, which is represented by a falling edge. If the switch closure is noisy, enable digital filtering for this

In this example, the PXIe-6509 reports rising edges only on bit 1, falling edges only on bit 0, and rising and falling edges on bits 7, 6, 5, and 4. The PXIe-6509 reports no changes for bits 3 and 2. After receiving notification of a change, you can read the port to determine the current values of all eight lines. However, you cannot read the state of any lines that are configured for change detection until the change detection interrupt occurs.

# Watchdog Timer

The watchdog timer is a software-configurable feature used to set critical outputs to safe states in the event of a software failure, a system crash, or any other loss of communication between the application and the PXIe-6509.

After you enable the watchdog timer, if the PXIe-6509 does not receive a watchdog reset software command within the time specified for the watchdog timer, the output lines enter a user-defined safe state and remain in that state until one of the following events occurs:

- The application disarms the watchdog timer and writes new values to the output lines.

- The PXIe-6509 is reset.

- The computer is restarted.

The signal indicating an expired watchdog asserts continuously until the application disarms the watchdog timer. After the watchdog timer expires, the PXIe-6509 ignores any writes until the application disarms the watchdog timer.

**Note** On the PXIe-6509, ports that are set to tristate cannot enter safe states of output when the computer enters a fault condition.

You can set the watch timer timeout period to specify the amount of time that elapses before the watchdog timer expires. The counter on the watchdog timer is configurable up to  $(2^{32} - 1) \times 8$  ns (about 34 seconds).

# Cables and Accessories

**Notice** Operate this product only with shielded cables and accessories. Do not use unshielded cables or accessories unless they are installed in a shielded enclosure with properly designed and shielded input/output ports and connected to the product using a shielded cable. If unshielded cables or accessories are not properly installed and shielded, the EMC specifications for the product are no longer guaranteed.

NI offers the following products for use with the PXIe-6509.

Table 4. Connectivity Options

| Cable (Part Number)                                      | Accessory (Part Number)                           |

|----------------------------------------------------------|---------------------------------------------------|

| SH100M-100M Flex <sup>2</sup> shielded cable (185095-xx) | SCB-100A connector block (785024-01)              |

| R1005050 ribbon cable (182762-xx)                        | CB-50 connector block, DIN-rail mount (776164-90) |

|                                                          | CB-50LP connector block, panel mount (777101-01)  |

For more information about optional equipment available from NI, refer to *ni.com*.

### **Related Documentation**

The following documents contain information that you may find helpful as you use this user guide:

- DAQ Getting Started guides—These guides describe how to install the NI-DAQmx driver software, the DAQ device, and how to confirm that the device is working properly.

- NI-DAQmx Help—This help file contains information about using NI-DAQmx to program NI devices. NI-DAQmx is the software you use to communicate with and control National Instruments DAQ devices.

- NI MAX Help for NI-DAQmx—This help file contains information about configuring and testing DAQ devices using MAX for NI-DAQmx, and information about special considerations for operating systems.

- DAQ Assistant Help—This help file contains information about creating and configuring channels, tasks, and scales using DAQ Assistant.

- PXIe-6509 Specifications—This document contains the specifications and pinouts for the PXIe-6509 device.

- PXIe-6509 Safety, Environmental, and Regulatory Information—This document contains safety, environmental, and regulatory information for the PXIe-6509.

**Note** You can download these documents from *ni.com/manuals*.

Information is subject to change without notice. Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the National Instruments Patent Notice at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the Export Compliance Information at ni.com/legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015.

© 2020 National Instruments. All rights reserved.

<sup>&</sup>lt;sup>2</sup> Formerly known as the SH100-100-F cable.