## Service Guide

Agilent Technologies 8561E/EC and 8563E/EC Spectrum Analyzers

Part Number: 08563-90214 Printed in USA March 2001 Supersedes: December 1999

© Copyright 1990 – 1999, 2001 Agilent Technologies, Inc.

## Notice

Agilent Technologies makes no warranty of any kind with regard to this material, including but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

All Rights Reserved. Reproduction, adaptation, or translation without prior written permission is prohibited, except as allowed under the copyright laws.

The information contained in this document is subject to change without notice.

## Certification

Agilent Technologies certifies that this product met its published specifications at the time of shipment from the factory. Agilent further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology, to the extent allowed by the Institute's calibration facility, and to the calibration facilities of other International Standards Organization members.

## **General Safety Considerations**

The following safety notes are used throughout this manual. Familiarize yourself with these notes before operating this instrument.

WARNING Warning denotes a hazard. It calls attention to a procedure which, if not correctly performed or adhered to, could result in injury or loss of life. Do not proceed beyond a warning note until the indicated conditions are fully understood and met.

CAUTION

Always use the three-prong AC power cord supplied with this product.

Failure to ensure adequate grounding may cause product damage.

| WARNING | No operator serviceable parts inside. Refer servicing to qualified personnel. To prevent electrical shock do not remove covers.                                                                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAUTION | Caution denotes a hazard. It calls attention to a procedure that, if not<br>correctly performed or adhered to, could result in damage to or<br>destruction of the instrument. Do not proceed beyond a caution sign<br>until the indicated conditions are fully understood and met.                                                                                                         |

| WARNING | This is a Safety Class 1 Product (provided with a protective<br>earth ground incorporated in the power cord). The mains plug<br>shall be inserted only in a socket outlet provided with a<br>protected earth contact. Any interruption of the protective<br>conductor inside or outside of the product is likely to make the<br>product dangerous. Intentional interruption is prohibited. |

| WARNING | Before this instrument is switched on, make sure it has been<br>properly grounded through the protective conductor of the ac<br>power cable to a socket outlet provided with protective earth<br>contact.                                                                                                                                                                                  |

|         | Any interruption of the protective (grounding) conductor,<br>inside or outside the instrument, or disconnection of the<br>protective earth terminal can result in personal injury.                                                                                                                                                                                                         |

|         | If this instrument is used in a manner not specified by Agilent<br>Technologies , the protection provided by the instrument may<br>be impaired.                                                                                                                                                                                                                                            |

|         | There are many points in the instrument which can, if<br>contacted, cause personal injury. Be extremely careful. Any<br>adjustments or service procedures that require operation of the<br>instrument with protective covers removed should be<br>performed only by trained service personnel.                                                                                             |

| CAUTION | Before this instrument is switched on, make sure its primary power circuitry has been adapted to the voltage of the ac power source.                                                                                                                                                                                                                                                       |

|         | Failure to set the ac power input to the correct voltage could cause damage to the instrument when the ac power cable is plugged in.                                                                                                                                                                                                                                                       |

|         | This product conforms to Enclosure Protection IP 2 0 according to IEC-529. The enclosure protects against finger access to hazardous parts within the enclosure; the enclosure does not protect against the entrance of water.                                                                                                                                                             |

### Warranty

This Agilent Technologies instrument product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Agilent Technologies will, at its option, either repair or replace products that prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Agilent Technologies. Buyer shall prepay shipping charges to Agilent and Agilent shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Agilent Technologies from another country.

Agilent Technologies warrants that its software and firmware designated by Agilent for use with an instrument will execute its programming instructions when properly installed on that instrument. Agilent Technologies does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error-free.

## LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. AGILENT TECHNOLOGIES SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. AGILENT TECHNOLOGIES SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### 1. General Information

| Introduction                                                       | . 26 |

|--------------------------------------------------------------------|------|

| How to Use this Guide                                              | 26   |

| Conventions used in this guide                                     | 26   |

| Documentation Outline.                                             | . 27 |

| Differences between 8560 EC-Series and E-Series Spectrum Analyzers | . 28 |

| Instrument Variations                                              | . 29 |

| Serial Numbers and Repair Information                              | 30   |

| Agilent 85629B Test and Adjustment Module                          |      |

| Service Kit                                                        |      |

| Electrostatic Discharge                                            | . 34 |

| Reducing Potential for ESD Damage                                  |      |

| Static-Safe Accessories                                            | . 35 |

| Returning Instruments for Service                                  | . 36 |

| Service Tag                                                        | . 36 |

| Original Packaging                                                 | . 36 |

| Other Packaging                                                    | . 36 |

| Recommended Test Equipment                                         | . 38 |

| Sales and Service Offices                                          | 45   |

#### 2. Adjustment Procedures

| Introduction                                              |

|-----------------------------------------------------------|

| Safety Considerations                                     |

| Which Adjustments Should Be Performed? 49                 |

| Test Equipment                                            |

| Adjustable and Factory-Selected Components                |

| Adjustment Tools                                          |

| Instrument Service Position                               |

| Using the TAM                                             |

| Test Equipment                                            |

| Adjustment Indicator                                      |

| 1. High Voltage Power Supply Adjustment (8561E and 8563E) |

| Assembly Adjusted                                         |

| Related Performance Test                                  |

| Description                                               |

| Equipment                                                 |

| Procedure                                                 |

| 2. Display Adjustment (8561E and 8563E) 62                |

| Assembly Adjusted                                         |

| Related Performance Test                                  |

| Description                                               |

| Equipment                                                 |

| Procedure                                                 |

| Preliminary Adjustments                                   |

| Cutoff Adjustment                                         |

| Deflection Adjustments                                    |

| Intensity Adjustments                                     |

| Fast Zero Span Adjustments    66                          |

| 3. IF Bandpass Adjustment                                 |

| Assembly Adjusted                                  | 68 |

|----------------------------------------------------|----|

| Related Performance Test                           |    |

| Description                                        |    |

| Equipment                                          |    |

| Procedure                                          |    |

| LC Bandpass Adjustments                            |    |

| XTAL Bandpass Adjustments                          |    |

| 4. IF Amplitude Adjustments                        |    |

| Assembly Adjusted                                  |    |

| Related Performance Tests                          |    |

| Description                                        |    |

| Equipment                                          |    |

| Procedure                                          |    |

| A5 Reference Attenuator Adjustment                 |    |

| A5 Adjustment Verification                         |    |

| 5. DC Log Amplifier Adjustments                    |    |

| Assembly Adjusted                                  |    |

| Related Performance Tests                          |    |

|                                                    |    |

| Description                                        |    |

| Equipment                                          |    |

| A4 Limiter Phase Adjustment                        |    |

| A4 Linear Fidelity Adjustment                      |    |

| A4 LOG Fidelity Adjustment                         |    |

| 6. Sampling Oscillator Adjustment                  |    |

| Assembly Adjusted                                  |    |

| Related Performance Test                           |    |

| Description                                        |    |

| Equipment                                          |    |

| Procedure                                          |    |

| Sampling Oscillator Adjustment                     |    |

| Sampler Match Adjustment                           |    |

| 7. YTO Adjustment                                  |    |

| Assembly Adjusted                                  |    |

| Related Performance Tests                          |    |

| Description                                        |    |

| Equipment                                          |    |

| Procedure                                          |    |

| YTO Main Coil Adjustments                          |    |

| YTO FM Coil Adjustments                            | 86 |

| 8. LO Distribution Amplifier Adjustment (8561E/EC) |    |

| Assembly Adjusted                                  |    |

| Related Performance Test                           |    |

| Description                                        |    |

| Equipment                                          |    |

| Procedure                                          |    |

| 9. LO Distribution Amplifier Adjustment (8563E/EC) |    |

| Assembly Adjusted                                  |    |

| Related Performance Test                           | 90 |

| Description                                        | 90 |

| Device set                                          | 00  |

|-----------------------------------------------------|-----|

| Equipment                                           |     |

| 10. Dual Band Mixer Bias Adjustment (8561E/EC)      |     |

|                                                     |     |

| Assembly Adjusted                                   |     |

| Related Performance Test                            |     |

| Description                                         |     |

| Equipment                                           |     |

| Procedure                                           |     |

| 11. Frequency Response Adjustment (8561E/EC)        |     |

| Assembly Adjusted                                   |     |

| Related Performance Tests                           |     |

| Description                                         |     |

| Equipment                                           |     |

| Procedure                                           |     |

| 12. Frequency Response Adjustment (8563E/EC)        |     |

| Assembly Adjusted                                   |     |

| Related Performance Tests                           |     |

| Description                                         |     |

| Equipment                                           | 100 |

| Procedure                                           |     |

| 13. Calibrator Amplitude Adjustment                 |     |

| Assembly Adjusted                                   |     |

| Related Performance Test                            | 104 |

| Description                                         | 104 |

| Equipment                                           | 104 |

| Procedure                                           | 104 |

| 14. 10 MHz Reference Adjustment — OCXO              | 106 |

| Assembly Adjusted                                   |     |

| Related Performance Test                            |     |

| Description                                         |     |

| Equipment                                           |     |

| Procedure                                           |     |

| 15. 10 MHz Reference Adjustment — TCXO (Option 103) |     |

| Assembly Adjusted                                   |     |

| Related Performance Test                            |     |

| Description                                         |     |

| Equipment                                           |     |

| Procedure                                           |     |

| 16. Demodulator Adjustment                          |     |

| Assembly Adjusted                                   |     |

| Related Performance Test                            |     |

| Description                                         |     |

| Equipment                                           |     |

| Procedure                                           |     |

| 17. External Mixer Bias Adjustment                  |     |

|                                                     |     |

| Assembly Adjusted                                   |     |

| Related Performance Test                            |     |

| Description                                         |     |

| Equipment                                           | 114 |

| Procedure                                                        |     |

|------------------------------------------------------------------|-----|

| 18. External Mixer Amplitude Adjustment                          |     |

| Assembly Adjusted                                                |     |

| Related Performance Test                                         |     |

| Description                                                      |     |

| Equipment                                                        |     |

| Procedure                                                        |     |

| 19. Signal ID Oscillator Adjustment                              |     |

| Assembly Adjusted                                                |     |

| Related Performance Test                                         |     |

| Description                                                      |     |

| Equipment                                                        |     |

| Procedure                                                        |     |

| 20. Switched YIG-Tuned Filter (SYTF) Adjustment (8561E/EC)       |     |

| Assembly Adjusted                                                |     |

| Related Performance Test                                         |     |

| Description                                                      |     |

| Equipment                                                        |     |

| Procedure                                                        |     |

| 21. YIG-Tuned Filter/Mixer (RYTHM) Adjustment (8563E/EC)         | 125 |

| Assembly Adjusted                                                |     |

| Related Performance Tests                                        | 125 |

| Description                                                      | 125 |

| Equipment                                                        | 125 |

| Procedure                                                        |     |

| 22. 16 MHz PLL Adjustment                                        |     |

| Assembly Adjusted                                                |     |

| Related Performance Tests                                        |     |

| Description                                                      |     |

| Equipment                                                        |     |

| Procedure                                                        |     |

| 23. 600 MHz Reference Adjustment (serial prefix 3406A and above) | 132 |

| Assembly Adjusted                                                | 132 |

| Related Performance Test                                         | 132 |

| Description                                                      | 132 |

| Equipment                                                        | 132 |

| Procedure                                                        | 132 |

|                                                                  |     |

|                                                                  |     |

### 2a. Manual Adjustment Procedures: 3335A Source Not Available

| What You'll Find in This Chapter   | 134 |

|------------------------------------|-----|

| Required Test Equipment            | 135 |

| 4a. IF Amplitude Adjustments       | 136 |

| Assembly Adjusted                  | 136 |

| Related Performance Tests          | 136 |

| Description                        | 136 |

| Equipment                          | 137 |

| Procedure                          | 137 |

| A5 Reference Attenuator Adjustment | 139 |

| A5 Adjustment Verification         | 139 |

|                                    |     |

**3.**

| 5a. DC Log Amplifier Adjustments                                 |     |

|------------------------------------------------------------------|-----|

| Assembly Adjusted                                                |     |

| Related Performance Tests                                        | 141 |

| Description                                                      |     |

| Equipment                                                        | 142 |

| A4 Limiter Phase Adjustment                                      | 142 |

| A4 Linear Fidelity Adjustment                                    | 143 |

| A4 LOG Fidelity Adjustment                                       | 144 |

|                                                                  |     |

| Assembly Replacement                                             |     |

| Introduction                                                     | 148 |

| Access to Internal Assemblies                                    |     |

| Cable Color Code                                                 | 150 |

| Procedure 1. Spectrum Analyzer Cover                             | 151 |

| Removal/Replacement                                              |     |

| Procedure 2A. A1 Front Frame/A18 LCD (8561EC and 8563EC)         |     |

| Removal of the Front Frame.                                      | 152 |

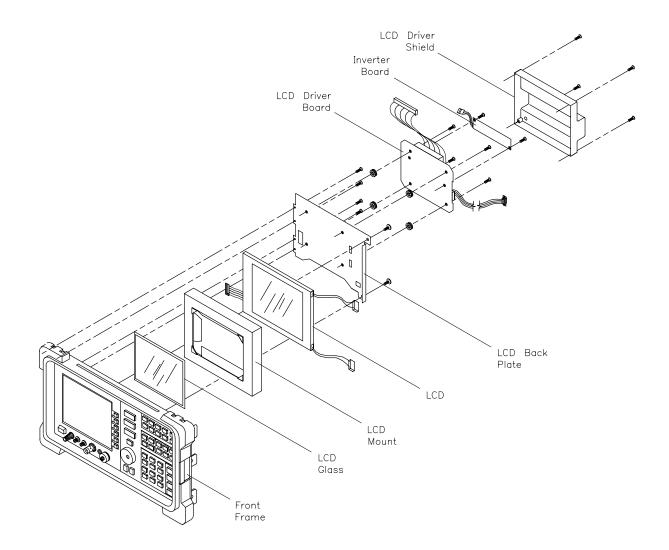

| Removal of the Display Driver Board, Inverter Board, and LCD     | 154 |

| Removal of the Backlights                                        |     |

| Removal of the Line Switch from the Front Panel                  |     |

| Removal of the Keyboard                                          | 157 |

| Replacement of the Front Frame                                   |     |

| Replacement of the Display Driver Board, Inverter Board, and LCD |     |

| Replacing the Backlights                                         | 160 |

| Replacement of the Line Switch                                   | 161 |

| Replacement of the Keyboard                                      | 161 |

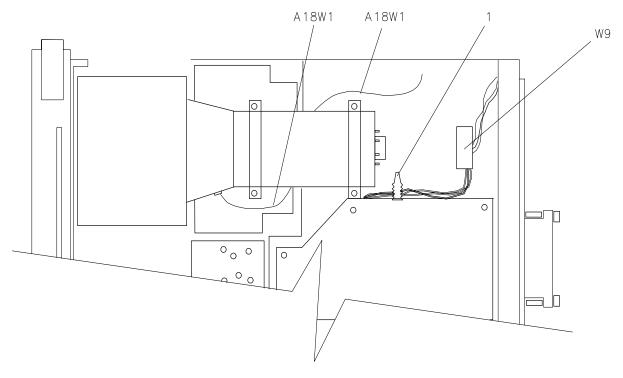

| Procedure 2B. A1 Front Frame/A18 CRT Display (8561E and 8563E)   | 162 |

| Removal                                                          |     |

| Replacement                                                      | 167 |

| Procedure 3. A1A1 Keyboard/Front Panel Keys                      | 170 |

| Removal                                                          | 170 |

| Replacement                                                      | 170 |

| Procedure 4. A1A2 RPG                                            | 171 |

| Removal                                                          | 171 |

| Replacement                                                      |     |

| Procedure 5. A2, A3, A4, and A5 Assemblies                       |     |

| Removal                                                          | 172 |

| Replacement                                                      |     |

| Procedure 6A. A6 Power Supply Assembly (8561EC and 8563EC)       |     |

| Removal                                                          |     |

| Replacement                                                      |     |

| Procedure 6B. A6 Power Supply Assembly (8561E and 8563E)         |     |

| Removal                                                          |     |

| Replacement                                                      |     |

| Procedure 7. A6A1 High Voltage Assembly (8561E and 8563E)        |     |

| Removal                                                          |     |

| Replacement                                                      |     |

| Procedure 8. A7 through A13 Assemblies                           |     |

| A7 First LO Distribution Amplifier                               | 195 |

| Removal                                                         | .195 |

|-----------------------------------------------------------------|------|

| Replacement                                                     | .195 |

| A8 Dual Mixer (8561E/EC)                                        | .196 |

| Removal                                                         | .196 |

| Replacement                                                     | .196 |

| A8 Low Band Mixer (8563E/EC)                                    | .197 |

| Removal                                                         | .197 |

| Replacement                                                     | .197 |

| A9 Input Attenuator                                             | .198 |

| Removal                                                         | .198 |

| Replacement                                                     |      |

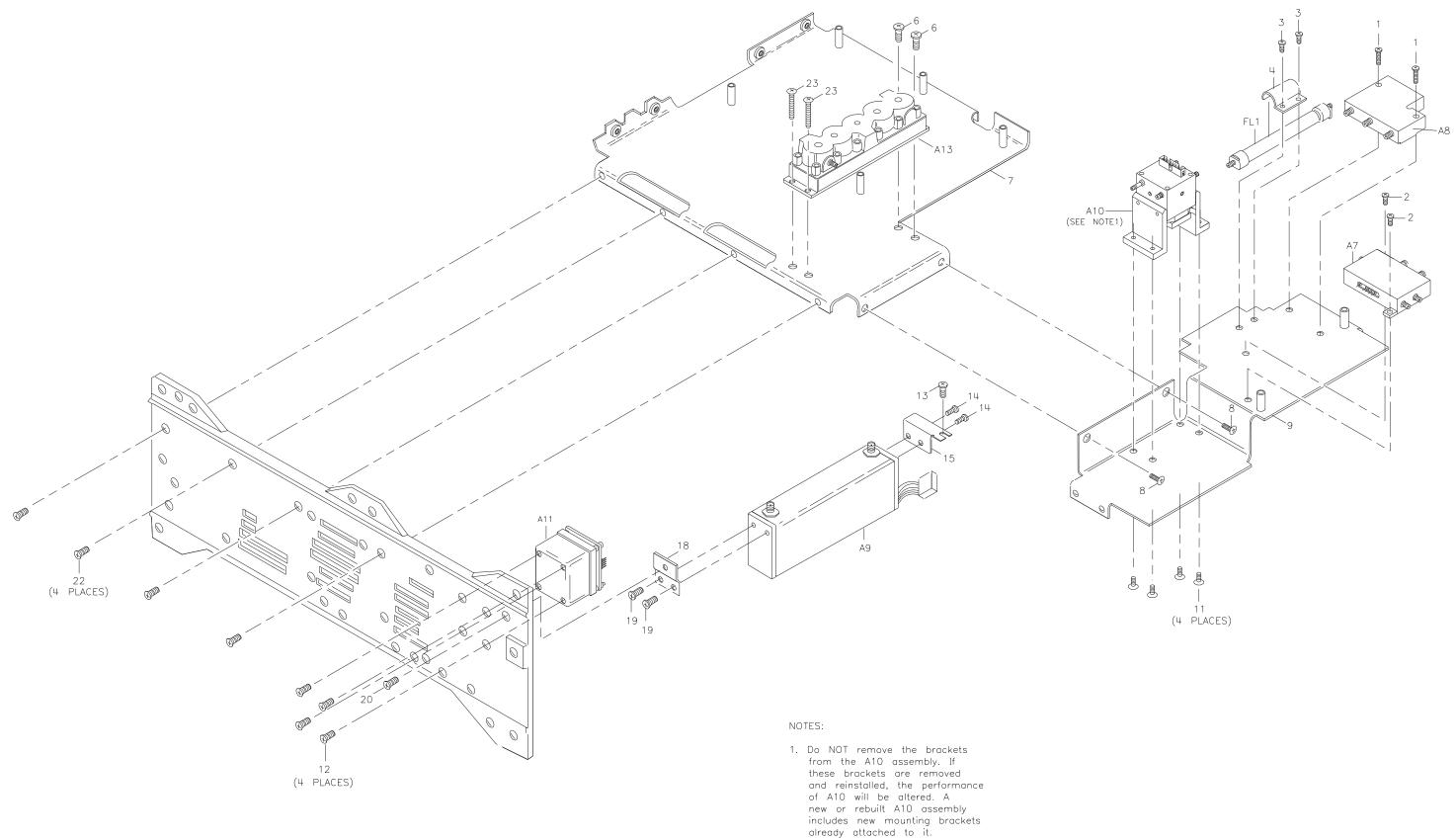

| A10 Switched YIG-Tuned Filter (SYTF, 8561E/EC)                  | .200 |

| Removal                                                         | .200 |

| Replacement                                                     | .201 |

| A10 YIG-Tuned Filter/Mixer (RYTHM, 8563E/EC)                    | .202 |

| Removal                                                         | .202 |

| Replacement                                                     | .202 |

| A11 YTO (Agilent 8561E/EC)                                      | .203 |

| Removal                                                         | .203 |

| Replacement                                                     | .203 |

| A11 YTO (8563E/EC)                                              | .204 |

| Removal                                                         | .204 |

| Replacement                                                     | .204 |

| A13 Second Converter                                            | .206 |

| Removal                                                         | .206 |

| Replacement                                                     | .206 |

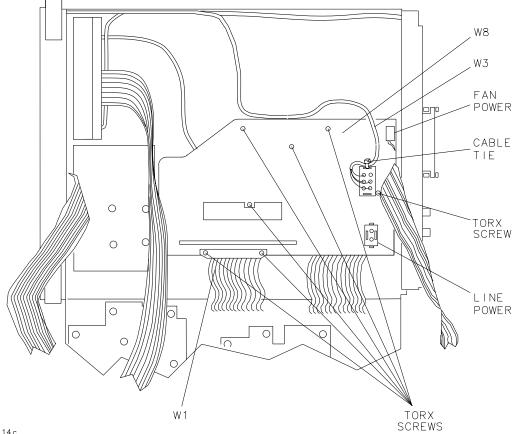

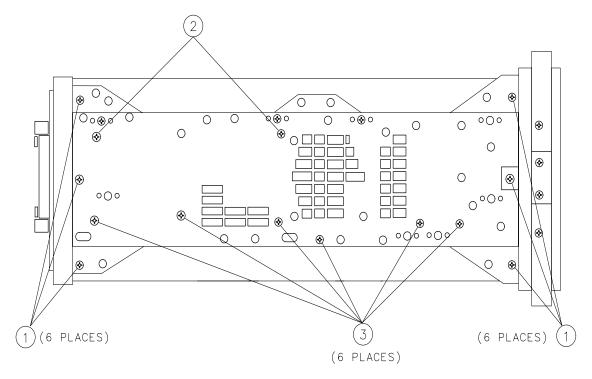

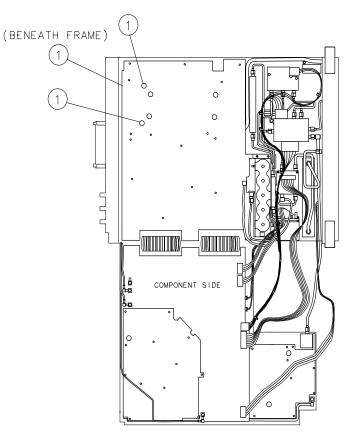

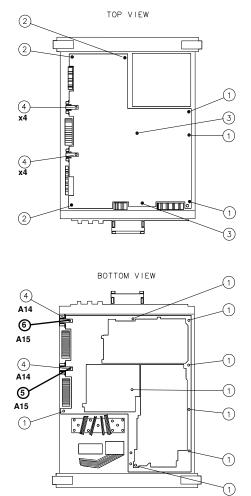

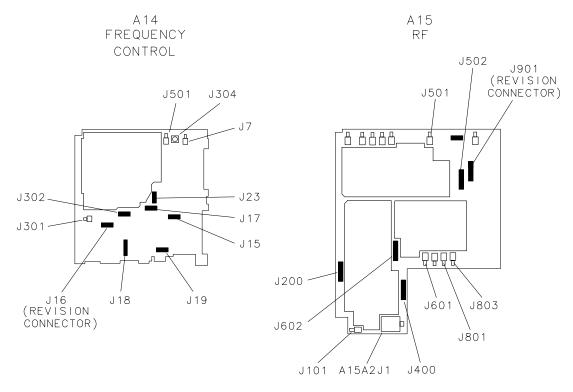

| Procedure 9. A14 and A15 Assemblies                             | .207 |

| Removal                                                         | .207 |

| Replacement                                                     | .208 |

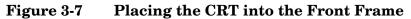

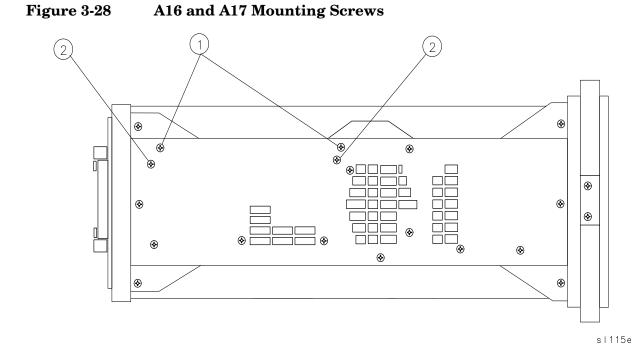

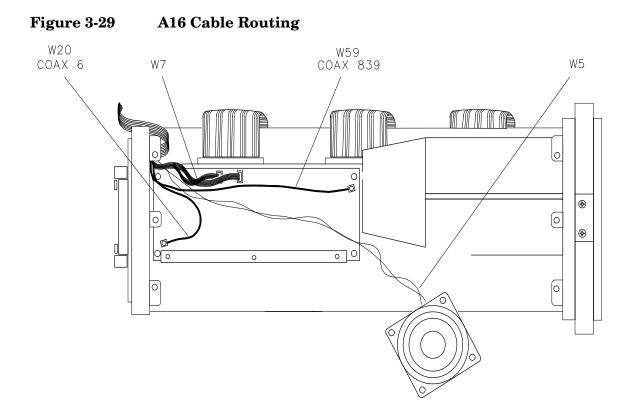

| Procedure 10. A16 Fast ADC and A17 CRT Driver (8561E and 8563E) | .210 |

| Removal                                                         | .210 |

| Replacement                                                     | .211 |

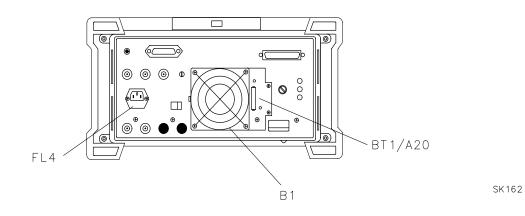

| Procedure 11. B1 Fan                                            | .213 |

| Removal/Replacement                                             | .213 |

| Procedure 12. BT1 Battery                                       | .214 |

| Removal/Replacement                                             | .214 |

| Procedure 13. Rear Frame/Rear Dress Panel                       | .215 |

| Removal                                                         | .215 |

| Replacement                                                     |      |

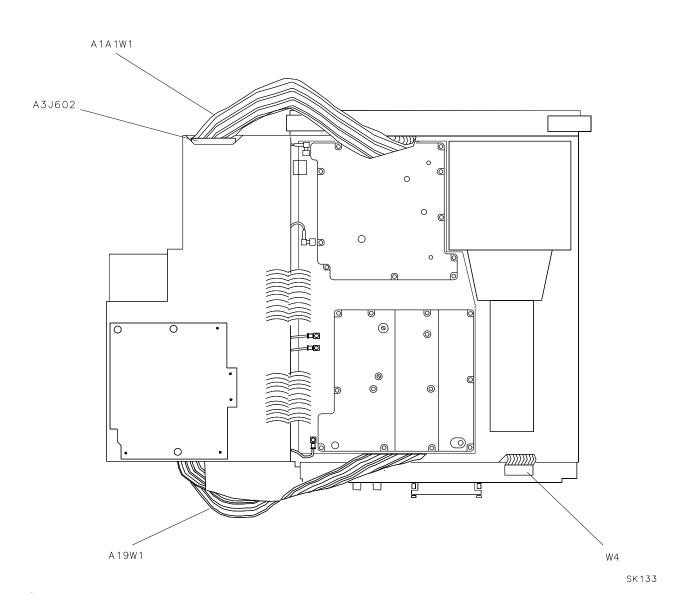

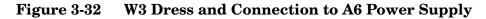

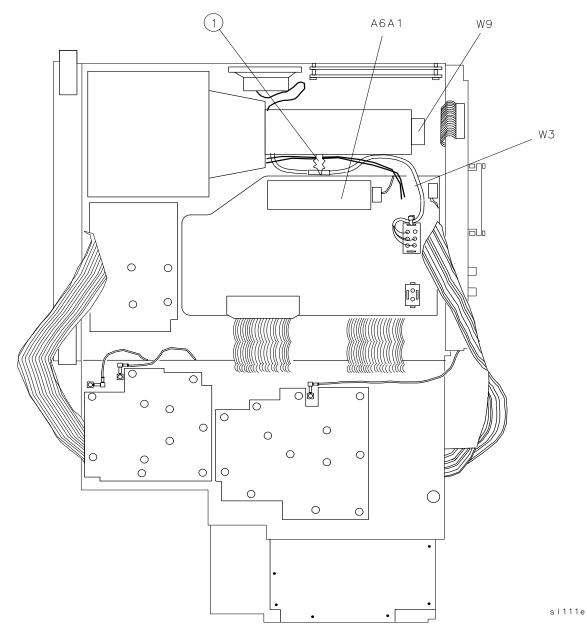

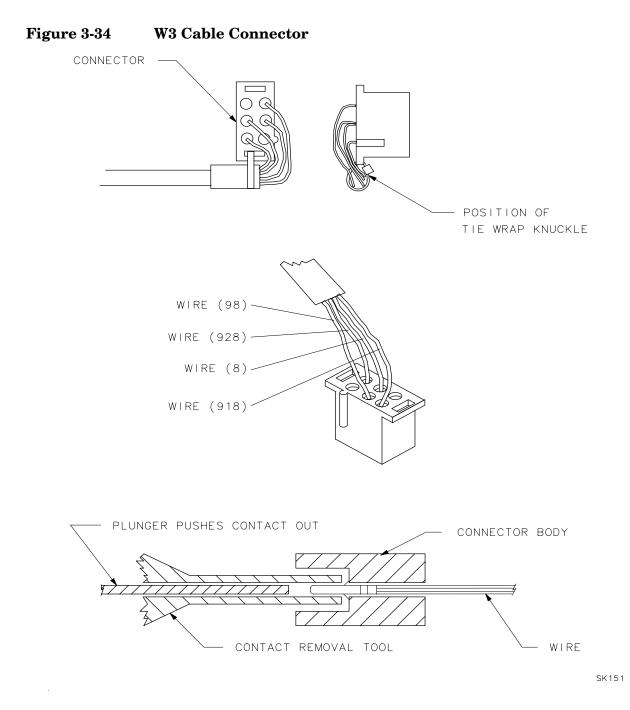

| Procedure 14. W3 Line Switch Cable (8561E and 8563E).           | .220 |

| Removal                                                         |      |

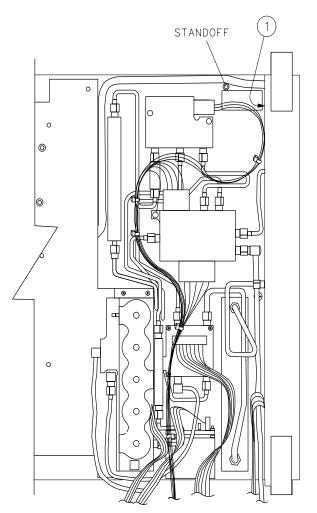

| Replacement (Using Contact Removal Tool, part number 8710-1791) |      |

| Replacement (without Contact Removal Tool)                      | .226 |

| Procedure 15. EEROM                                             | .229 |

| Removal/Replacement                                             |      |

| Procedure 16. A21 OCXO                                          | .231 |

| Removal                                                         | .231 |

| Replacement                                                     | .232 |

| 4. | Replaceable Parts                                 |     |

|----|---------------------------------------------------|-----|

|    | Introduction                                      | 234 |

|    | Ordering Information                              |     |

|    | Direct Mail-Order System                          |     |

|    | Direct Phone-Order System                         |     |

|    | Parts List Format                                 |     |

|    | Firmware-Dependent Part Numbers                   |     |

|    |                                                   | 201 |

| 5  | Major Assembly and Cable Locations                |     |

| J. | Introduction                                      | 280 |

|    |                                                   | 200 |

| G  | General Troubleshooting                           |     |

| 0. | Introduction                                      | 206 |

|    | Assembly Level Text                               |     |

|    | Block Diagrams                                    |     |

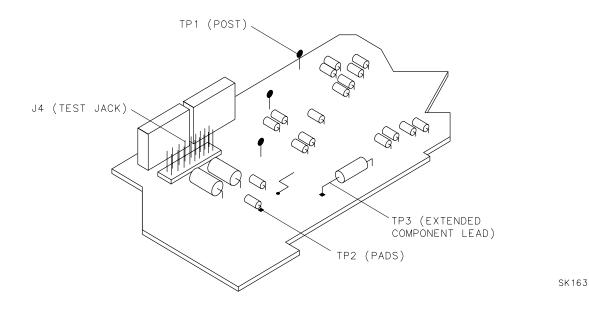

|    | Assembly Test Points                              |     |

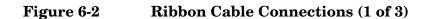

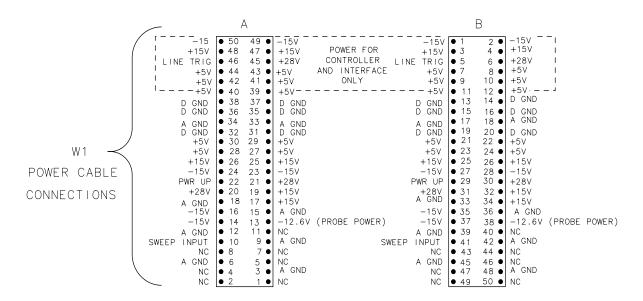

|    | Ribbon Cables                                     |     |

|    |                                                   |     |

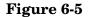

|    | Service Cal Data Softkey Menus                    |     |

|    | Troubleshooting to a Functional Section           |     |

|    | TAM (Test and Adjustment Module)                  |     |

|    | Diagnostic Functions                              |     |

|    | TAM Requirements                                  |     |

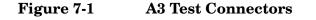

|    | Test Connectors                                   |     |

|    | Inconsistent Results                              |     |

|    | Erroneous Results (8561E and 8563E)               |     |

|    | Blank Display (8561E and 8563E)                   |     |

|    | Automatic Fault Isolation                         |     |

|    | Manual Probe Troubleshooting                      |     |

|    | RF Path Fault Isolation                           | 309 |

|    | Calibration Oscillator Troubleshooting Mode       |     |

|    | Error Messages                                    | 311 |

|    | Viewing Multiple Messages                         | 312 |

|    | Error Message Elimination                         | 312 |

|    | System Analyzer Programming Errors (100 to 150)   | 312 |

|    | ADC Errors (200 to 299)                           | 314 |

|    | LO and RF Hardware/Firmware Failures (300 to 399) | 315 |

|    | Automatic IF Errors (400 to 599)                  | 327 |

|    | System Errors (600 to 651)                        | 340 |

|    | Digital and Checksum Errors (700 to 799)          |     |

|    | Option Module Errors (800 to 899)                 |     |

|    | User-Generated Errors (900 to 999)                |     |

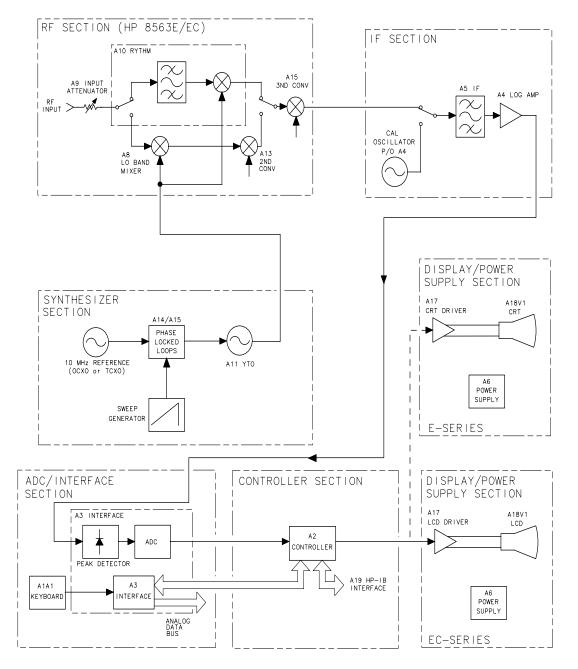

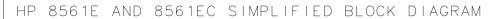

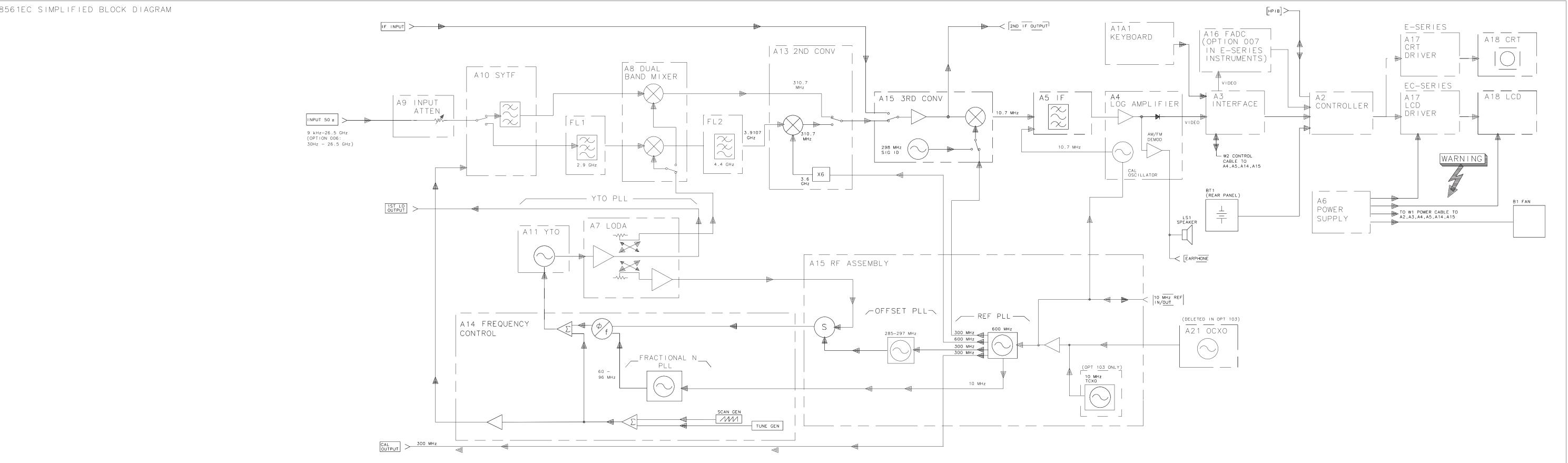

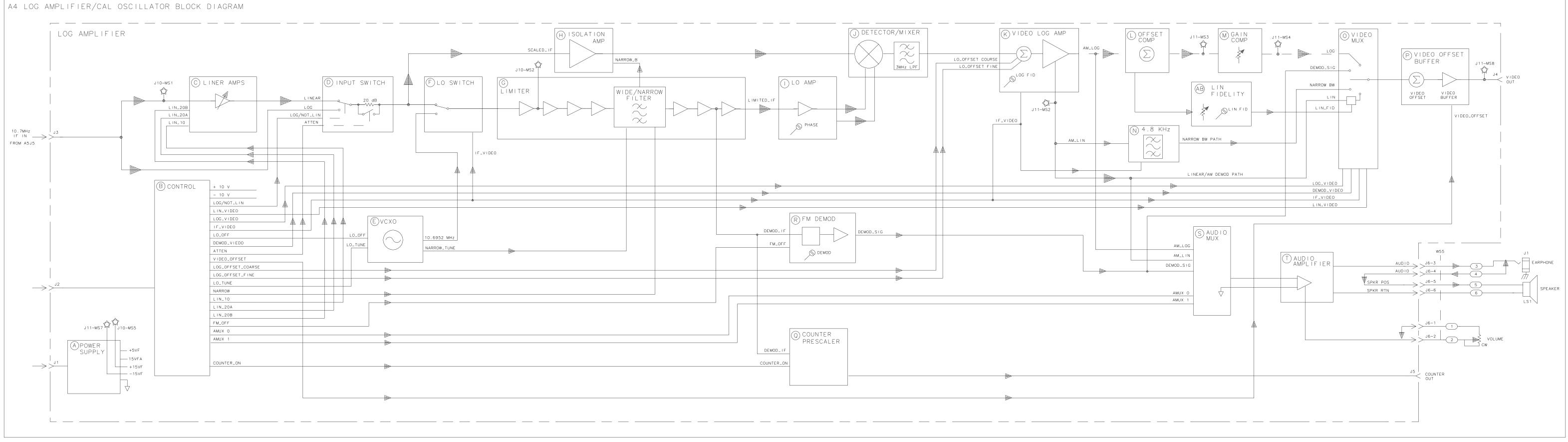

|    | Block Diagram Description                         |     |

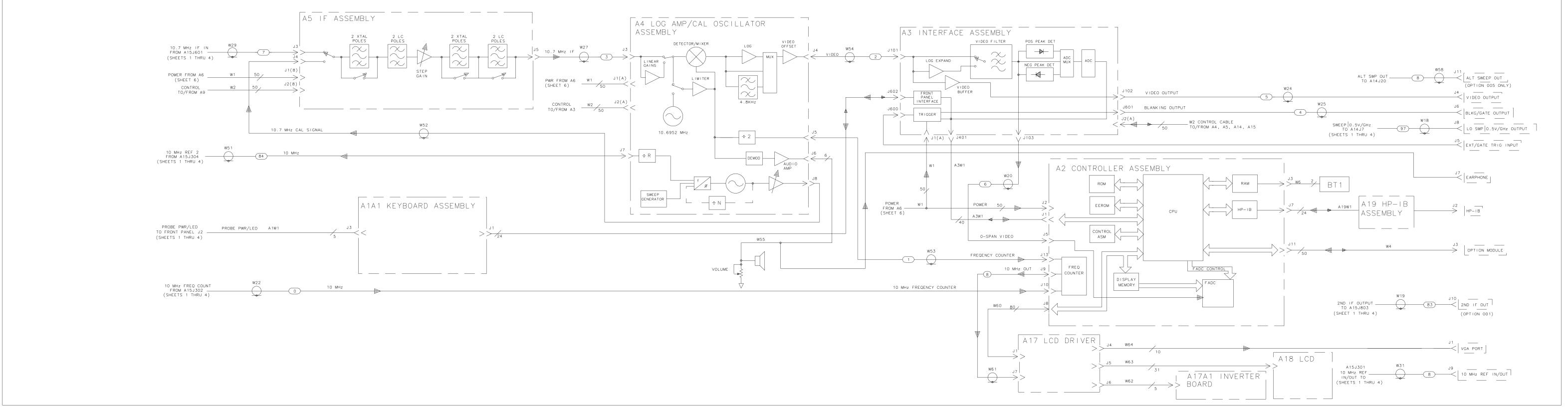

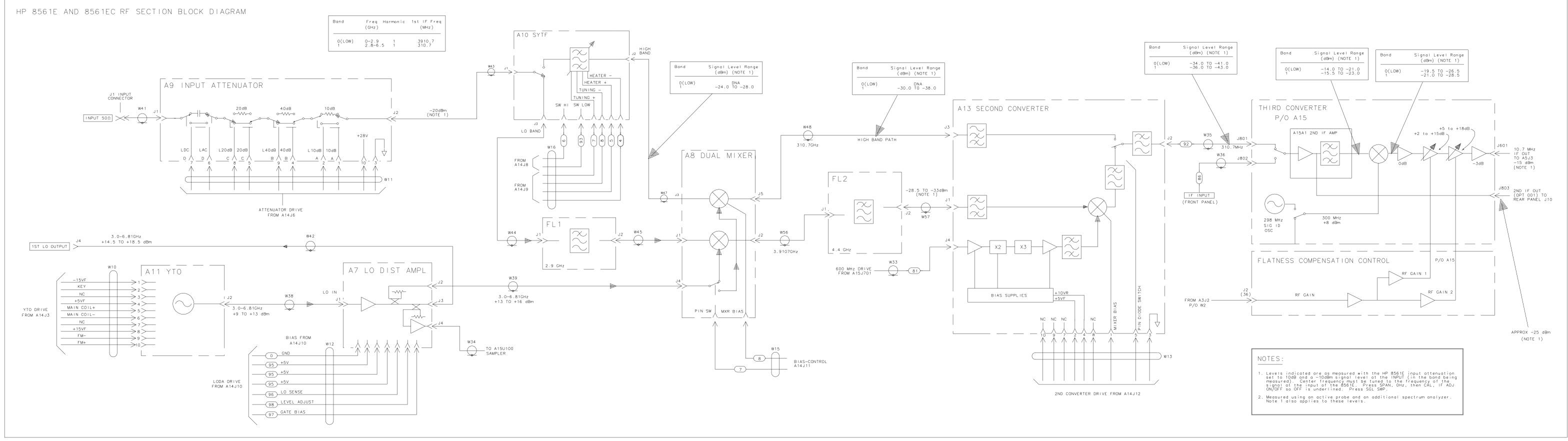

|    | RF Section (8561E/EC)                             |     |

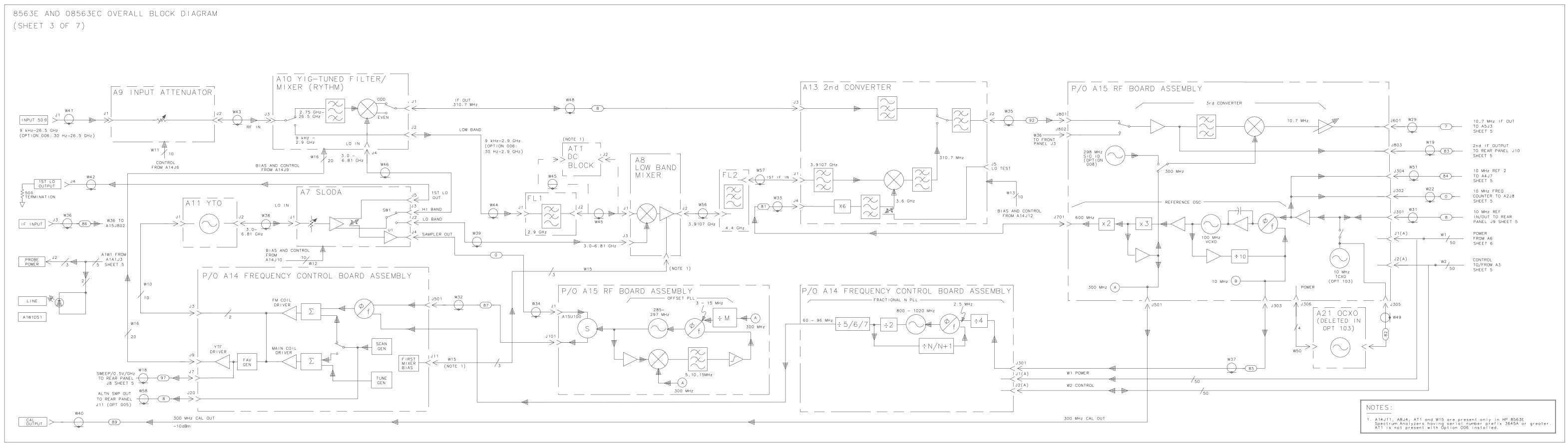

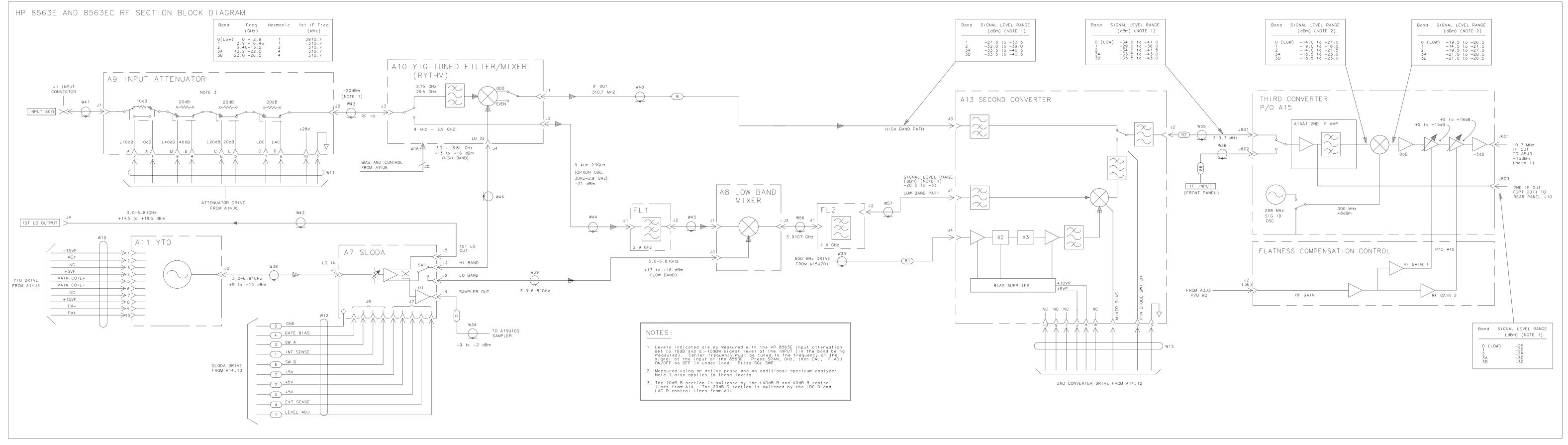

|    | RF Section (8563E/EC)                             |     |

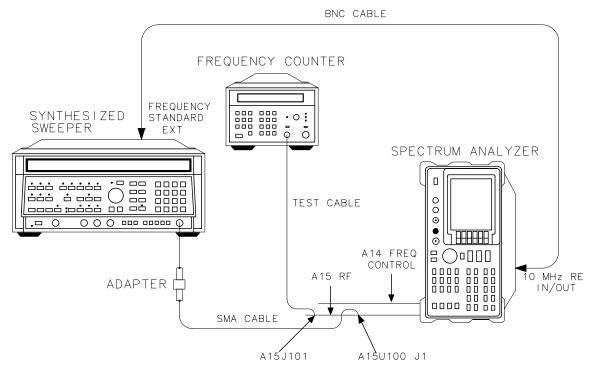

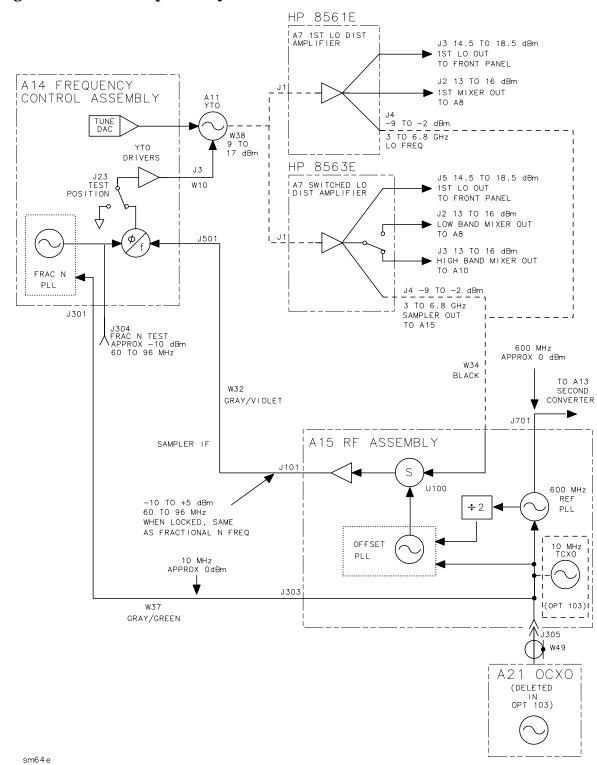

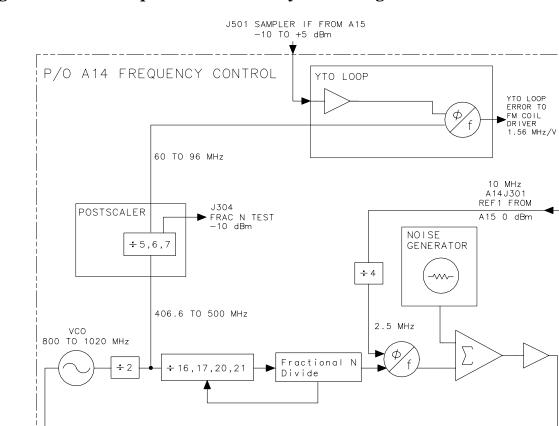

|    | Synthesizer Section                               |     |

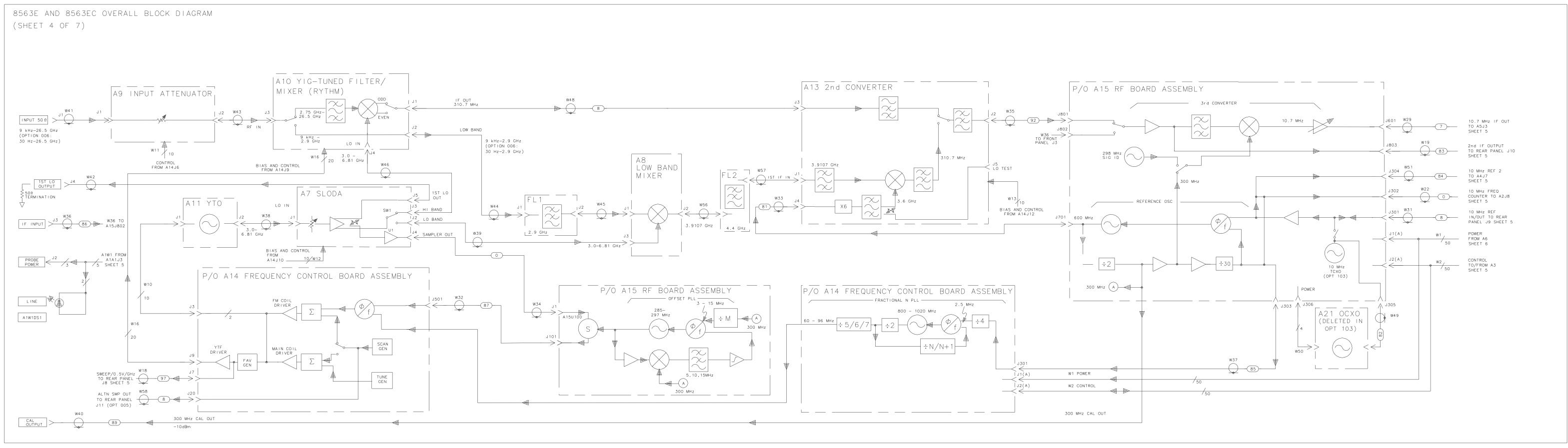

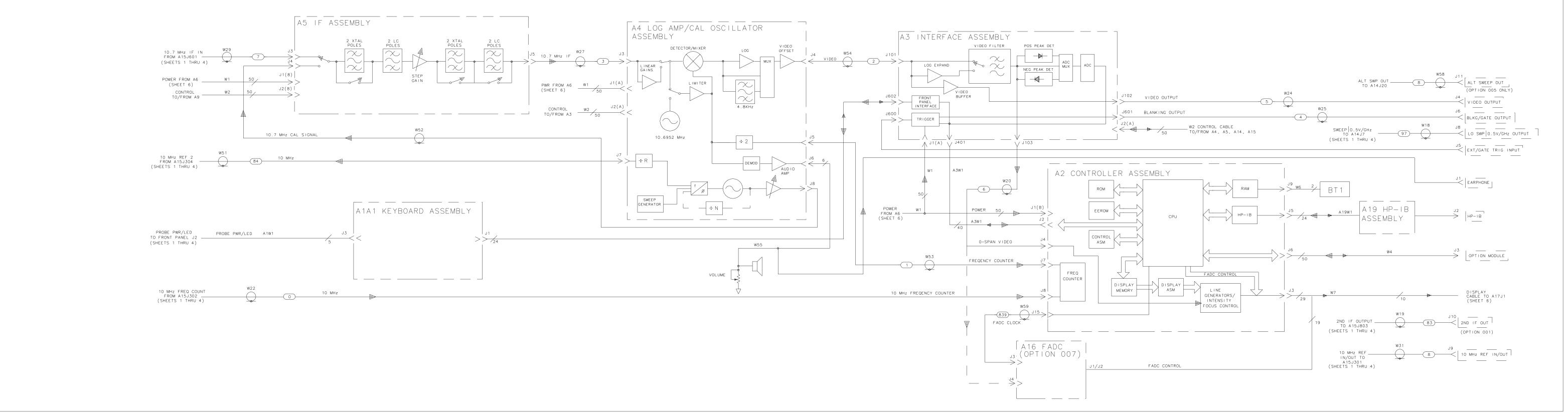

|    | IF Section                                        |     |

|    | ADC/Interface Section                             |     |

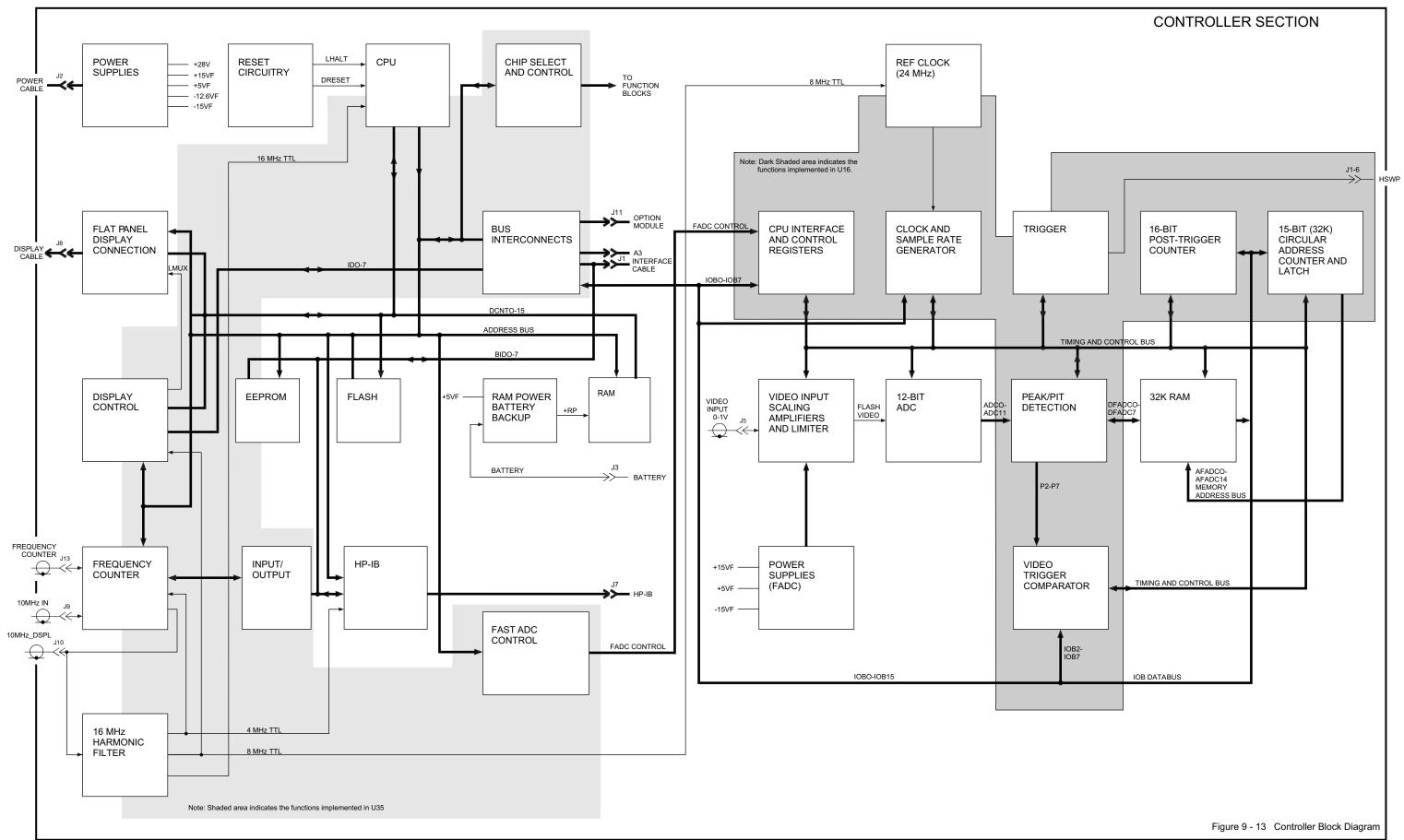

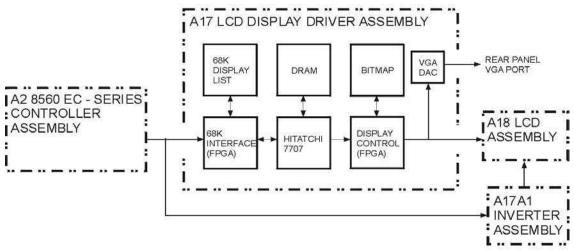

|    | Controller Section                                | 357 |

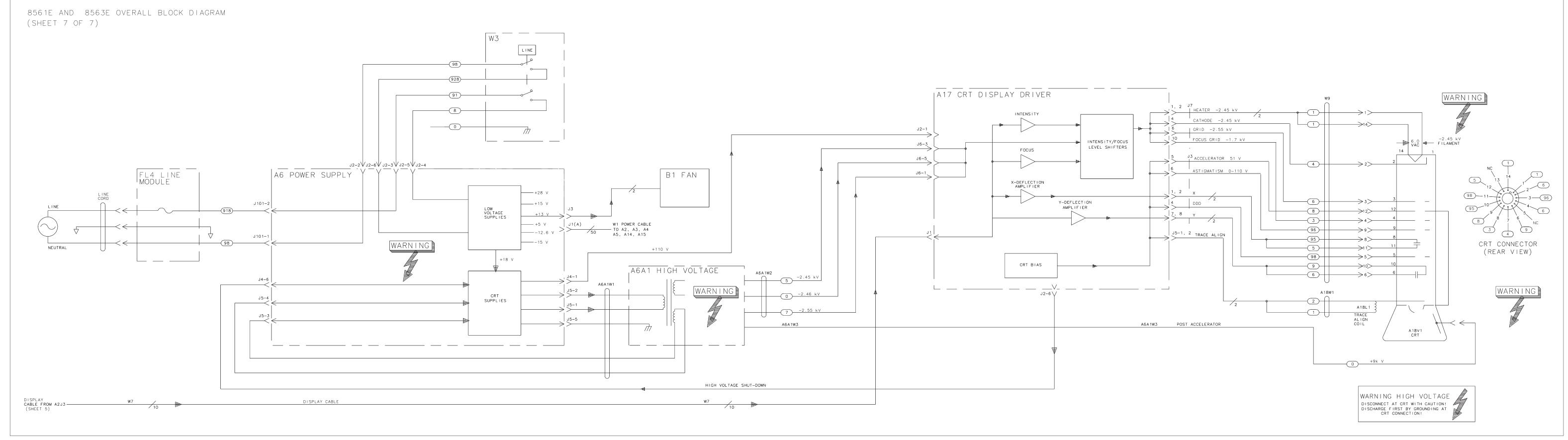

|    | Display/Power Supply Section                                               | 360 |

|----|----------------------------------------------------------------------------|-----|

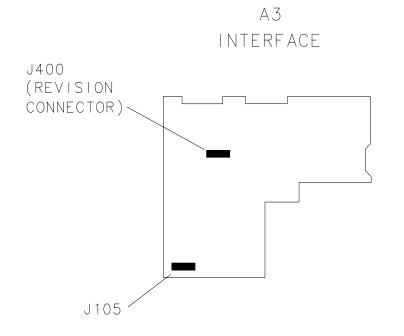

| 7. | ADC/Interface Section                                                      |     |

|    | Introduction                                                               |     |

|    | Troubleshooting Using the TAM                                              |     |

|    | Automatic Fault Isolation                                                  |     |

|    | Keyboard/RPG Problems                                                      |     |

|    | Keyboard Interface                                                         |     |

|    | RPG Interface                                                              |     |

|    | Triggering or Video Gating Problems                                        |     |

|    | Preselector Peaking Control (Real Time DAC)                                |     |

|    | Flatness Control (RF Gain DACs)                                            |     |

|    | A3 Assembly's Video Circuits                                               |     |

|    | Log Offset/Log Expand                                                      |     |

|    | Video MUX                                                                  |     |

|    | Video Filter                                                               | 398 |

|    | Video Filter Buffer Amplifier                                              | 399 |

|    | Positive/Negative Peak Detectors                                           |     |

|    | Peak Detector Reset                                                        |     |

|    | Rosenfell Detector                                                         |     |

|    | ADC MUX                                                                    | 403 |

|    | Variable Gain Amplifier (VGA)                                              | 405 |

|    | Track and Hold                                                             |     |

|    | A3 Assembly's ADC Circuits                                                 |     |

|    | ADC Control Signals                                                        |     |

|    | ADC Start/Stop Control                                                     |     |

|    | ADC ASM                                                                    |     |

|    | ADC                                                                        |     |

|    | Ramp Counter                                                               |     |

|    | A3 Assembly's Control Circuits                                             |     |

|    | Analog Bus Drivers                                                         |     |

|    | Analog Bus Timing                                                          | 411 |

|    | Interface Strobe Select                                                    |     |

|    | A16 Assembly's Fast ADC Circuits (8561E and 8563E with Option 007)         |     |

|    | Video Input Scaling Amplifiers and Limiter                                 |     |

|    | 8-Bit Flash ADC                                                            |     |

|    | Peak/Pit Detection                                                         |     |

|    | 32 K-Byte Static RAM                                                       |     |

|    | A16 Assembly's Fast ADC Control Circuits (8561E and 8563E with Option 007) |     |

|    | CPU Interface and Control Registers                                        |     |

|    | Reference Clock                                                            |     |

|    | Clock and Sample Rate Generator                                            |     |

|    | Trigger                                                                    |     |

|    | 16-Bit Post-Trigger Counter                                                |     |

|    | 15-Bit (32 K) Circular Address Counter                                     |     |

|    | Video Trigger Comparator                                                   |     |

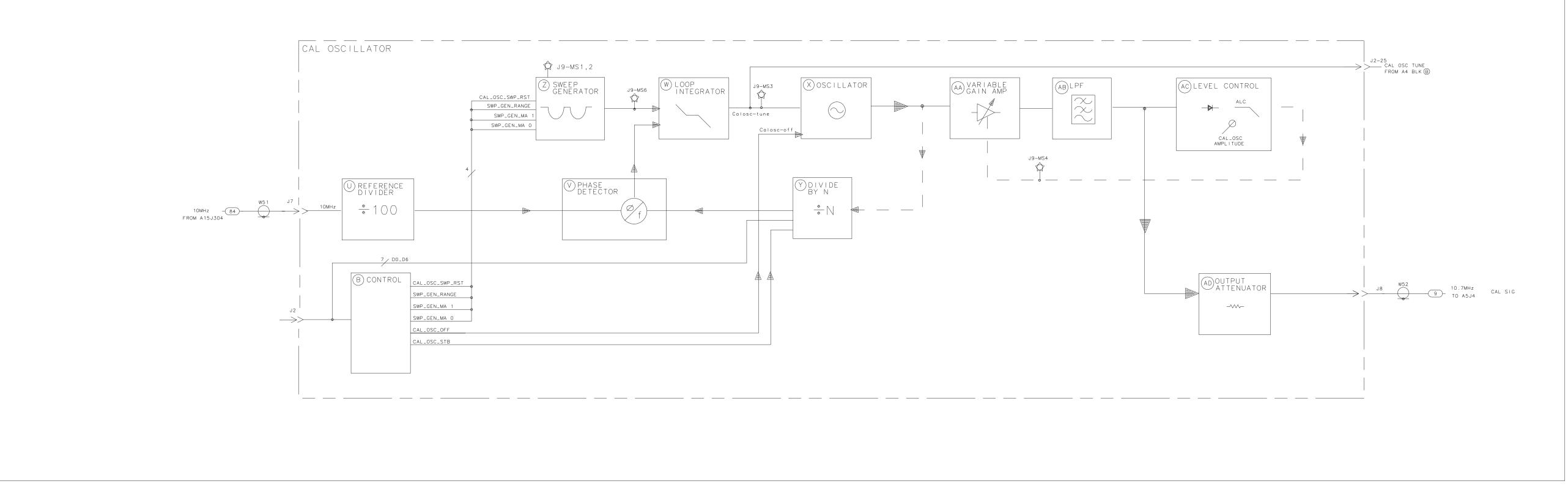

#### 8. IF Section

| Introduction                                              | . 430 |

|-----------------------------------------------------------|-------|

| Troubleshooting Using the TAM                             | . 432 |

| Troubleshooting the Log Amplifier with the TAM            |       |

| Troubleshooting A5 with the TAM                           |       |

| Troubleshooting the Cal Oscillator with the TAM           | . 437 |

| Automatic IF Adjustment                                   |       |

| Parameters Adjusted                                       |       |

| Requirements                                              |       |

| Performance Test Failures                                 |       |

| IF Gain Uncertainty Performance Test                      |       |

| Scale Fidelity Performance Test                           |       |

| Resolution Bandwidths Performance Tests                   |       |

| Log Amplifier (P/O A4 Assembly)                           |       |

| Log Amplifier                                             |       |

| Linear Amplifiers                                         |       |

| Video Offset                                              |       |

| Video Output                                              |       |

| Frequency Counter Prescaler/Conditioner                   |       |

| AM/FM Demodulator                                         |       |

| 4.8 kHz IF Filters                                        |       |

| 10.7 MHz IF Filters                                       |       |

| 4.8 kHz and 10.7 MHz IF Filters                           |       |

| 10.6952 MHz VCXO                                          |       |

| Input Switch                                              |       |

| LO Switch                                                 |       |

| Synchronous Detector                                      |       |

| Log Offset/Gain Compensation                              |       |

| Video MUX                                                 |       |

| A5 IF Assembly                                            |       |

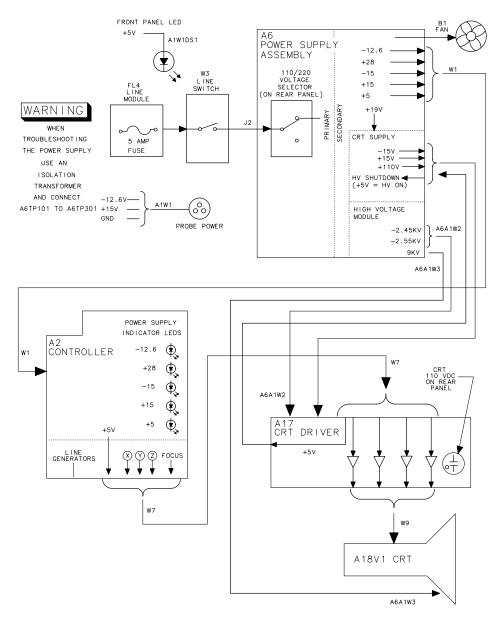

| IF Signature                                              |       |

| Common IF Signature Problems                              |       |

| 1 MHz Resolution Bandwidth Problems                       |       |

| 30 kHz Resolution Bandwidth Problems                      |       |

| 3 kHz and 10 kHz Resolution Bandwidth Problems            |       |

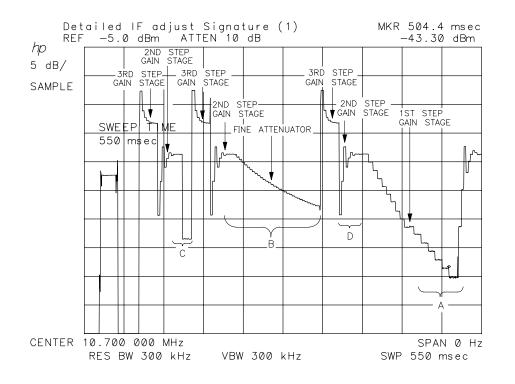

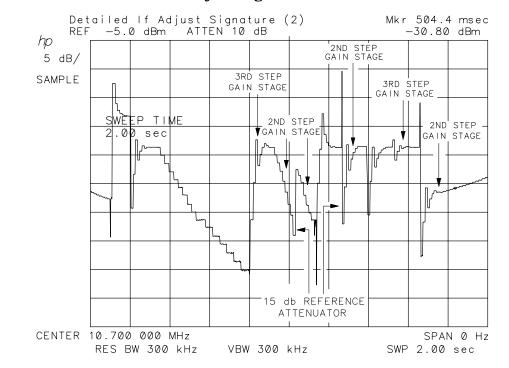

| Step Gains                                                |       |

| Cal Oscillator (P/O A4 Assembly)                          |       |

| Cal Oscillator Unlock at Beginning of IF Adjust           |       |

| Inadequate CAL OSC AMPTD Range                            | 479   |

| 300 Hz to 3 kHz Resolution Bandwidth Out of Specification | 473   |

| Low-Pass Filter                                           |       |

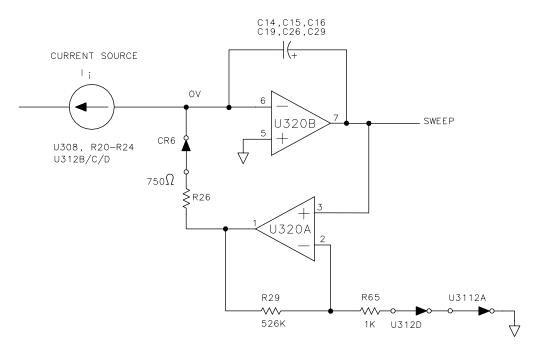

| Sweep Generator                                           |       |

| AM/FM Demodulation, Audio Amplifier, and Speaker          |       |

| Tail in Demountation, Auto Ampinier, and Speaker          | - +10 |

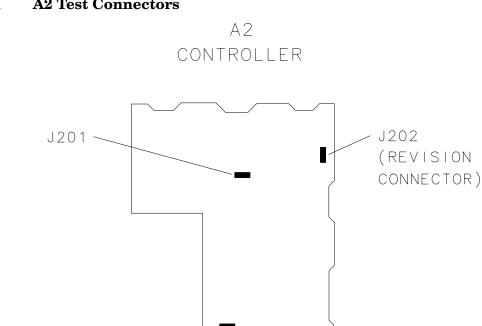

| Controller Section                                        |       |

| Introduction                                         |     |

|------------------------------------------------------|-----|

| Troubleshooting Using the TAM (8561E and 8563E only) |     |

| Blank Display                                        |     |

| Digital Signature Analysis (8561E and 8563E)         | 490 |

## www.valuetronics.com

9.

| Display Problems (8561E and 8563E)                             | 491 |

|----------------------------------------------------------------|-----|

| Line Generators                                                |     |

| Blanking                                                       |     |

| Display Jumbled or Trace Off Screen                            |     |

| Intensity                                                      |     |

| Bad Characters or Graticule                                    |     |

| Long Lines Dimmer Than Short Lines                             |     |

| Analog Zero-Span Problems (8561E and 8563E, Non-Option 007)    | 502 |

| Frequency-Count Marker Problems (8561EC and 8563EC)            | 504 |

| Frequency-Count Marker Problems (8561E and 8563E)              | 505 |

| Frequency Counter (8561EC and 8563EC))                         | 506 |

| Frequency Counter (8561E and 8563E)                            | 508 |

| Video Input Scaling Amplifiers and Limiter (8561EC and 8563EC) | 510 |

| 12-Bit Flash ADC (8561EC and 8563EC)                           | 512 |

| 32 K-Byte Static RAM (8561EC and 8563EC)                       | 512 |

| Reference Clock (8561EC and 8563EC)                            | 513 |

| 16 MHz Harmonic Filter (8561EC and 8563EC)                     | 513 |

| State- and Trace-Storage Problems                              | 514 |

| Keyboard Problems                                              | 515 |

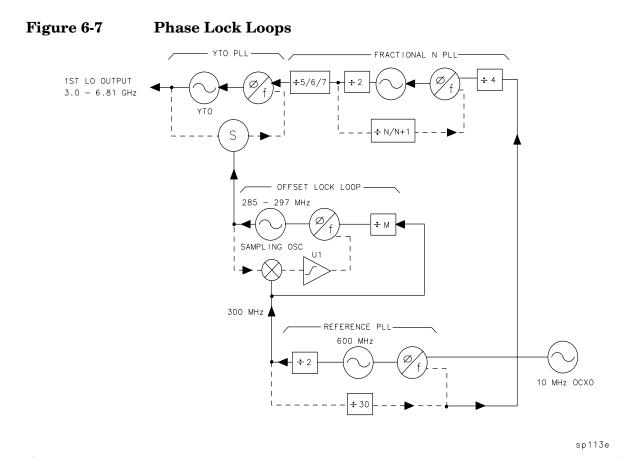

#### **10. Synthesizer Section**

| Introduction                                    |

|-------------------------------------------------|

| Troubleshooting Using the TAM                   |

| Troubleshooting Test Setup                      |

| Confirming a Faulty Synthesizer Section         |

| General PLL Troubleshooting                     |

| PLL Locked at Wrong Frequency                   |

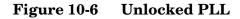

| Unlocked PLL                                    |

| Unlocked Reference PLL (100 MHz VCXO)           |

| Operation (100 MHz VCXO)                        |

| Troubleshooting (100 MHz VCXO)                  |

| Third LO Driver Amplifier (100 MHz VCXO)543     |

| Unlocked Reference PLL (600 MHz SAWR)           |

| Operation (600 MHz SAWR)                        |

| Troubleshooting (600 MHz SAWR)                  |

| Third LO Driver Amplifier (600 MHz SAWR)548     |

| Unlocked Offset Lock Loop (Sampling Oscillator) |

| Operation                                       |

| Troubleshooting                                 |

| Unlocked YTO PLL                                |

| Operation                                       |

| Troubleshooting an Unlocked YTO PLL             |

| Unlocked Fractional N PLL                       |

| Operation                                       |

| Confirming an Unlocked Condition                |

| Fractional N PLL                                |

| Frequency Span Accuracy Problems                |

| Determining the First LO Span                   |

| Confirming Span Problems                        |

| YTO Main Coil Span Problems (LO Spans >20 MHz)                               | 570 |

|------------------------------------------------------------------------------|-----|

| YTO FM Coil Span Problems (LO Spans 2.01 MHz to 20 MHz)                      | 570 |

| Fractional N Span Problems (LO Spans ≤2 MHz)                                 | 572 |

| First LO Span Problems (All Spans)                                           | 572 |

| First LO Span Problems (Multiband Sweeps)                                    | 574 |

| Phase Noise Problems                                                         | 575 |

| Phase Noise in Locked versus Unlocked Spans                                  | 575 |

| Reference versus Reference PLL Phase Noise                                   | 575 |

| Fractional N versus Offset PLL or YTO PLL Phase Noise                        | 576 |

| Fractional N PLL Phase Noise                                                 | 576 |

| Sampler and Sampler IF                                                       | 577 |

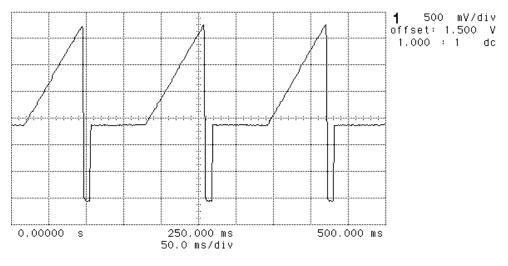

| Sweep Generator Circuit (for Spectrum Analyzers with 100 s max. Sweep Time)  | 579 |

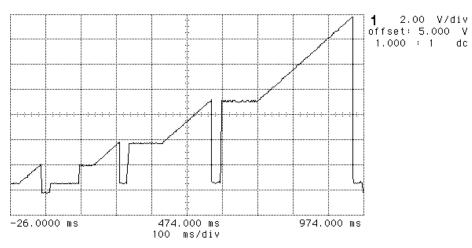

| Sweep Generator Circuit (for Spectrum Analyzers with 2000 s max. Sweep Time) | 581 |

| A21 OCXO                                                                     | 585 |

#### 11. RF Section

| Introduction                         | 594 |

|--------------------------------------|-----|

| Troubleshooting Using the TAM        | 595 |

| Low Band Problems                    | 598 |

| High Band Problems                   | 599 |

| Low and High Band Problems           | 600 |

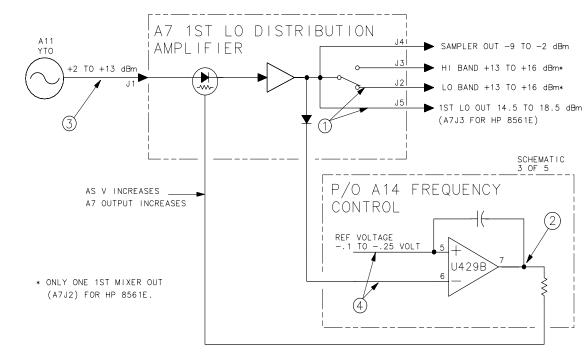

| A7 LO Distribution Amplifier         | 602 |

| A8 Dual Mixer (8561E/EC)             | 604 |

| PIN Switch                           | 604 |

| High Band Bias (8561E/EC)            | 604 |

| A8 Low Band Mixer (8563E/EC)         | 606 |

| A9 Input Attenuator                  | 607 |

| A13 Second Converter                 | 609 |

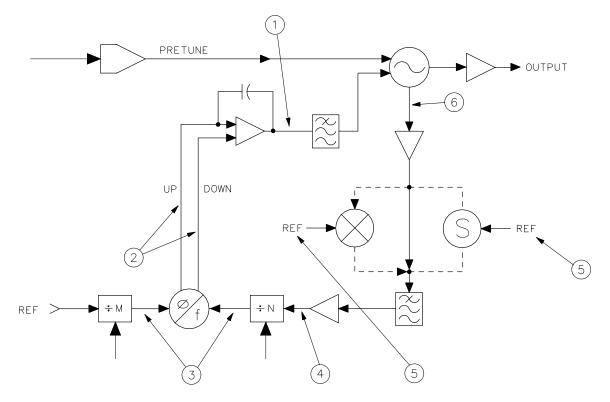

| A14 Frequency Control Assembly       | 611 |

| LODA Drive                           | 611 |

| Control Latch for Band-Switch Driver | 612 |

| YTF Driver Circuit                   | 613 |

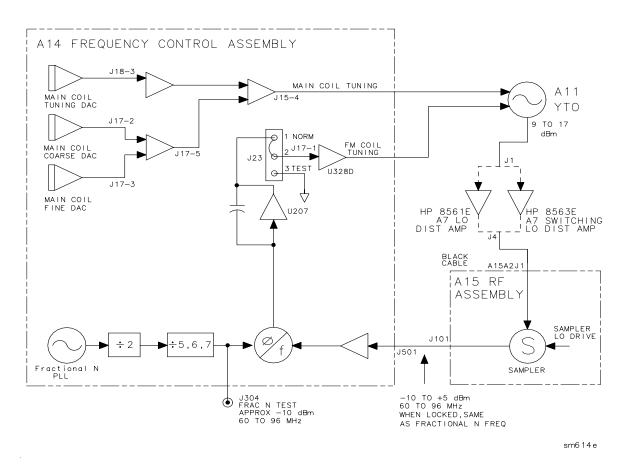

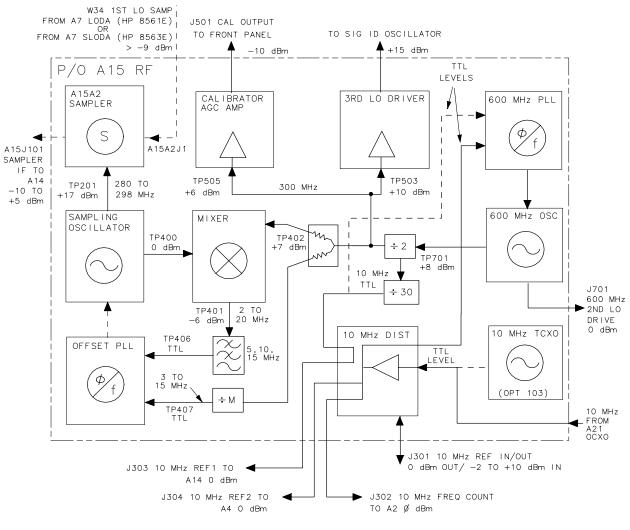

| A15 RF Assembly                      | 618 |

| Confirming a Faulty Third Converter  | 618 |

| Confirming Third Converter Output    | 618 |

| Third Converter                      | 619 |

| Flatness Compensation Control        | 621 |

| Control Latches                      | 621 |

| SIG ID Oscillator (Option 008)       | 622 |

| 10 MHz Reference                     | 623 |

|                                      |     |

### 12. Display/Power Supply Section

| 632 |

|-----|

| 633 |

| 633 |

| 635 |

| 635 |

| 636 |

| •   |

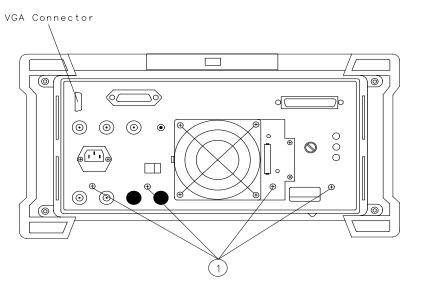

| Troubleshooting using the VGA port                   | .636 |

|------------------------------------------------------|------|

| Troubleshooting using part substitution              | .636 |

| CRT Display (8561E and 8563E)                        | .638 |

| Troubleshooting Using the TAM                        | .640 |

| Blank Display (Using the TAM)                        | .642 |

| Blank Display                                        | .643 |

| Blanking Signal                                      | .644 |

| Display Distortion                                   | .645 |

| Focus Problems                                       | .647 |

| Intensity Problems                                   | .649 |

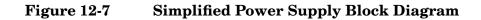

| Power Supply                                         | .651 |

| Troubleshooting Using the TAM (8561E and 8563E only) | .654 |

| A6 Power Supply Assembly                             | .655 |

| Dead Power Supply                                    | .655 |

| Line Fuse Blowing                                    | .657 |

| Supply Restarting Every 1.5 Seconds (Kick Start)     | .657 |

| Low Voltage Supplies                                 | .657 |

| High Voltage Supplies (8561E and 8563E)              | .658 |

| CRT Supply Dropping Out (8561E and 8563E )           | .659 |

| Blanking Signal (8561E and 8563E)                    | .660 |

| Buck Regulator Control                               | .660 |

| DC-DC Converter Control                              | .661 |

| Power Up                                             | .661 |

|                                                      |      |

#### 13. Component-Level Information Packets

| Figure 1-1 . Serial Number Label Example                                   |     |

|----------------------------------------------------------------------------|-----|

| Figure 1-2. Earlier Serial Number Label Example                            |     |

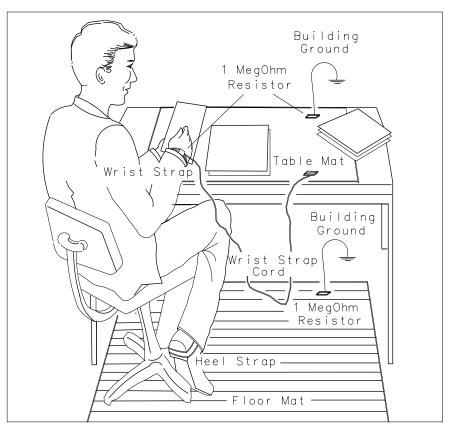

| Figure 1-3 . Example of a Static-Safe Workstation                          |     |

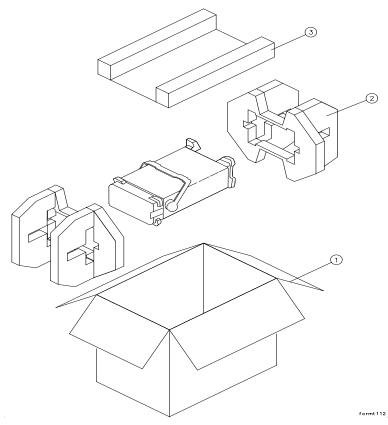

| Figure 1-4 . Spectrum Analyzer Shipping Container and Cushioning Materials |     |

| Figure 2-1 . High Voltage Power Supply Adjustment Setup                    | 60  |

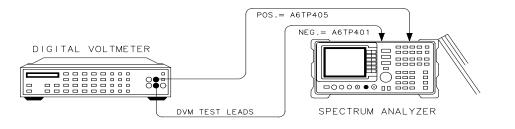

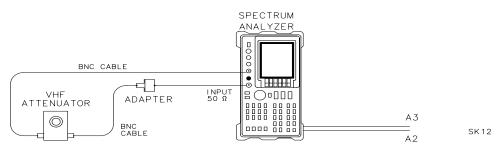

| Figure 2-2 . Display Adjustment Setup                                      | 62  |

| Figure 2-3 . CRT Adjust Pattern                                            |     |

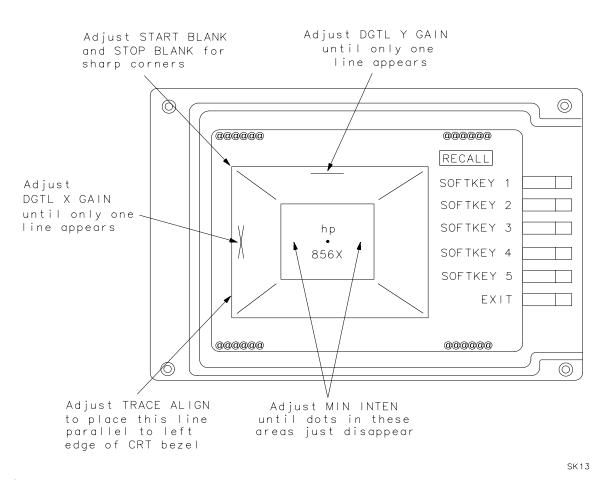

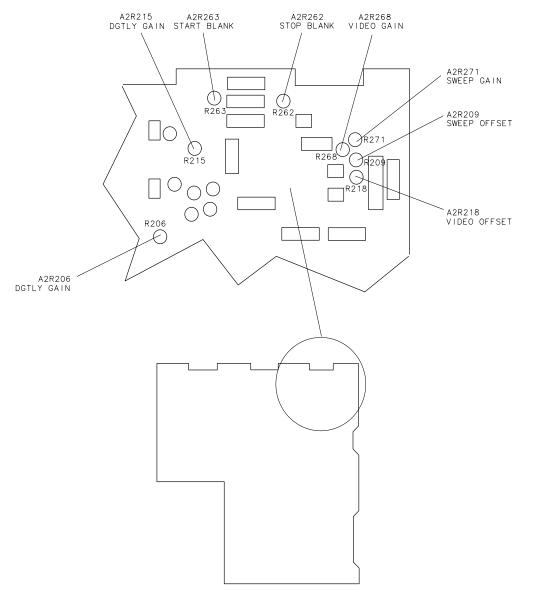

| Figure 2-4 . A2 Display Adjustment Locations                               | 66  |

| Figure 2-5 . IF Bandpass Adjustment Setup                                  | 68  |

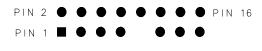

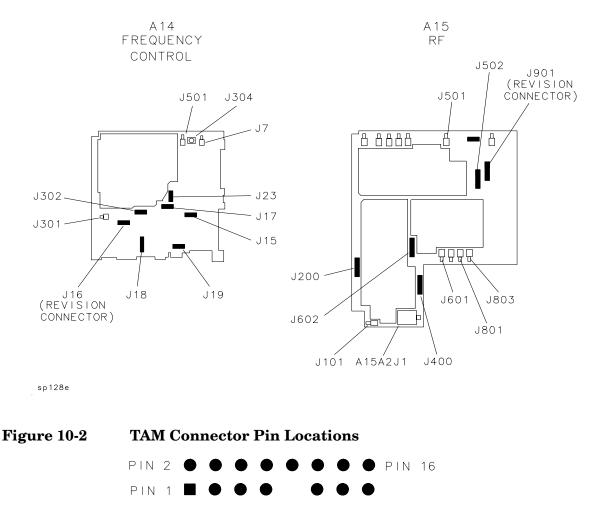

| Figure 2-6 . TAM Connector Pin Locations                                   | 69  |

| Figure 2-7 . IF Amplitude Adjustment Setup                                 |     |

| Figure 2-8 . IF Amplitude Adjustment Locations                             | 74  |

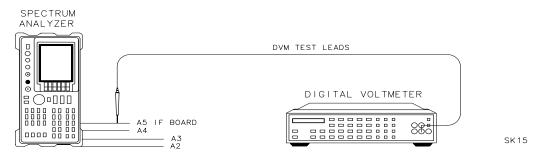

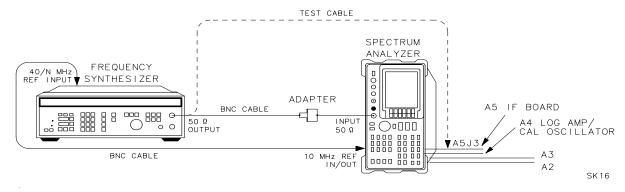

| Figure 2-9. DC Log Adjustment Setup                                        |     |

| Figure 2-10. DC Log Adjustment Locations                                   | 78  |

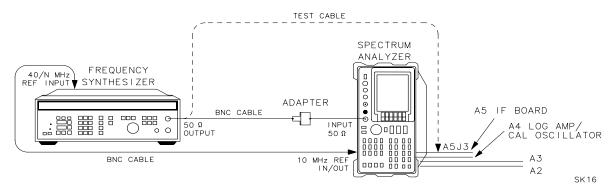

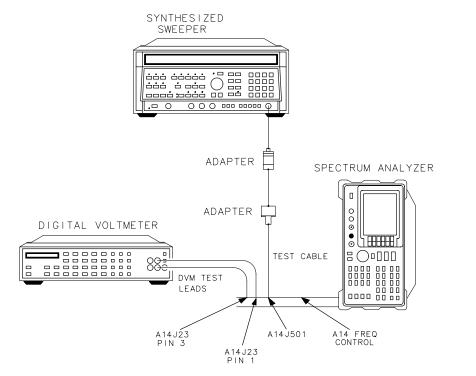

| Figure 2-11 . Sampler Adjustment Setup                                     |     |

| Figure 2-12 . TAM Connector Pin Locations                                  |     |

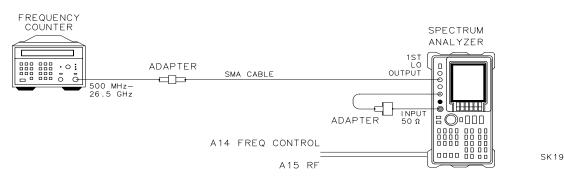

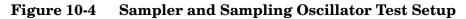

| Figure 2-13 . YTO Adjustment Setup                                         |     |

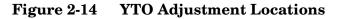

| Figure 2-14 . YTO Adjustment Locations                                     |     |

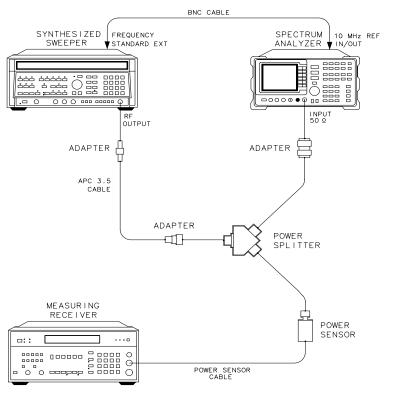

| Figure 2-15. 1st LO Distribution Amplifier Adjustment Setup                |     |

| Figure 2-16 . TAM Connector Pin Locations                                  |     |

| Figure 2-17 . First LO Distribution Amplifier Adjustment Setup             |     |

| Figure 2-18 . TAM Connector Pin Locations                                  |     |

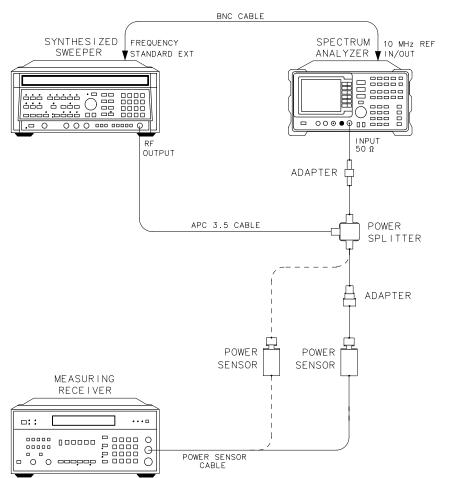

| Figure 2-19 . Dual Band Mixer Bias Adjustment Setup                        |     |

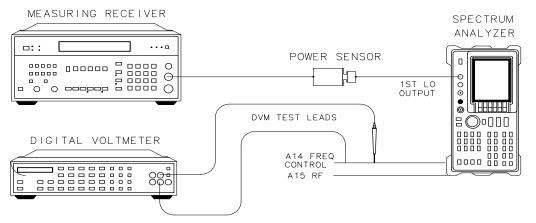

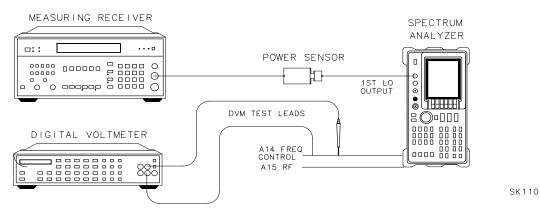

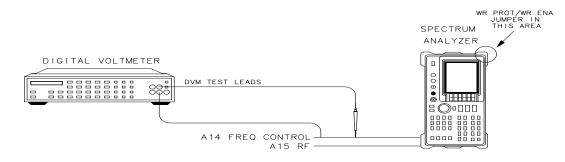

| Figure 2-20 . Frequency Response Adjustment Setup (8561E/EC)               |     |

| Figure 2-21 . Frequency Response Adjustment Setup (8563E/EC)               |     |

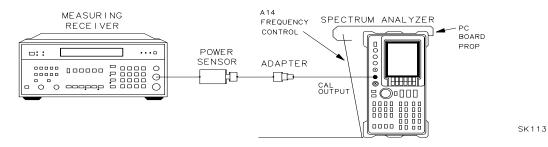

| Figure 2-22 . Calibrator Amplitude Adjustment Setup                        |     |

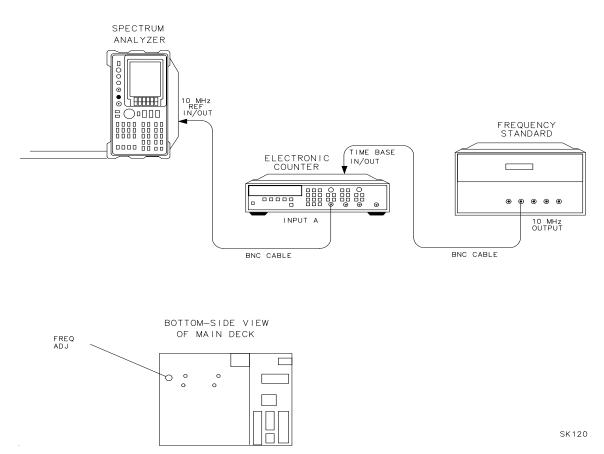

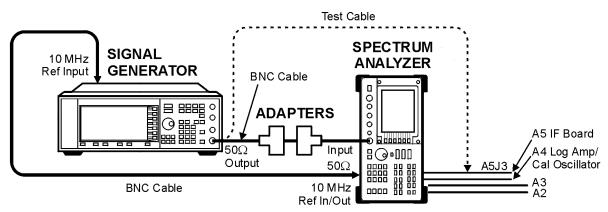

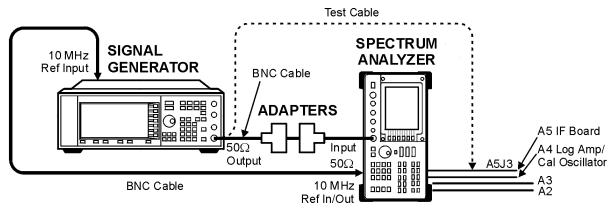

| Figure 2-23. 10 MHz Reference Adjustment Setup and Adjustment Location     |     |

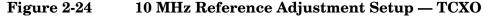

| Figure 2-24. 10 MHz Reference Adjustment Setup — TCXO                      |     |

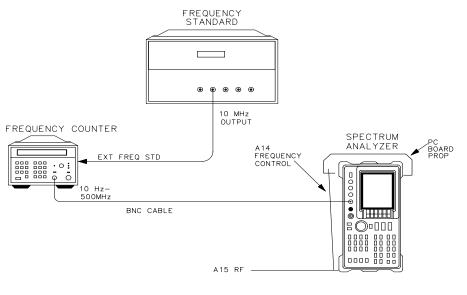

| Figure 2-25 . Demodulator Adjustment Setup                                 |     |

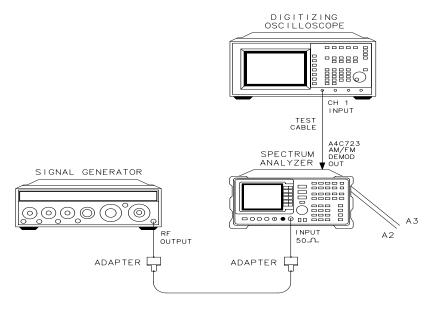

| Figure 2-26. Demodulator Adjustment Locations                              |     |

| Figure 2-27 . External Mixer Bias Adjustment Setup                         |     |

| Figure 2-28. External Mixer Amplitude Adjustment Setup                     |     |

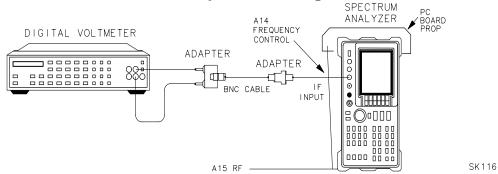

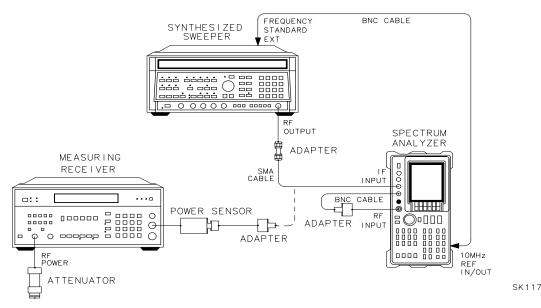

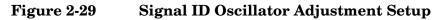

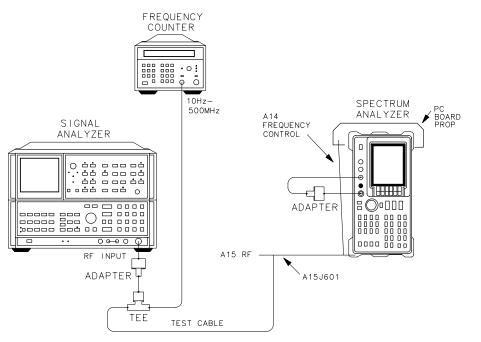

| Figure 2-29 . Signal ID Oscillator Adjustment Setup                        |     |

| Figure 2-30. Signal ID Oscillator Adjustment Jumper Location               |     |

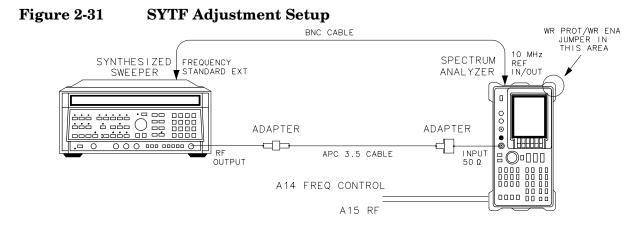

| Figure 2-31 . SYTF Adjustment Setup                                        |     |

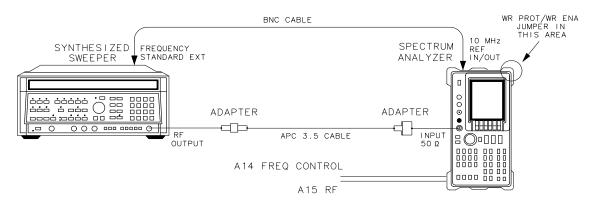

| Figure 2-32 . RYTHM Adjustment Setup                                       |     |

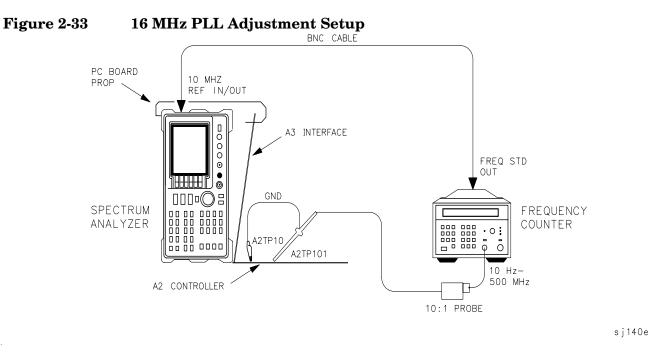

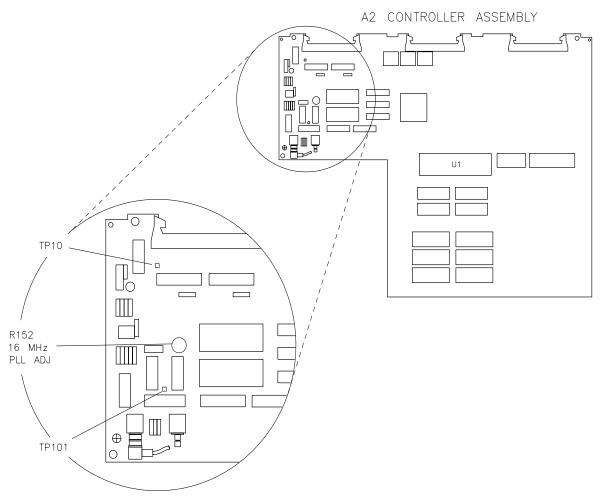

| Figure 2-33. 16 MHz PLL Adjustment Setup                                   |     |

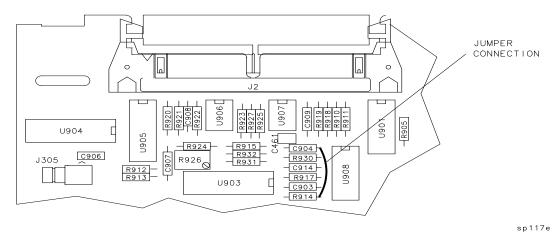

| Figure 2-34. 16 MHz PLL Adjustment Location                                |     |

| Figure 2a-1 . IF Amplitude Adjustment Setup                                |     |

| Figure 2a-2. IF Amplitude Adjustment Locations                             |     |

| Figure 2a-3 . DC Log Adjustment Setup                                      | 141 |

| Figure 2a-4 . DC Log Adjustment Locations                                  |     |

| Figure 3-1 . Hinged Assemblies                                             | 151 |

| Figure 3-2. LCD Assembly - Exploded View                                   | 156 |

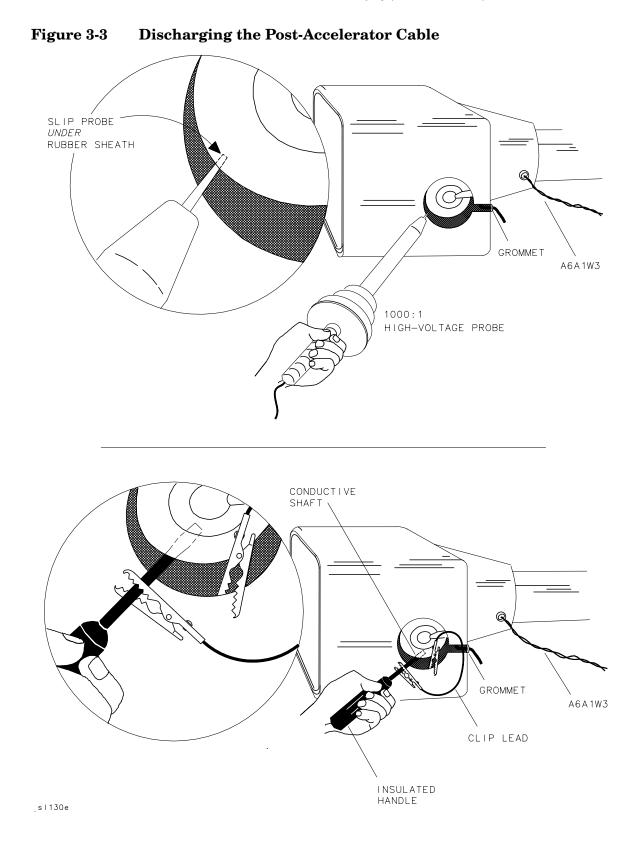

| Figure 3-3 . Discharging the Post-Accelerator Cable                        | 164 |

## Figures

| Figure 3-4 . A9, A18, and Line-Switch Assembly Mounting Screws     | 165 |

|--------------------------------------------------------------------|-----|

| Figure 3-5 . Front-Frame Mounting Screws                           | 166 |

| Figure 3-6 . Installing the CRT and Front-Frame Assemblies         | 167 |

| Figure 3-7 . Placing the CRT into the Front Frame                  |     |

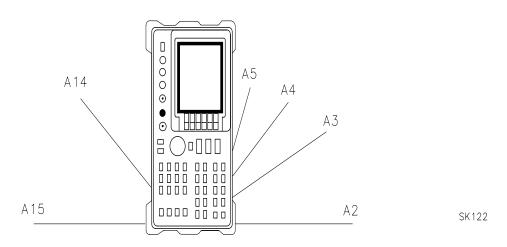

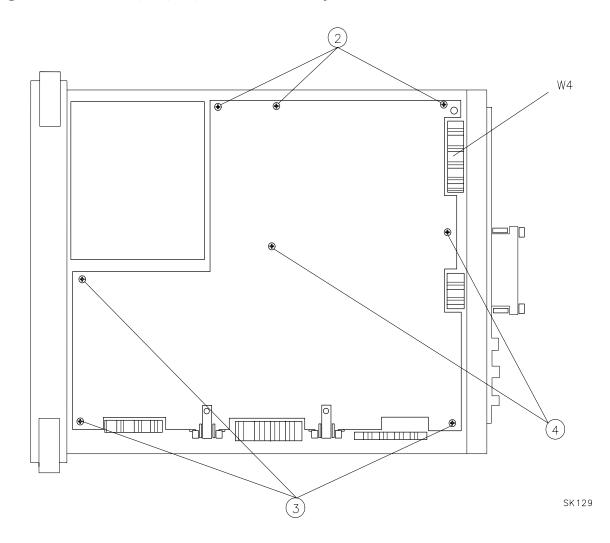

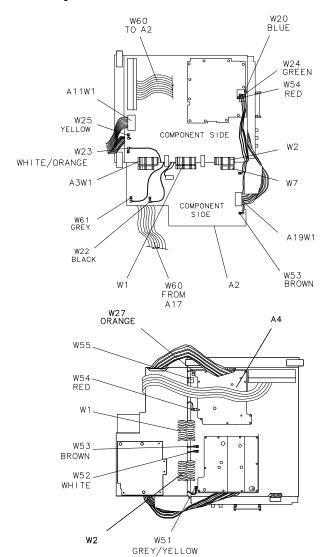

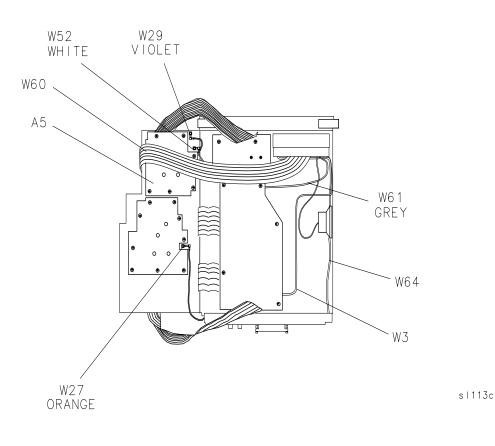

| Figure 3-8 . A2, A3, A4, and A5 Assembly Removal                   |     |

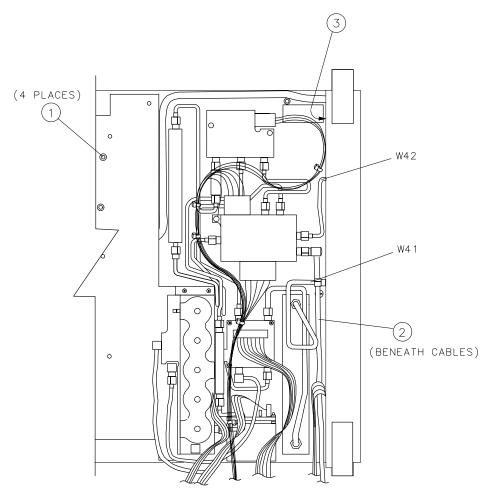

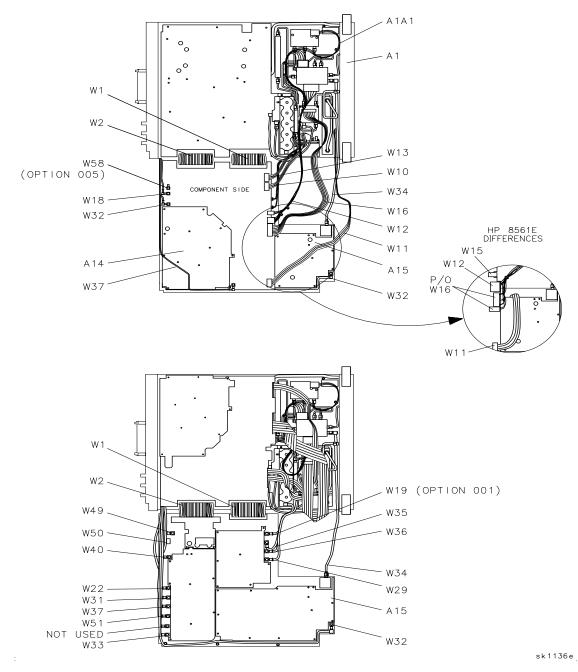

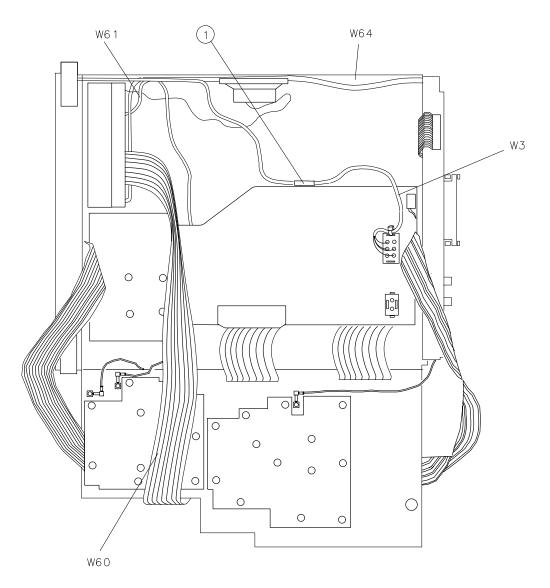

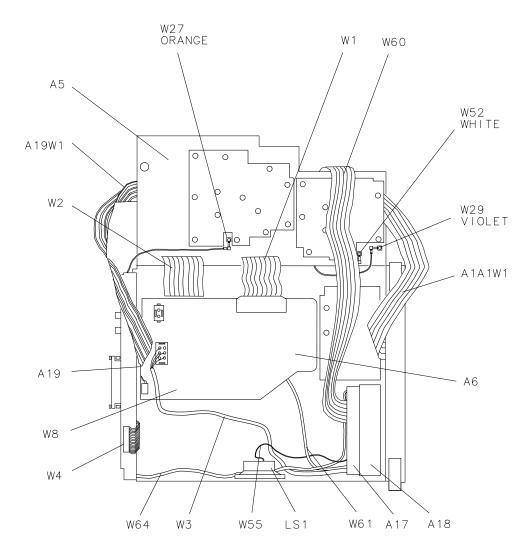

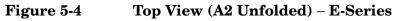

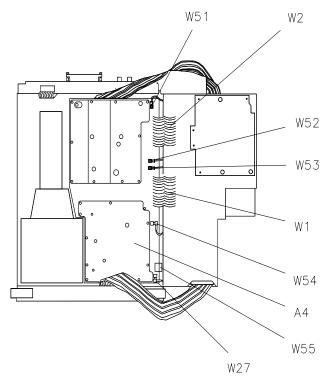

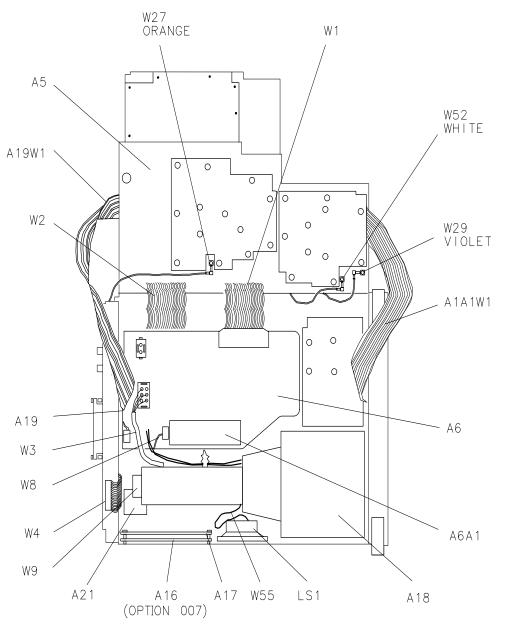

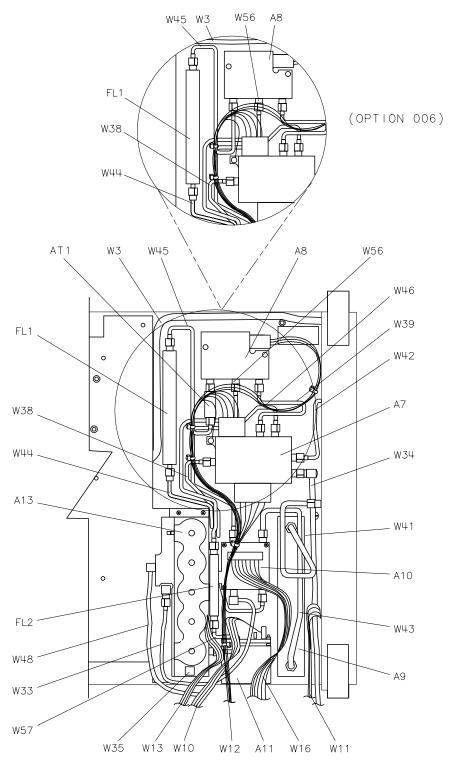

| Figure 3-9. Assembly Cables (1 of 3) – EC-Series                   | 174 |

| Figure 3-10. Assembly Cables (2 of 3) – EC-Series                  | 175 |

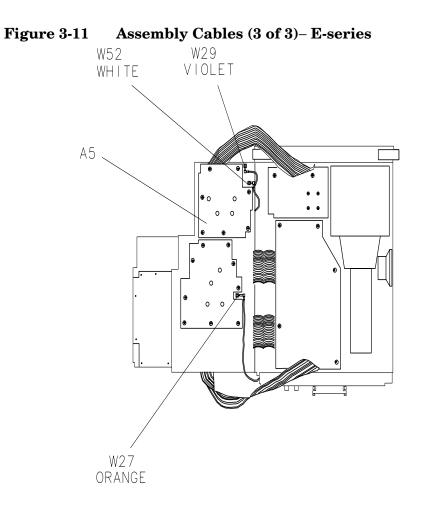

| Figure 3-11 . Assembly Cables (3 of 3)– E-series                   | 176 |

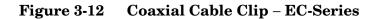

| Figure 3-12 . Coaxial Cable Clip – EC-Series                       | 177 |

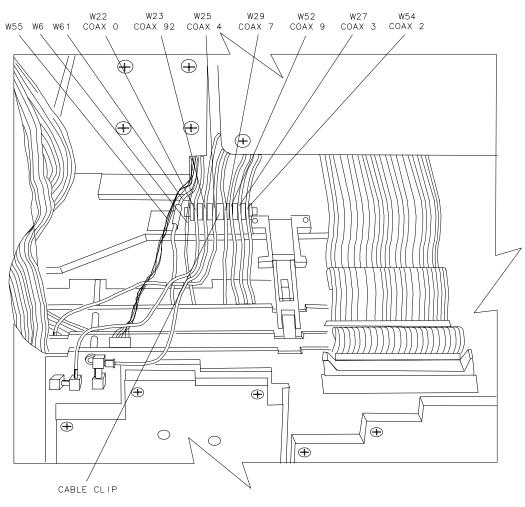

| Figure 3-13 . Coaxial Cable Clip – E-Series                        |     |

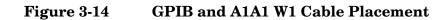

| Figure 3-14 . GPIB and A1A1 W1 Cable Placement                     | 179 |

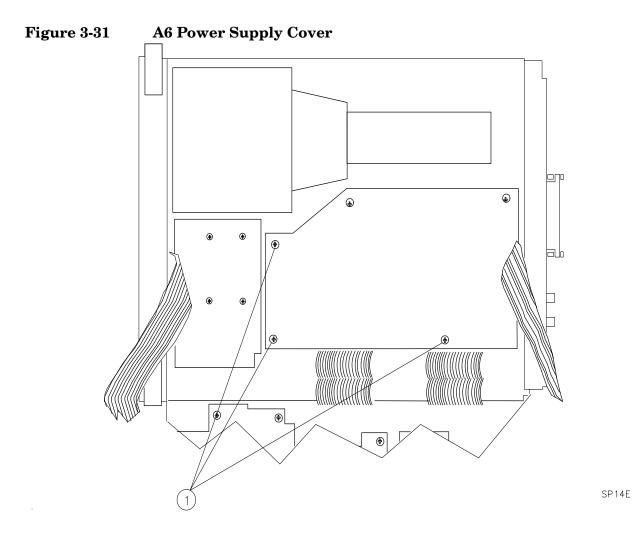

| Figure 3-15 . Power Supply Cover                                   | 181 |

| Figure 3-16 . Power Supply Cover                                   |     |

| Figure 3-17 . A6 Power Supply Connections                          | 185 |

| Figure 3-18 . Power Supply Cover                                   |     |

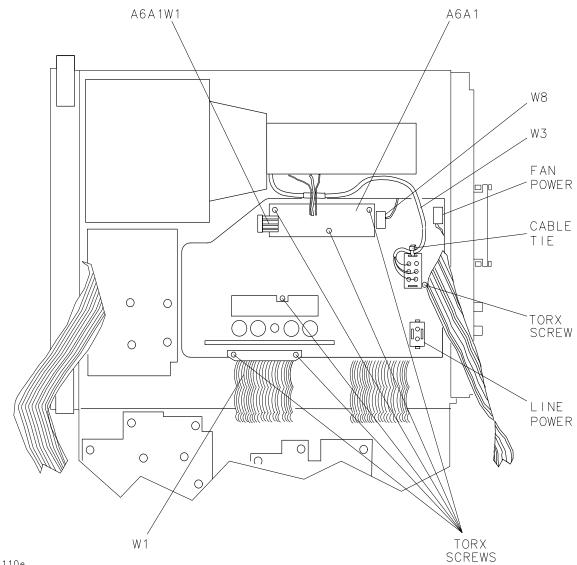

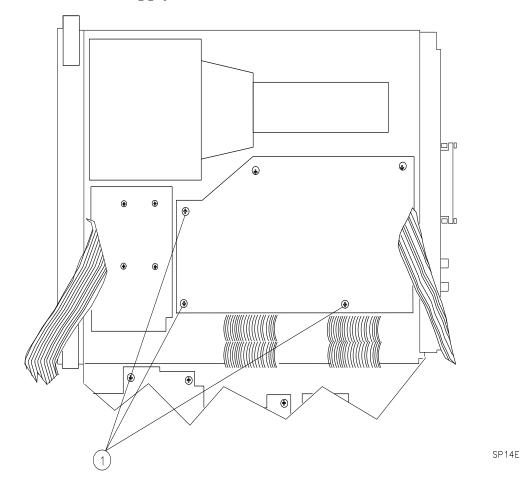

| Figure 3-19 . A16 Fast ADC and A17 CRT Driver Mounting Screws      |     |

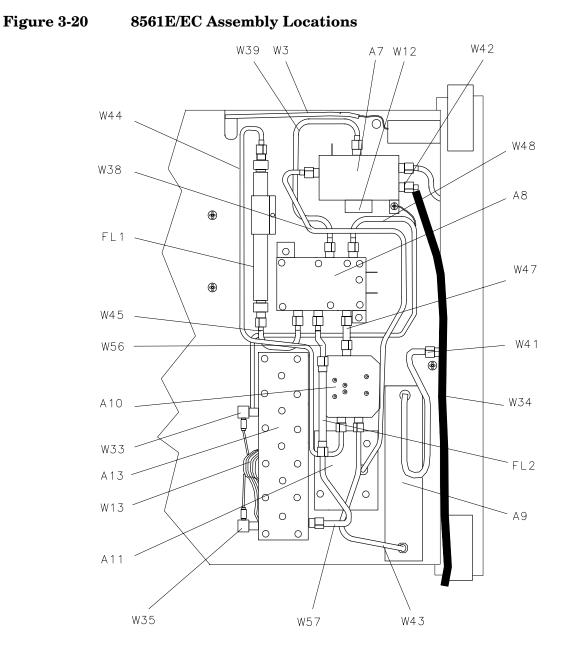

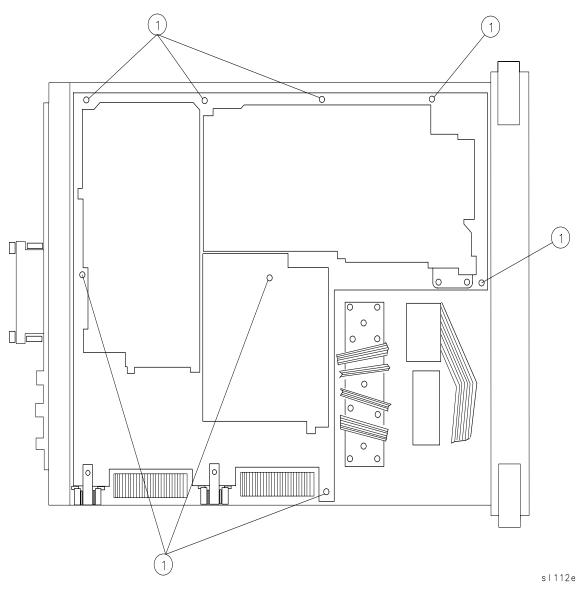

| Figure 3-20 . 8561E/EC Assembly Locations                          | 192 |

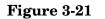

| Figure 3-21 . 8563E/EC Assembly Locations                          |     |

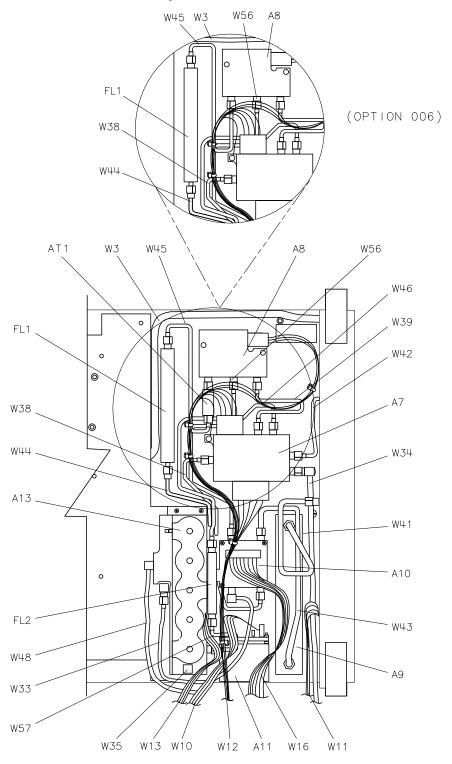

| Figure 3-22. 8561E/EC RF Section Bias Connections                  | 194 |

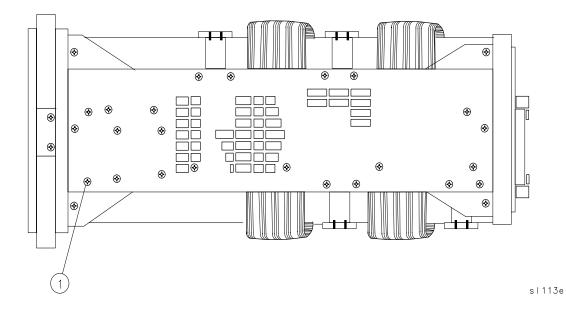

| Figure 3-23 . A9 Mounting Screw at Right Side Frame                | 199 |

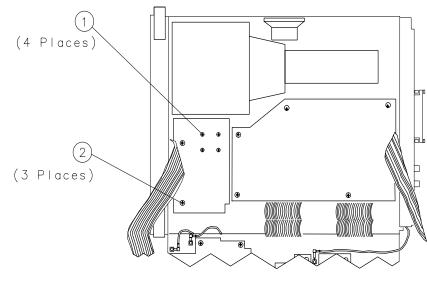

| Figure 3-24 . A10 Mounting Screws                                  | 200 |

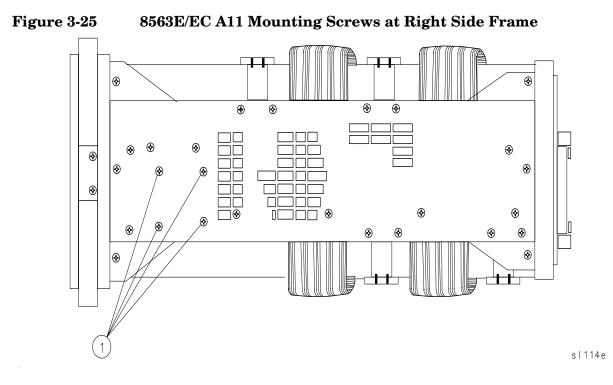

| Figure 3-25 . 8563E/EC A11 Mounting Screws at Right Side Frame     | 205 |

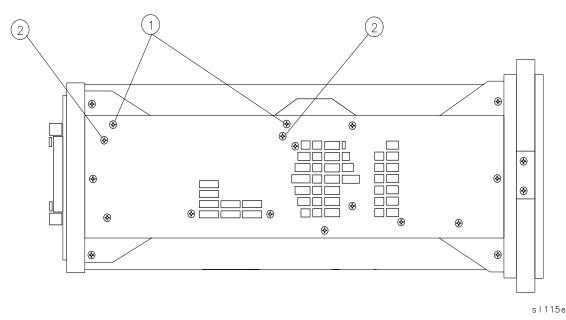

| Figure 3-26 . A14 and A15 Assembly Removal                         | 207 |

| Figure 3-27 . A14 and A15 Assembly Cables                          | 209 |

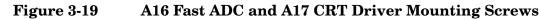

| Figure 3-28 . A16 and A17 Mounting Screws                          | 211 |

| Figure 3-29 . A16 Cable Routing                                    | 212 |

| Figure 3-30 . Main Deck Screws                                     | 217 |

| Figure 3-31 . A6 Power Supply Cover                                | 219 |

| Figure 3-32. W3 Dress and Connection to A6 Power Supply            | 222 |

| Figure 3-33 . Line-Switch Mounting Screw and Cable Dress           | 224 |

| Figure 3-34 . W3 Cable Connector                                   |     |

| Figure 3-35 . Side Frame Mounting Screws                           | 227 |

| Figure 3-36 . A21 OCXO Mounting Screws                             | 231 |

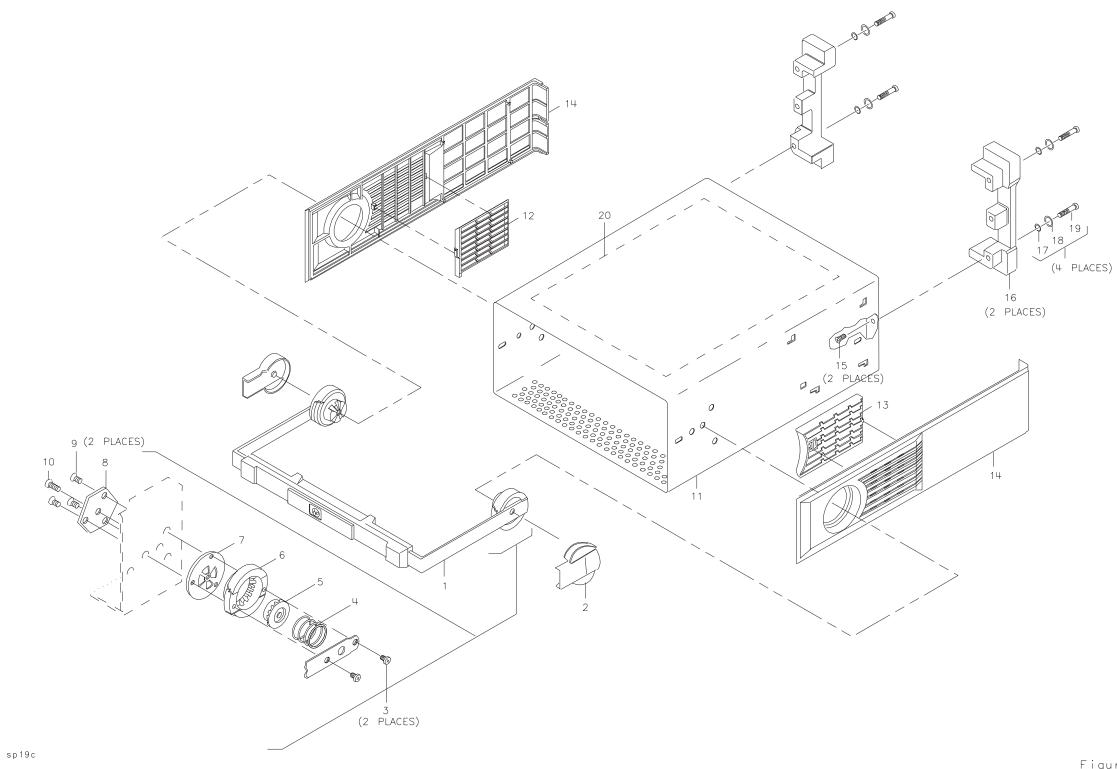

| Figure 4-1 . Parts Identification, Assembly Mounting               | 253 |

| Figure 4-2 . Parts Identification, Cover Assembly                  | 261 |

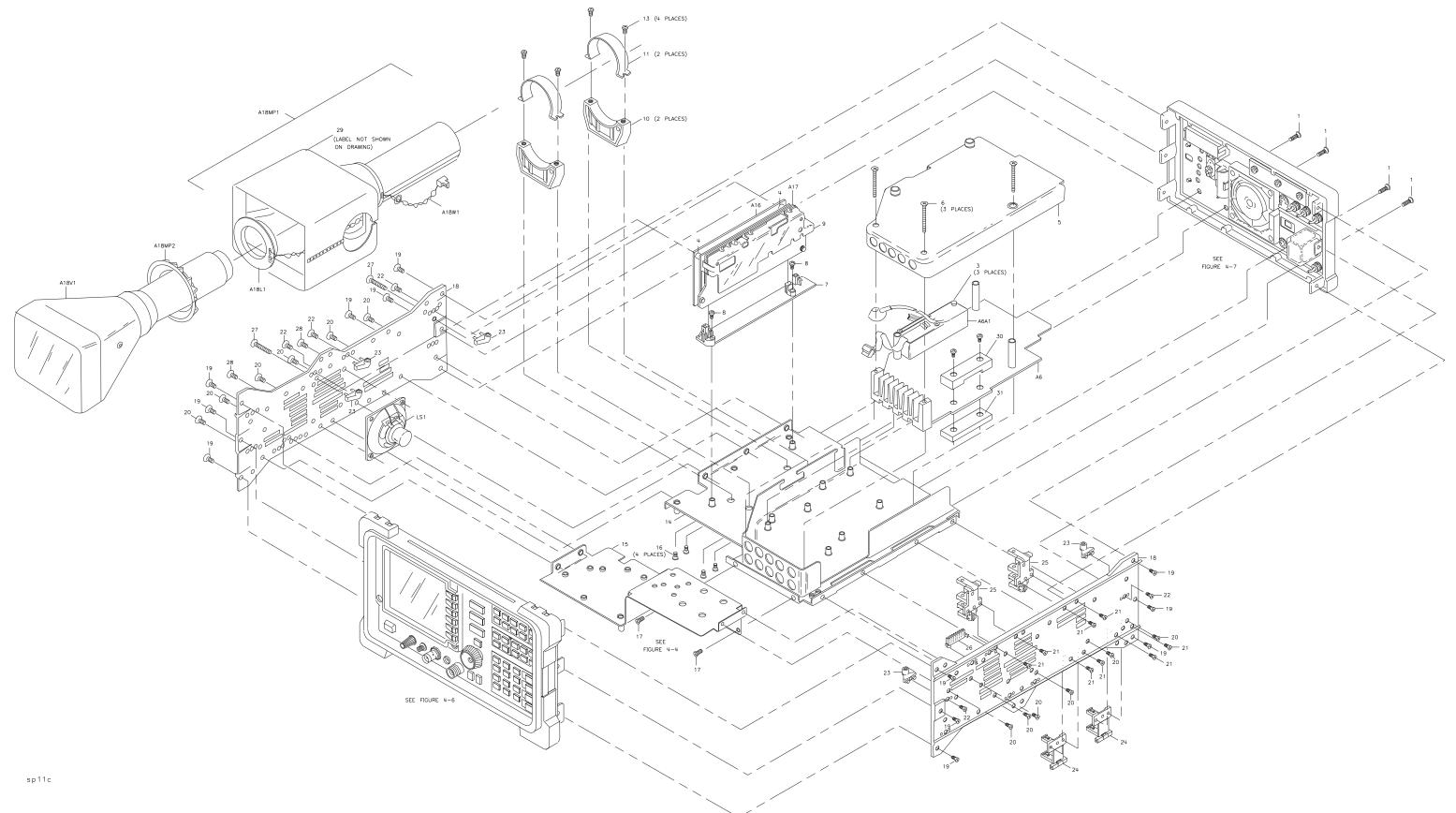

| Figure 4-3 . Parts Identification, Main Chassis (8561E and 8563E)  | 263 |

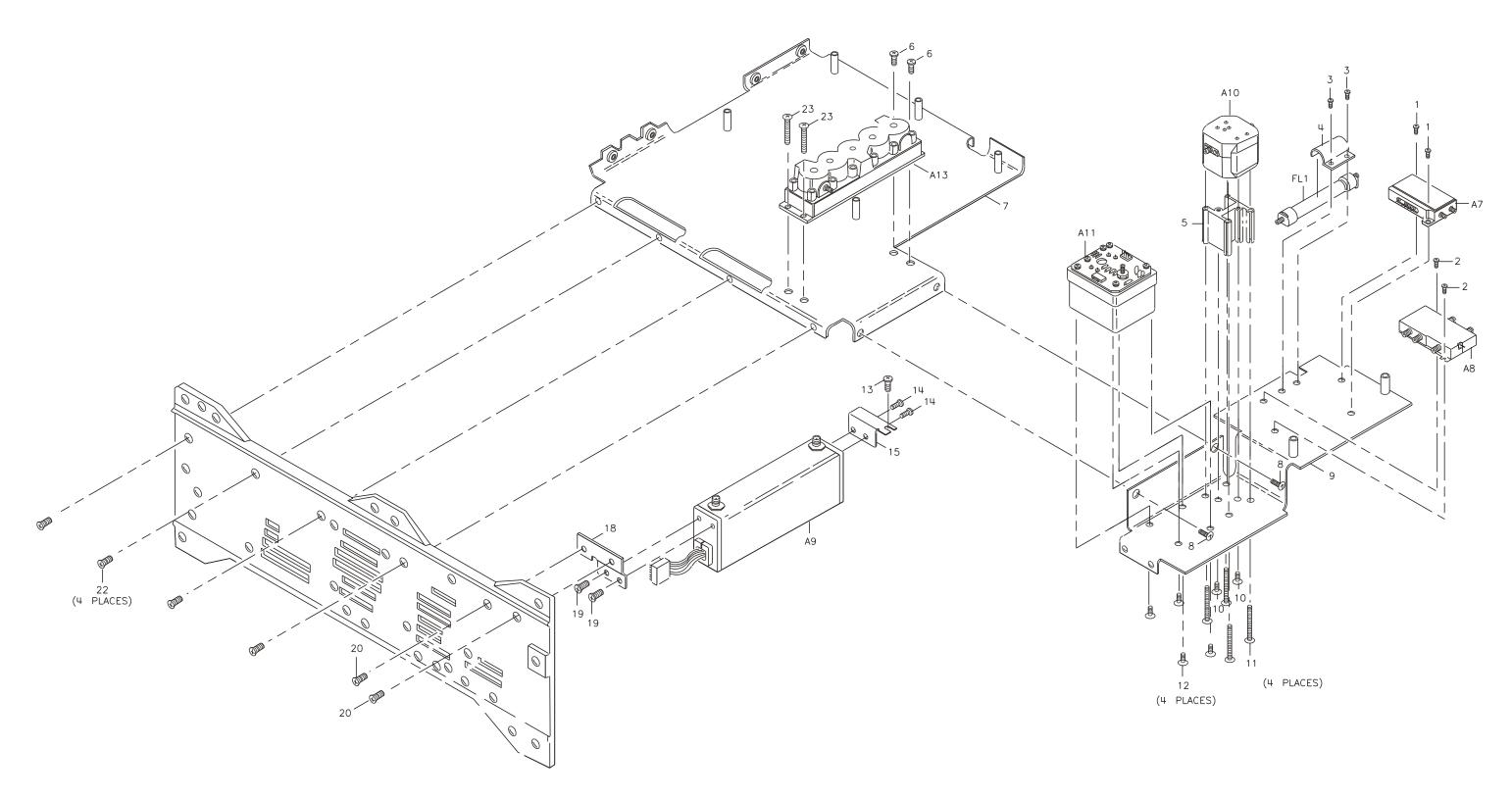

| Figure 4-4 . Parts Identification, RF Section (8561E/EC Only)      | 265 |

| Figure 4-5 . Parts Identification, RF Section (8563E/EC Only)      | 267 |

| Figure 4-6 . Parts Identification, Front Frame (8561E and 8563E)   | 269 |

| Figure 4-7 . Parts Identification, Rear Frame (8561E and 8563E)    | 271 |

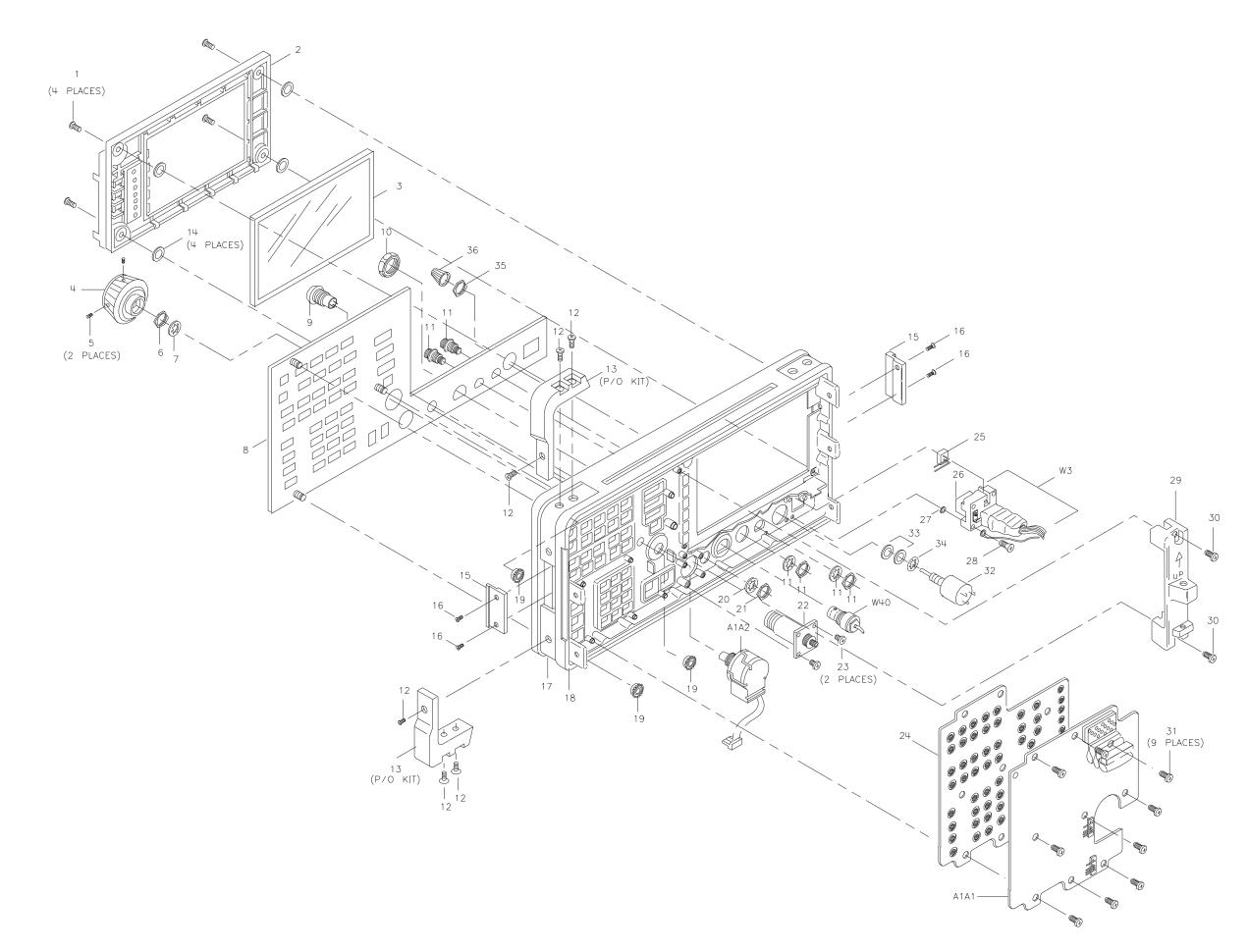

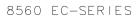

| Figure 4-8 . Parts Identification, Chassis (8561EC and 8563EC)     | 273 |

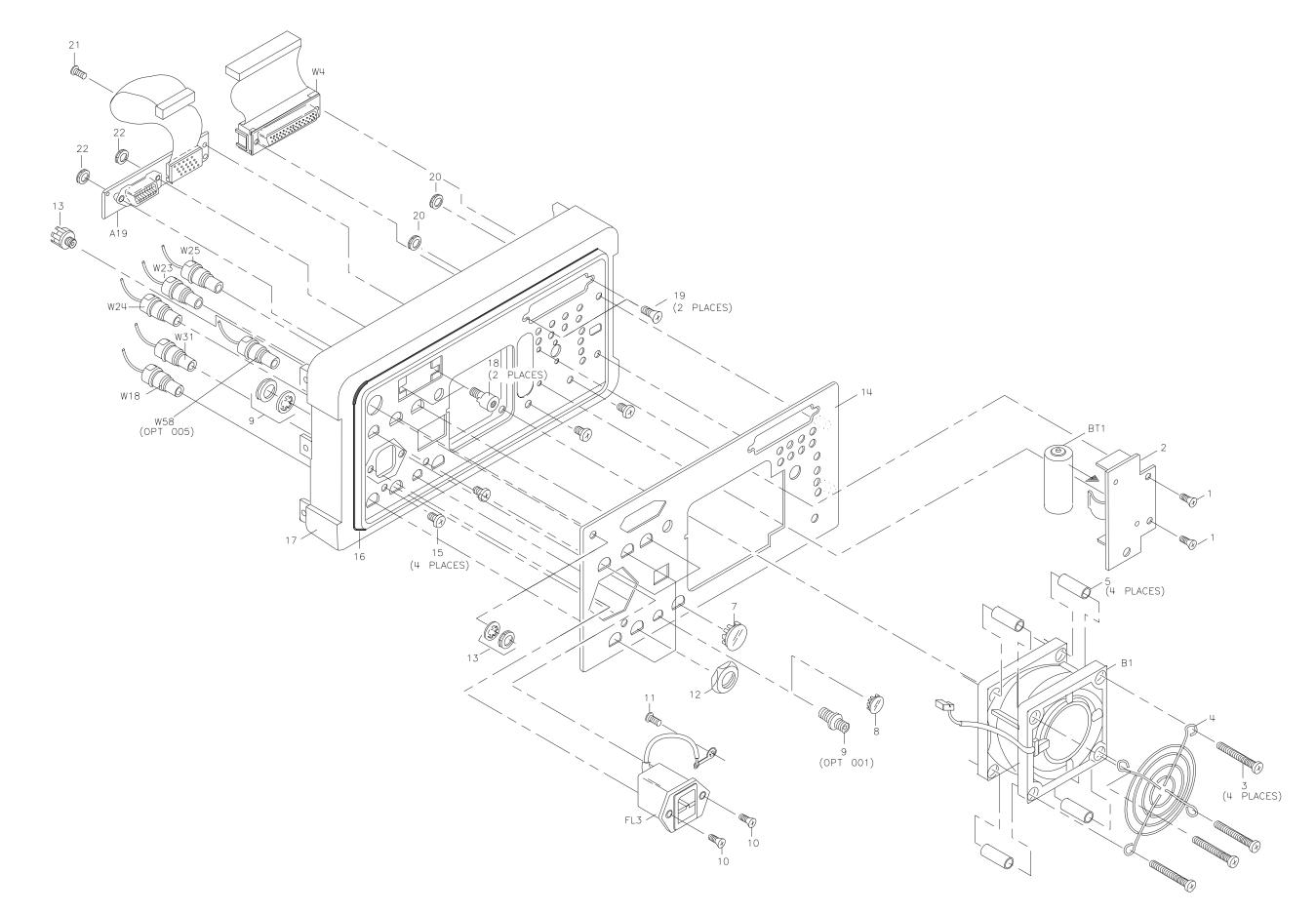

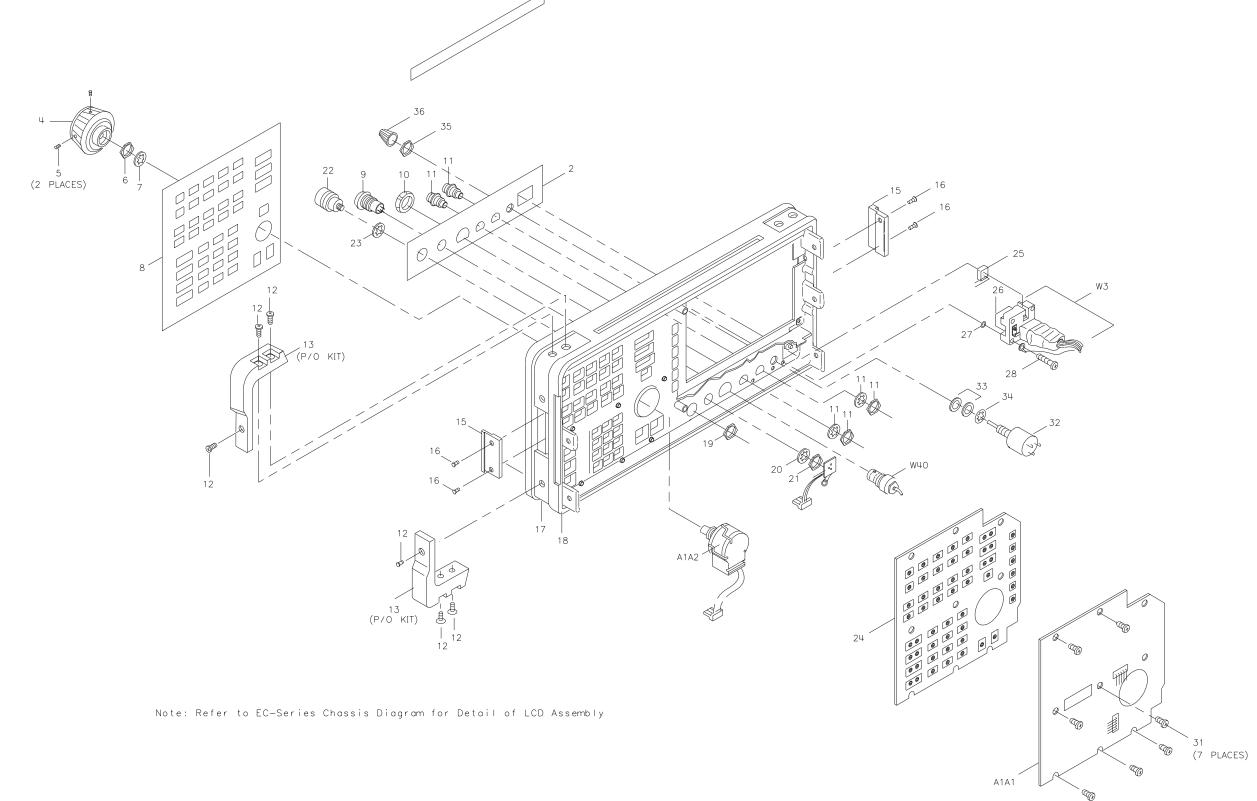

| Figure 4-9 . Parts Identification, Front Frame (8561EC and 8563EC) |     |

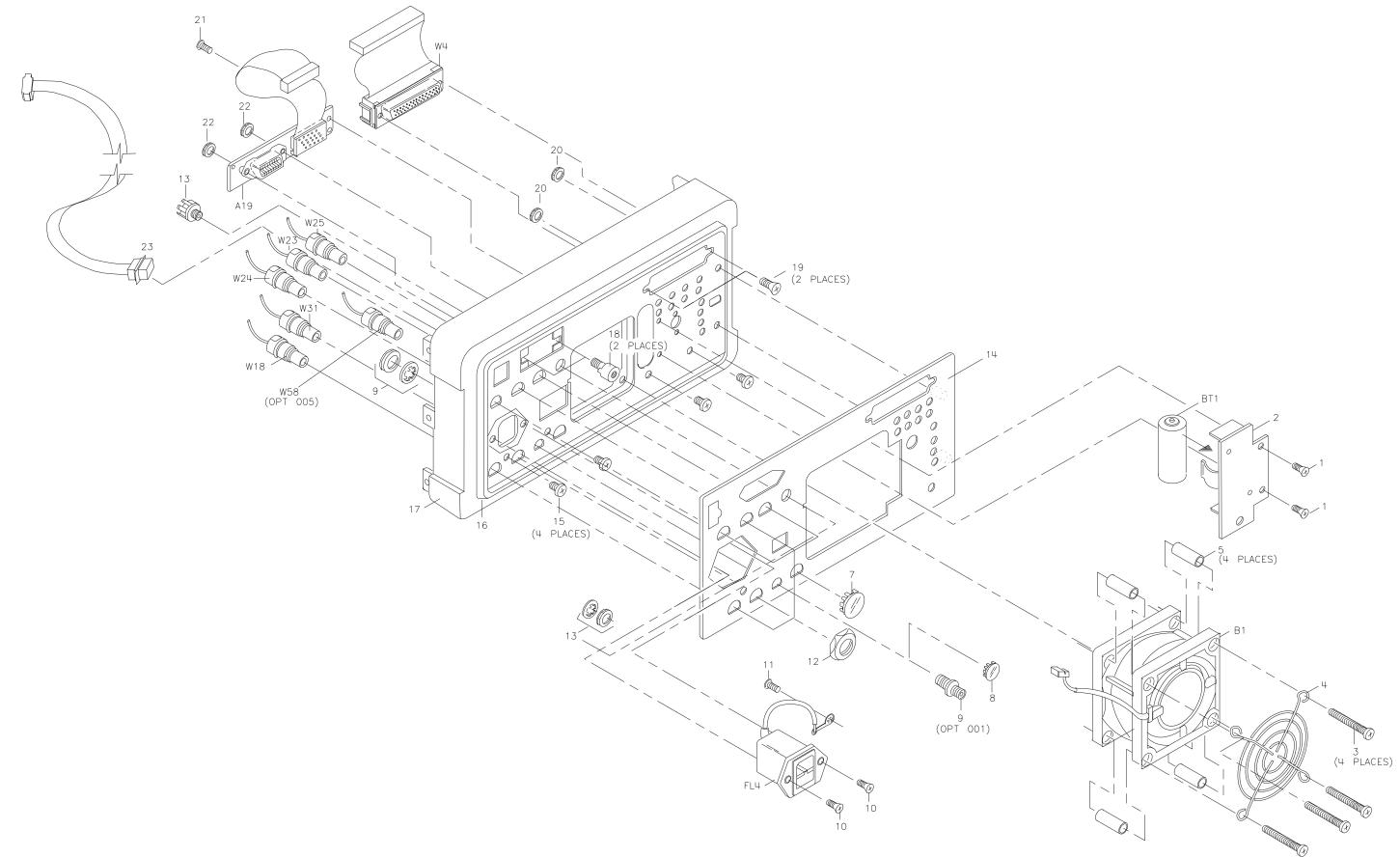

| Figure 4-10 . Parts Identification, Rear Frame (8561EC and 8563EC) | 277 |

| Figure 5-1 . Hinged Assemblies                                     |     |

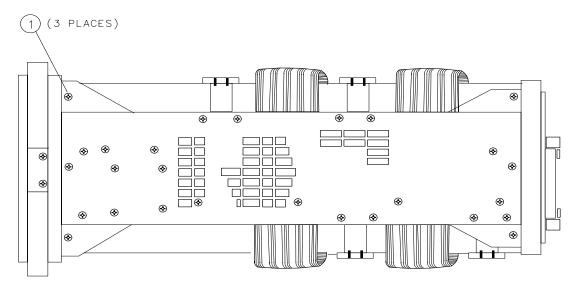

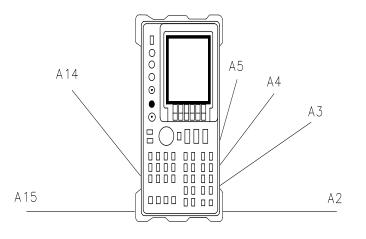

| Figure 5-2. Top View (A2 and A3 unfolded) – EC-Series              | 284 |

| Figure 5-3. Top View (A2, A3, A4, and A5 Unfolded) – EC-Series           | . 285 |

|--------------------------------------------------------------------------|-------|

| Figure 5-4. Top View (A2 Unfolded) – E-Series                            |       |

| Figure 5-5. Top View (A2 and A3 Unfolded) – E-Series.                    | . 287 |

| Figure 5-6. Top View (A2, A3, A4, and A5 Unfolded) – E-Series            | . 288 |

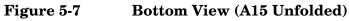

| Figure 5-7 . Bottom View (A15 Unfolded)                                  |       |

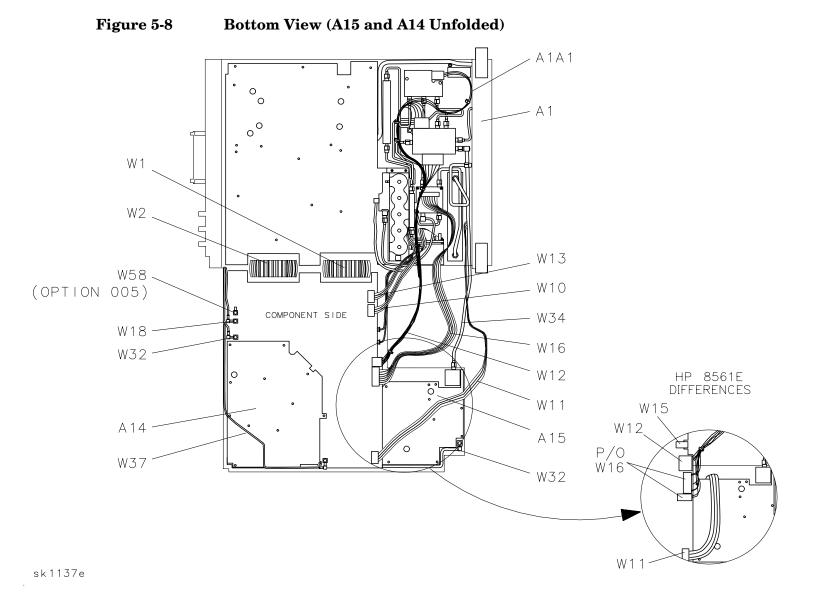

| Figure 5-8. Bottom View (A15 and A14 Unfolded)                           | . 290 |

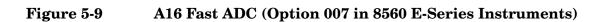

| Figure 5-9 . A16 Fast ADC (Option 007 in 8560 E-Series Instruments)      | . 291 |

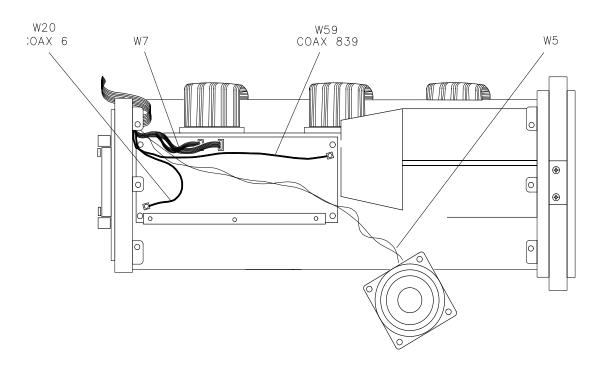

| Figure 5-10 . 8561E/EC Front End                                         |       |

| Figure 5-11 . 8563E/EC Front End                                         | . 293 |

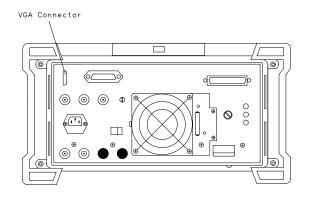

| Figure 5-12 . Rear View EC-Series                                        | . 294 |

| Figure 5-13 . Rear View E-Series                                         |       |

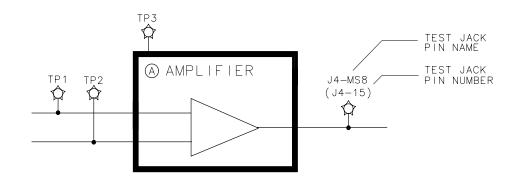

| Figure 6-1 . Assembly Test Points                                        | . 298 |

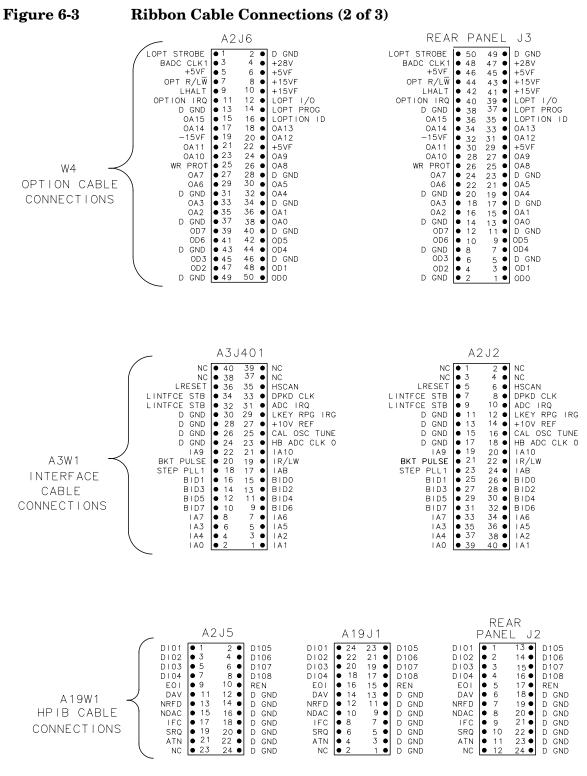

| Figure 6-2 . Ribbon Cable Connections (1 of 3)                           | . 299 |

| Figure 6-3 . Ribbon Cable Connections (2 of 3)                           | . 300 |

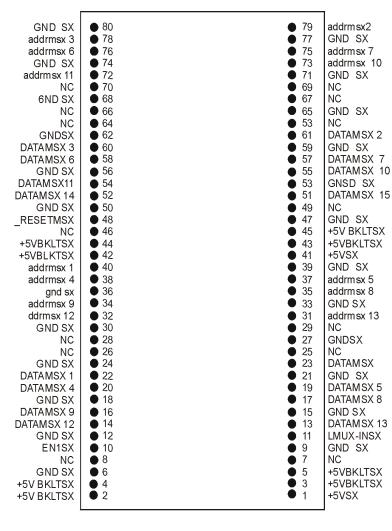

| Figure 6-4 . Ribbon Cable Connections (3 of 3) - EC-Series Only          | . 301 |

| Figure 6-5 . Service Cal Data Menu                                       | . 302 |

| Figure 6-6 . Functional Sections                                         | . 347 |

| Figure 6-7 . Phase Lock Loops                                            | . 355 |

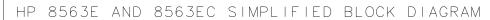

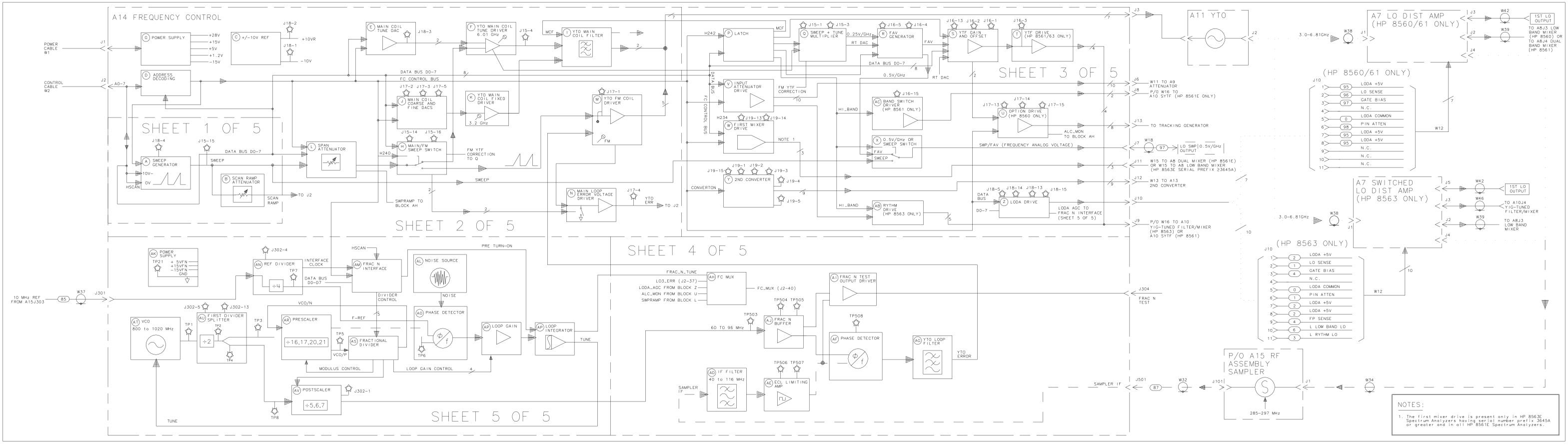

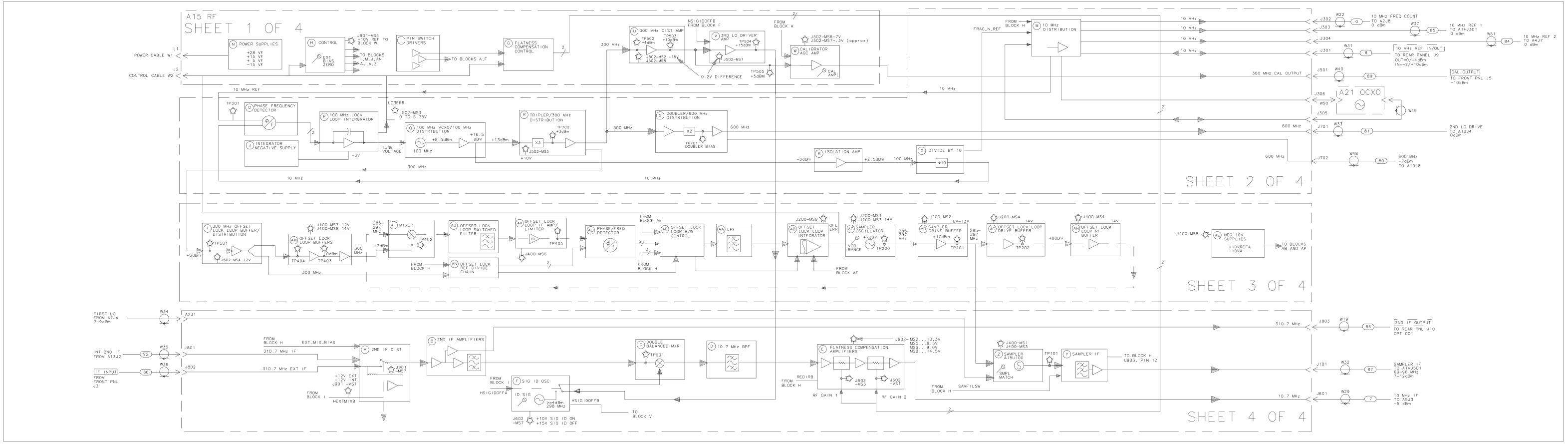

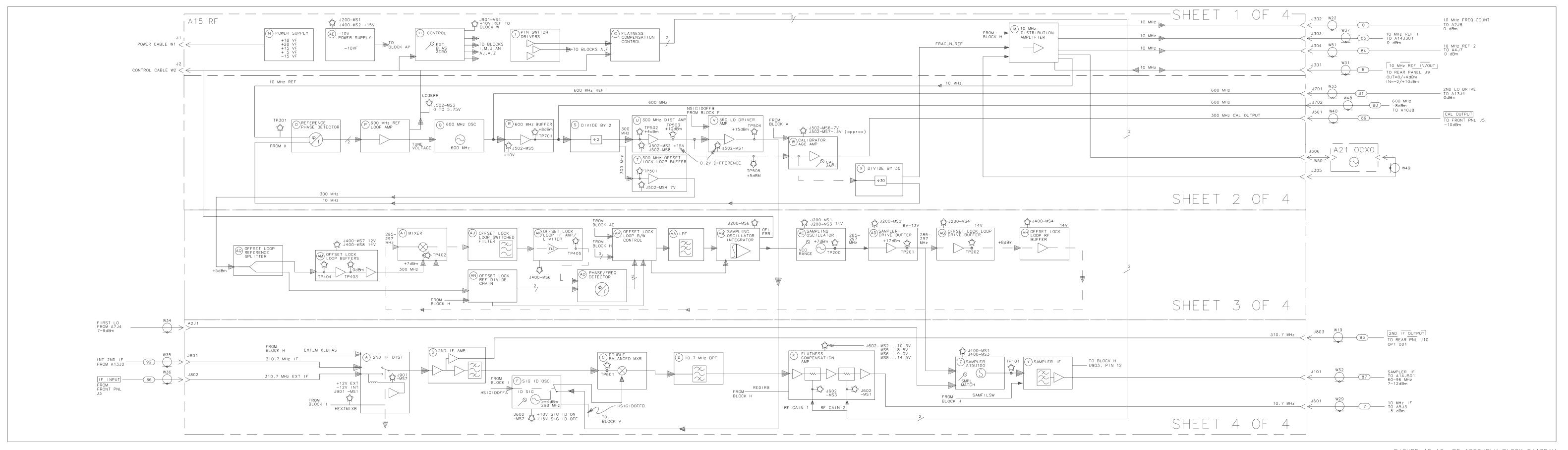

| Figure 6-8 . Simplified 61E/EC Block Diagram                             | . 361 |

| Figure 6-9 . Simplified 63E/EC Block Diagram                             |       |

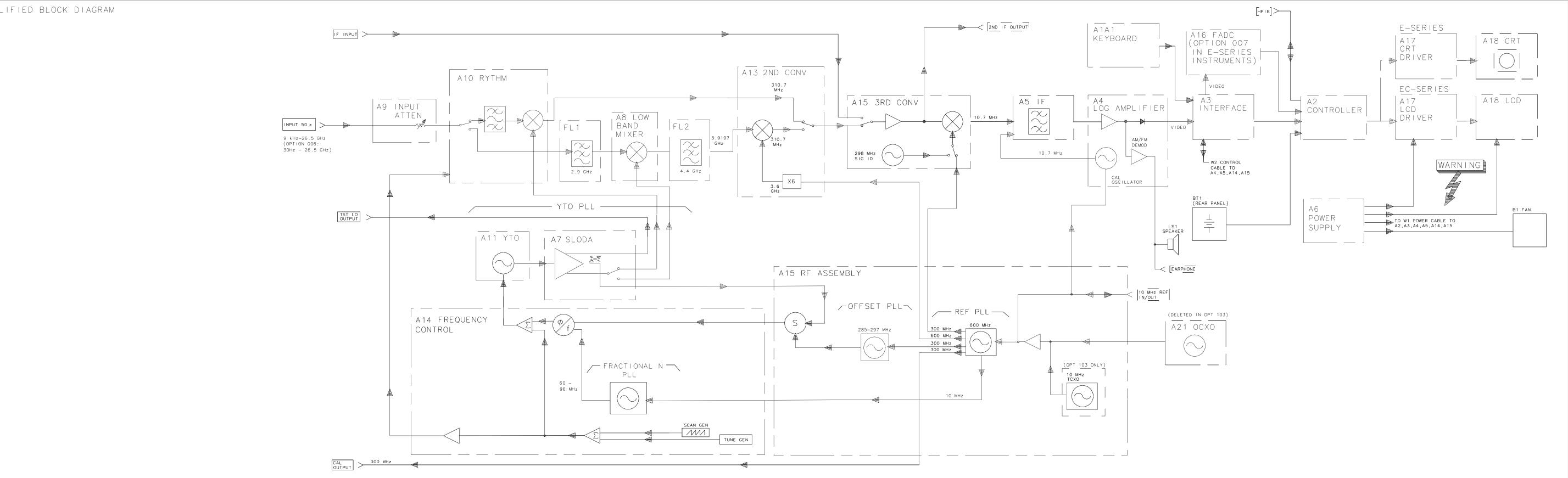

| Figure 6-10 . Overall Block Diagram (1 of 7)                             |       |

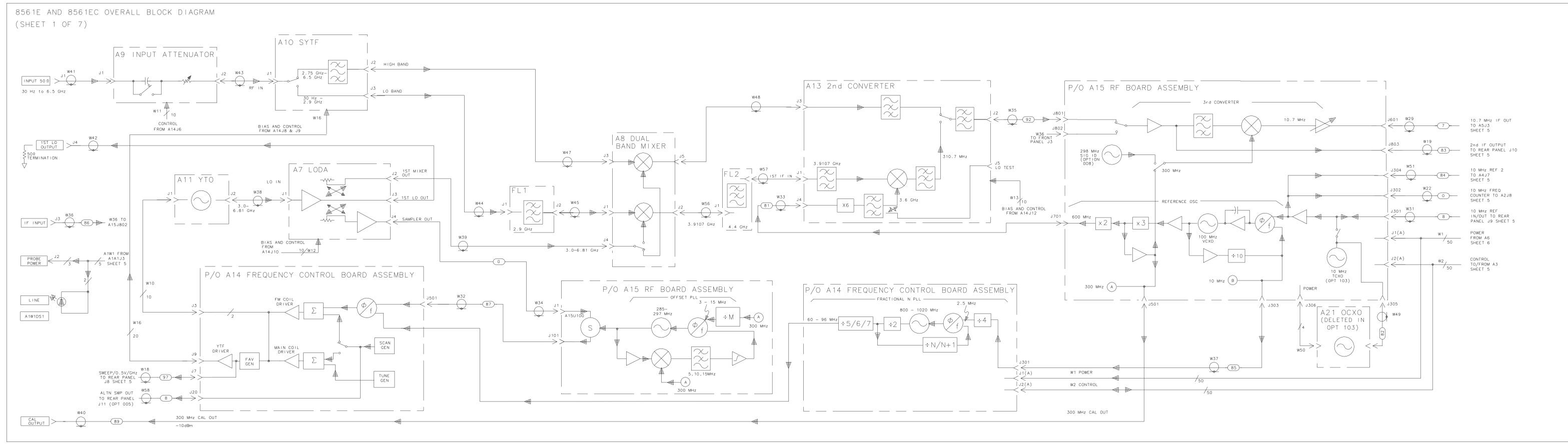

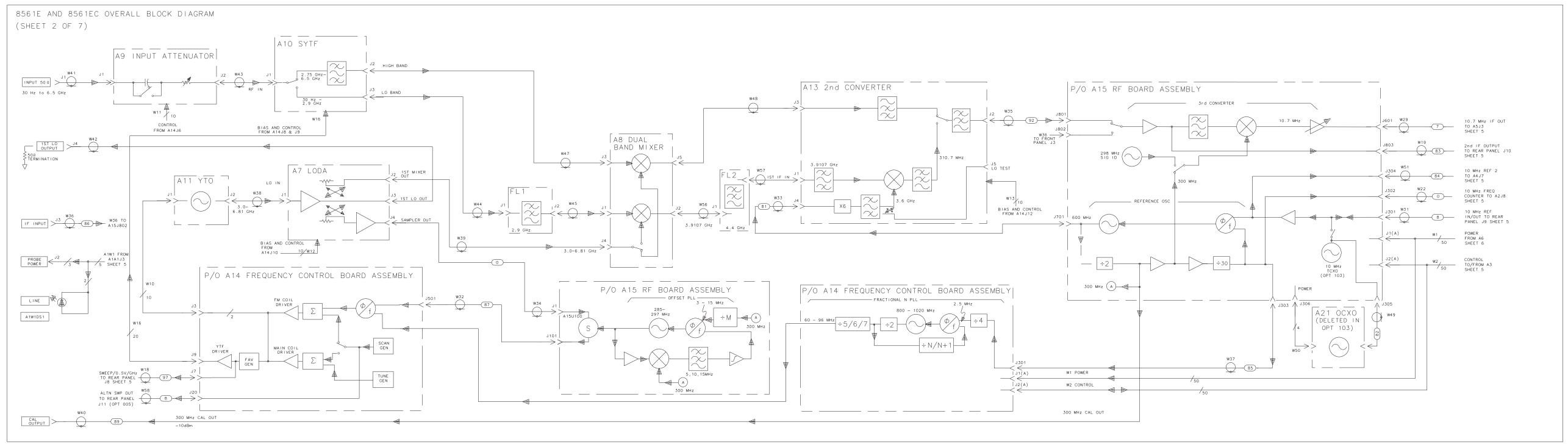

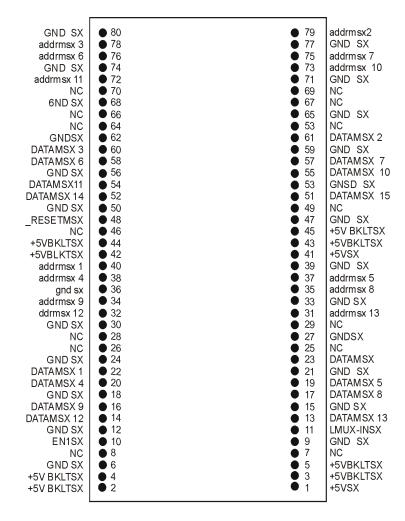

| Figure 6-10 . Overall Block Diagram (2 of 7)                             |       |

| Figure 6-10 . Overall Block Diagram (3 of 7)                             |       |

| Figure 6-10 . Overall Block Diagram (4 of 7)                             |       |

| Figure 6-10 . Overall Block Diagram (5 of 7)                             |       |

| Figure 6-10 . Overall Block Diagram (6 of 7)                             |       |

| Figure 6-10 . Overall Block Diagram (7 of 7)                             |       |

| Figure 7-1 . A3 Test Connectors                                          |       |

| Figure 7-2 . A3 Interface Assembly Block Diagram                         |       |

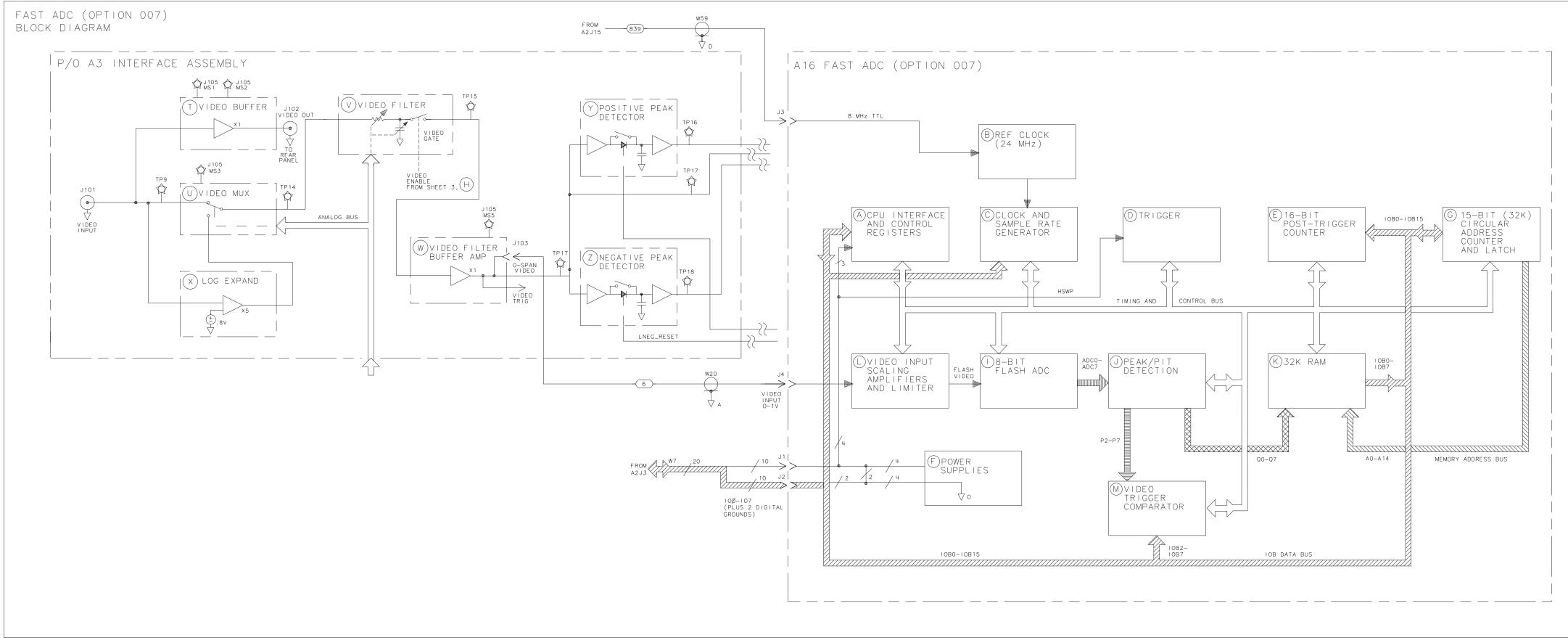

| Figure 7-3 . Fast ADC Block Diagram (Option 007 in E-Series Instruments) |       |

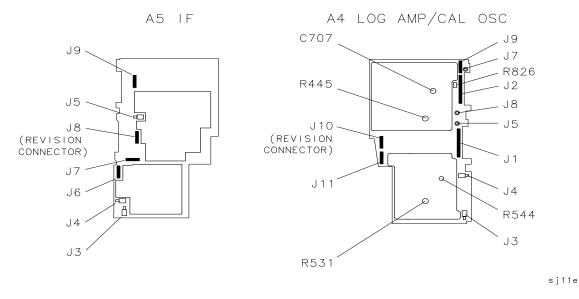

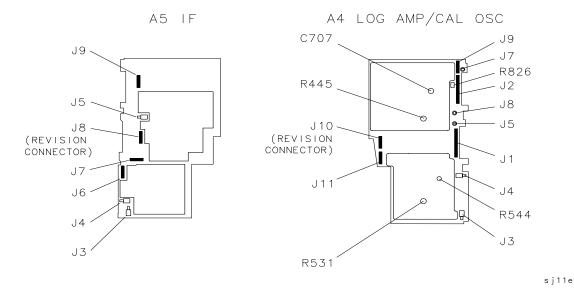

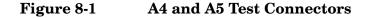

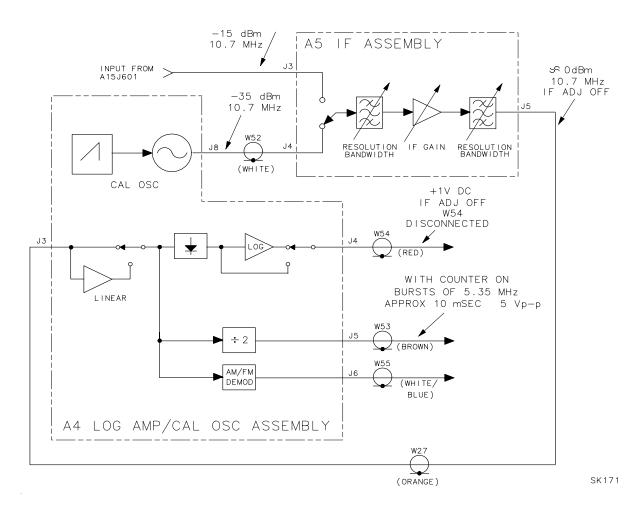

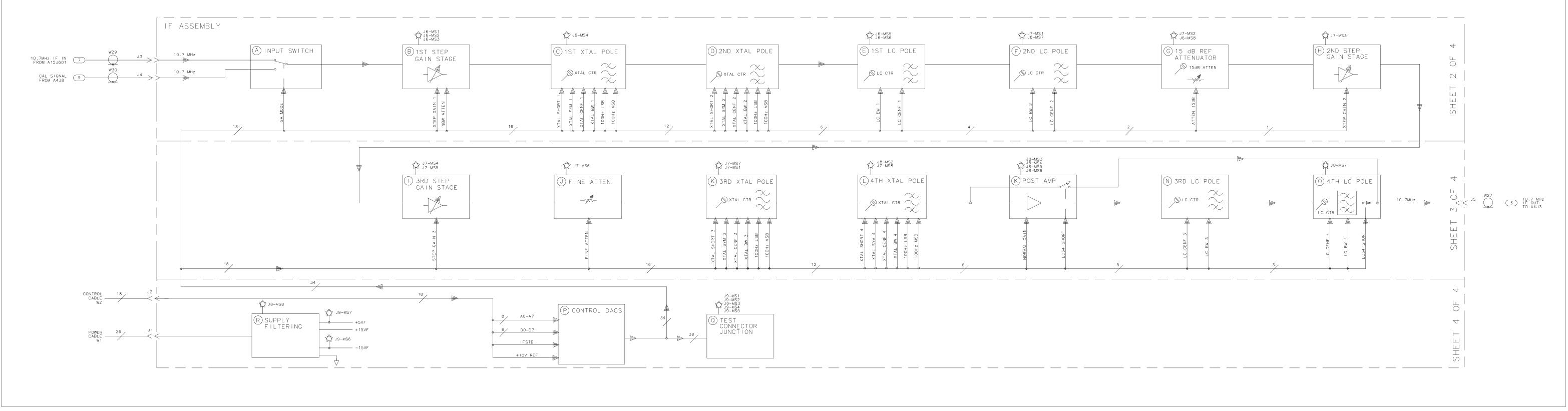

| Figure 8-1 . A4 and A5 Test Connectors                                   |       |

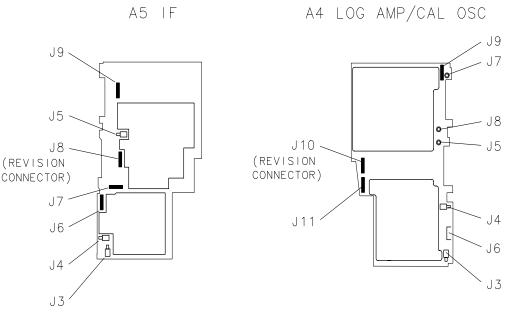

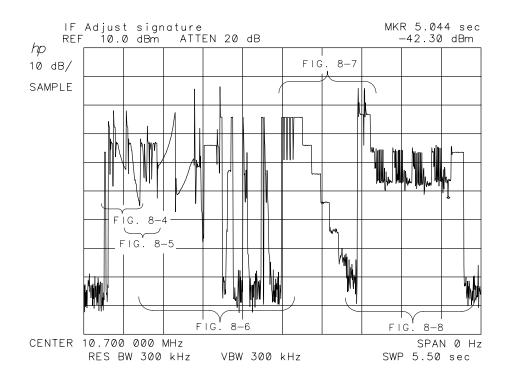

| Figure 8-2 . IF Section Troubleshooting with the TAM                     |       |

| Figure 8-3 . IF Adjust Signature                                         |       |

| Figure 8-4 . Detailed IF Adjust Signature (1)                            |       |

| Figure 8-5 . Detailed IF Adjust Signature (2)                            |       |

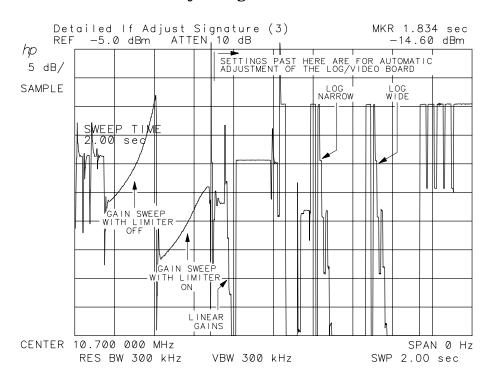

| Figure 8-6 . Detailed IF Adjust Signature (3)                            |       |

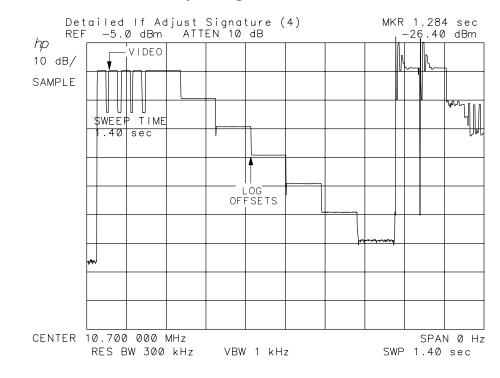

| Figure 8-7 . Detailed IF Adjust Signature (4)                            |       |

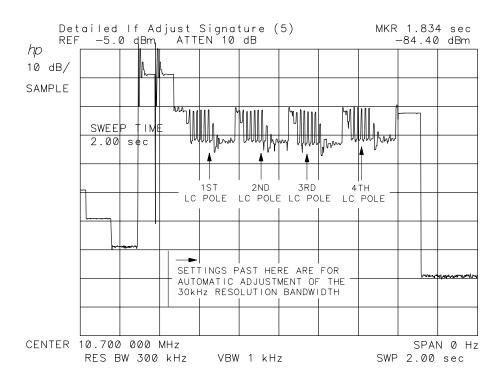

| Figure 8-8 . Detailed IF Adjust Signature (5)                            |       |

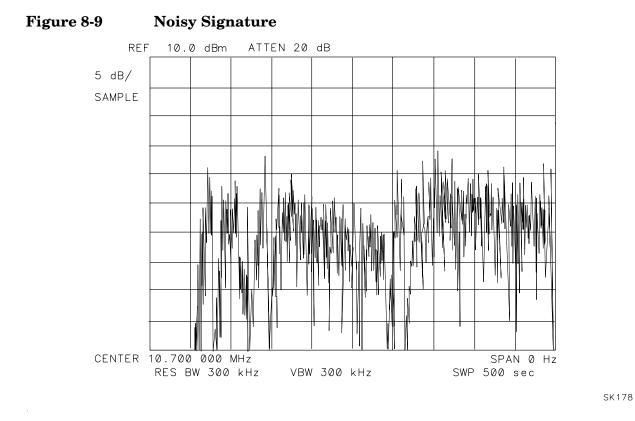

| Figure 8-9. Noisy Signature                                              |       |

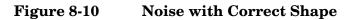

| Figure 8-10. Noise with Correct Shape                                    |       |

| Figure 8-11 . Region B Amplitude Variation                               |       |

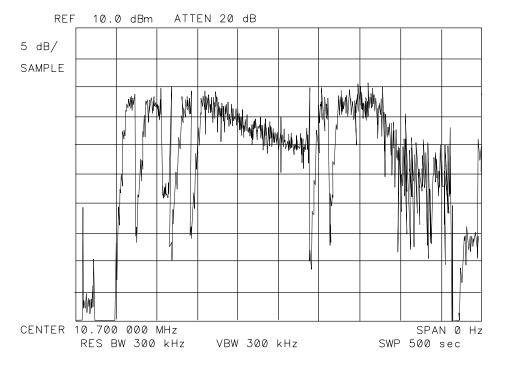

| Figure 8-12 . Region B Amplitude Offset                                  |       |

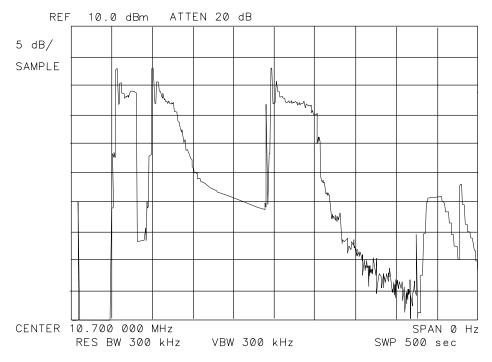

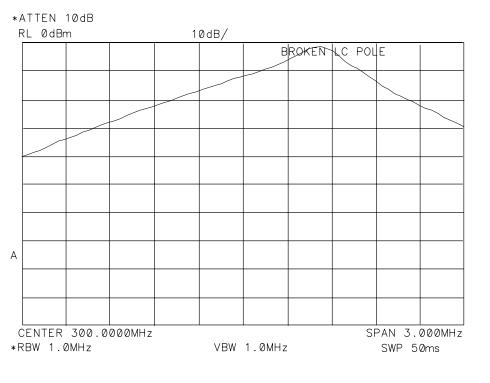

| Figure 8-13 . Faulty Crystal Short                                       |       |

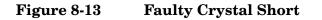

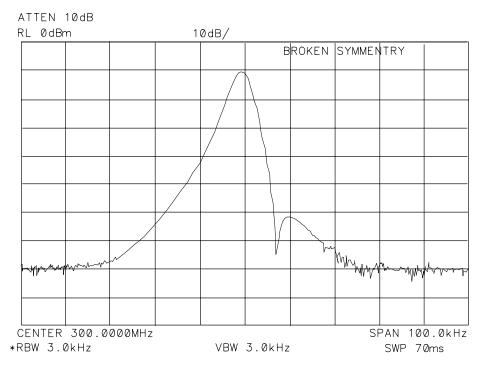

| Figure 8-14 . Faulty LC Pole                                             |       |

| Figure 8-15 . Faulty Crystal Symmetry                                    | . 468 |

## Figures

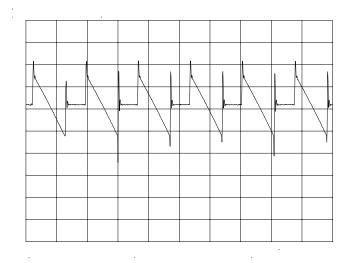

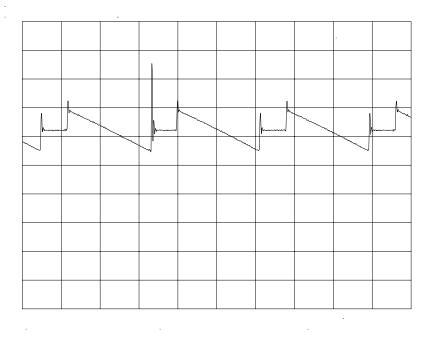

| Figure 8-16 . Output Waveform, 10 kHz Resolution Bandwidth                        | 474 |

|-----------------------------------------------------------------------------------|-----|

| Figure 8-17 . Output Waveform, 3 kHz Resolution Bandwidth                         | 475 |

| Figure 8-18 . Output Waveform, 1 kHz Resolution Bandwidth                         | 475 |

| Figure 8-19 . Output Waveform, 300 Hz Resolution Bandwidth                        | 476 |

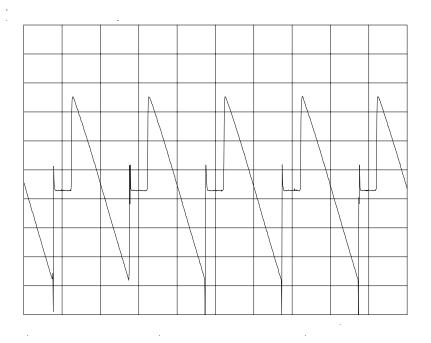

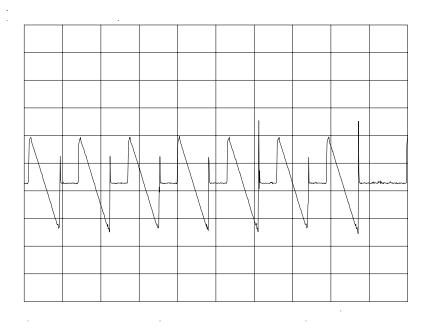

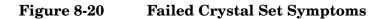

| Figure 8-20 . Failed Crystal Set Symptoms                                         |     |

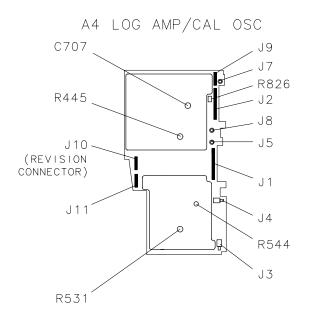

| Figure 8-21 . A4 Log Amplifier/Cal Oscillator Block Diagram (1 of 2)              | 479 |

| Figure 8-21 . A4 Log Amplifier/Cal Oscillator Block Diagram (2 of 2)              |     |

| Figure 8-22 . A5 IF Assembly Block Diagram                                        | 483 |

| Figure 9-1 . A2 Test Connectors                                                   | 488 |

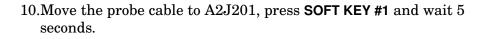

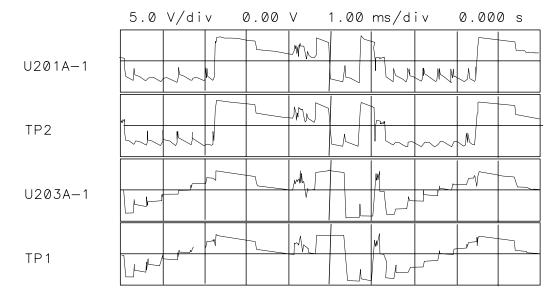

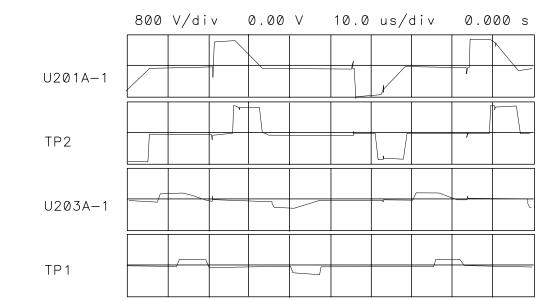

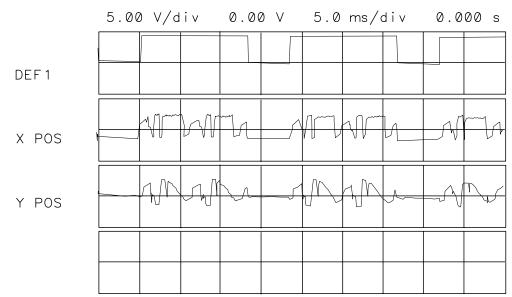

| Figure 9-2 . Line Generator Output Waveforms                                      | 492 |

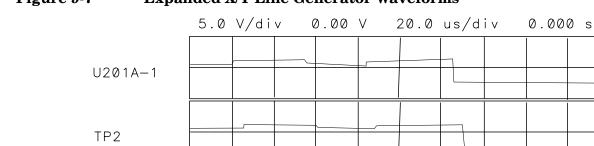

| Figure 9-3 . Blanking Waveforms                                                   |     |

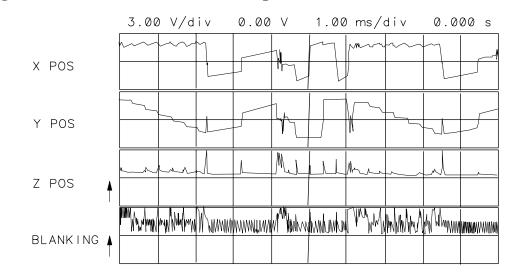

| Figure 9-4 . Expanded Blanking Waveforms                                          |     |

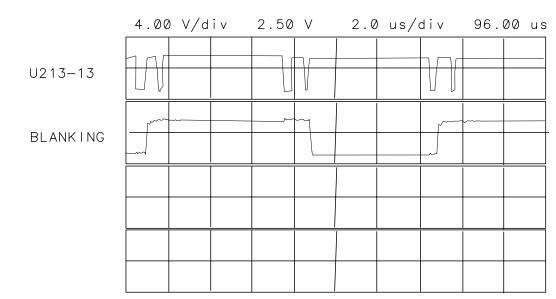

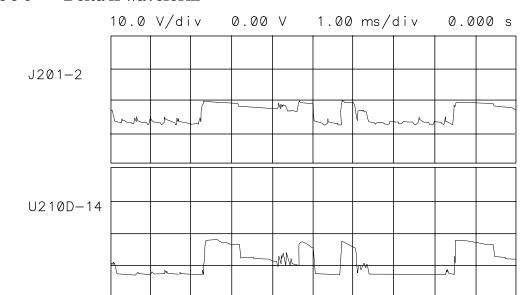

| Figure 9-5 . Switch Driver Waveform LCHAR                                         |     |

| Figure 9-6 . Distorted X/Y Line Generator Waveforms                               |     |

| Figure 9-7 . Expanded X/Y Line Generator Waveforms                                |     |

| Figure 9-8 . Normal X/Y Line Generator Waveforms                                  |     |

| Figure 9-9 . Delta X Waveform                                                     |     |

| Figure 9-10 . Delta Y Waveform                                                    |     |

| Figure 9-11 . DEF1 Synchronization                                                |     |

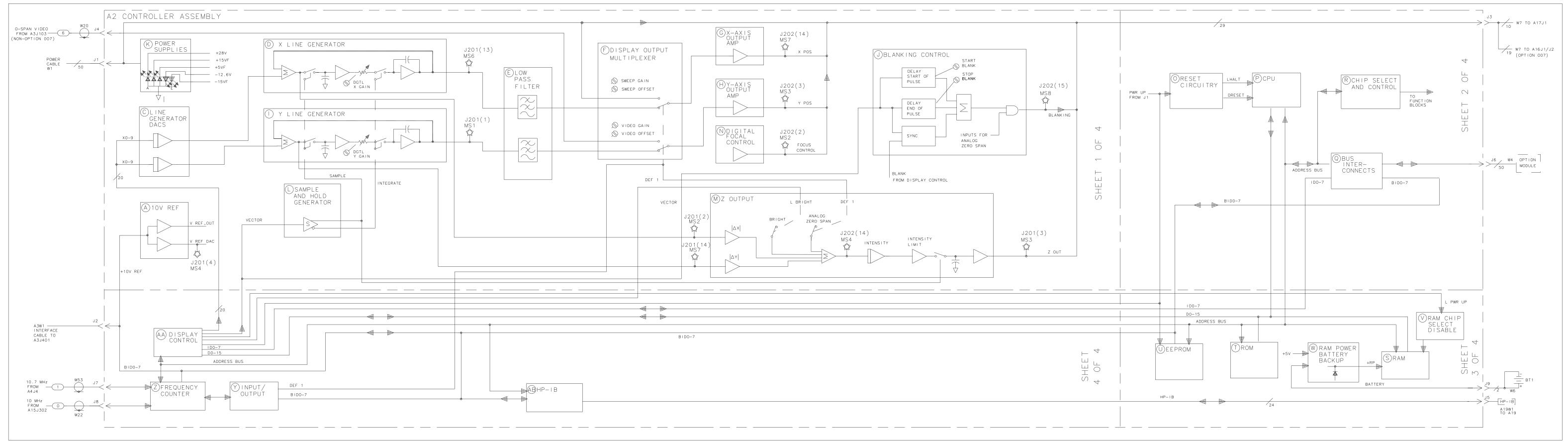

| Figure 9-12 . A2 Controller Block Diagram (E-Series)                              |     |

| Figure 9-13 . A2 Controller Block Diagram (EC-Series)                             |     |

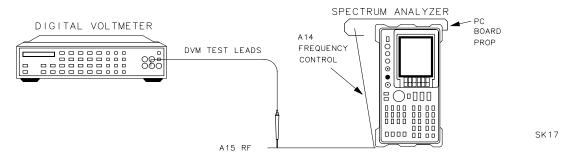

| Figure 10-1 . A14 and A15 Test Connectors                                         |     |

| Figure 10-2 . TAM Connector Pin Locations                                         |     |

| Figure 10-3 . YTO Loop Test Setup                                                 |     |

| Figure 10-4 . Sampler and Sampling Oscillator Test Setup                          |     |

| Figure 10-5 . PLL Locked at Wrong Frequency                                       |     |

| Figure 10-6 . Unlocked PLL                                                        |     |

| Figure 10-7 . Troubleshooting an Unlocked YTO PLL                                 |     |

| Figure 10-8 . VCO Bias Voltages                                                   |     |

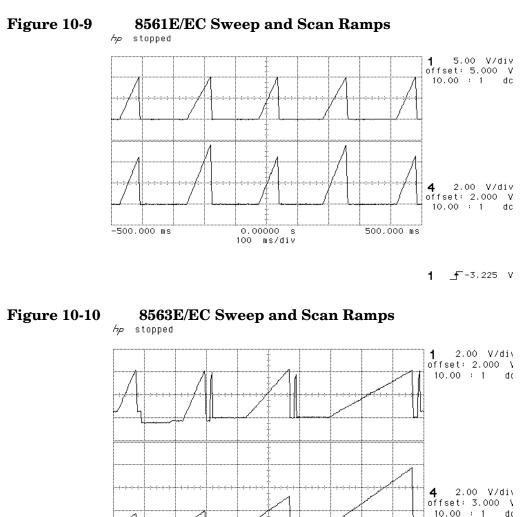

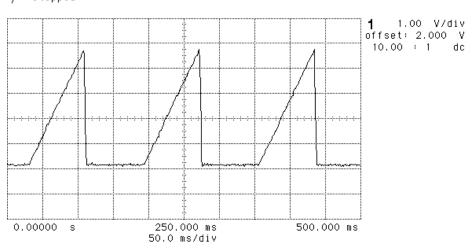

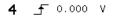

| Figure 10-9 . 8561E/EC Sweep and Scan Ramps                                       |     |

| Figure 10-10. 8563E/EC Sweep and Scan Ramps                                       |     |

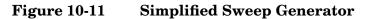

| Figure 10-11 . Simplified Sweep Generator                                         |     |

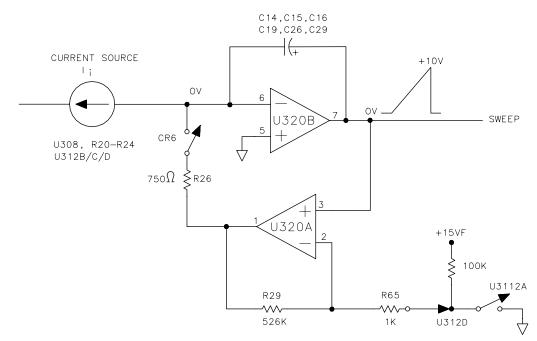

| Figure 10-12 . Simplified Sweep Generator during Retrace                          |     |

| Figure 10-13 . Simplified Synthesizer Section                                     |     |

| Figure 10-14 . Simplified A14 Assembly Block Diagram                              |     |

| Figure 10-15 . Simplified A15 Assembly Block Diagram                              |     |

| Figure 10-16 . Frequency Control Block Diagram                                    |     |

| Figure 10-17 . RF Assembly Block Diagram                                          |     |

| Figure 10-18 . RF Assembly Block Diagram                                          |     |

| Figure 11-1 . A14 and A15 Test Connectors                                         |     |

| Figure 11-2 . A14J10, Solder Side of A14 (Ignore Pin Numbers on Mating Connector) |     |

| Figure 11-3 . A7 First LO Distribution Amplifier Drive                            |     |

| Figure 11-4 . 8561E/EC Rear-Panel SWP Output                                      |     |

| Figure 11-5 . 8563E/EC Rear-Panel SWP Output                                      |     |

| Figure 11-6 . 8561E/EC Signal at A14J15 Pin 1                                     | 615 |

## Figures

| Figure 11-7 . 8563E/EC Signal at A14J15 Pin 1                          | 616 |

|------------------------------------------------------------------------|-----|

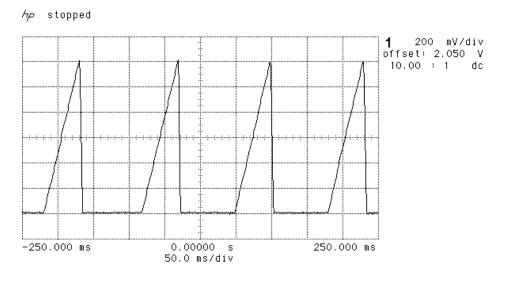

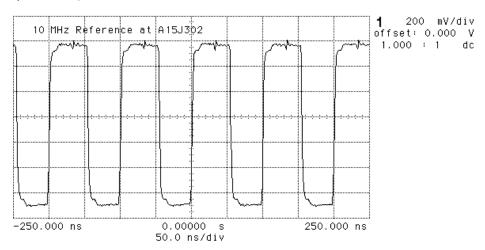

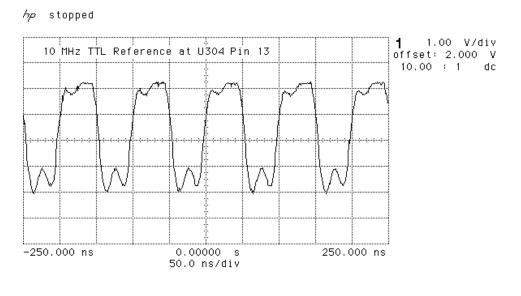

| Figure 11-8. 10 MHz Reference at A15J302                               | 624 |

| Figure 11-9. 10 MHz TTL Reference at U304 Pin 13                       | 625 |

| Figure 11-10.8561E/EC RF Section, Troubleshooting Block Diagram        | 627 |

| Figure 11-11. 8563E/EC RF Section, Troubleshooting Block Diagram       | 629 |

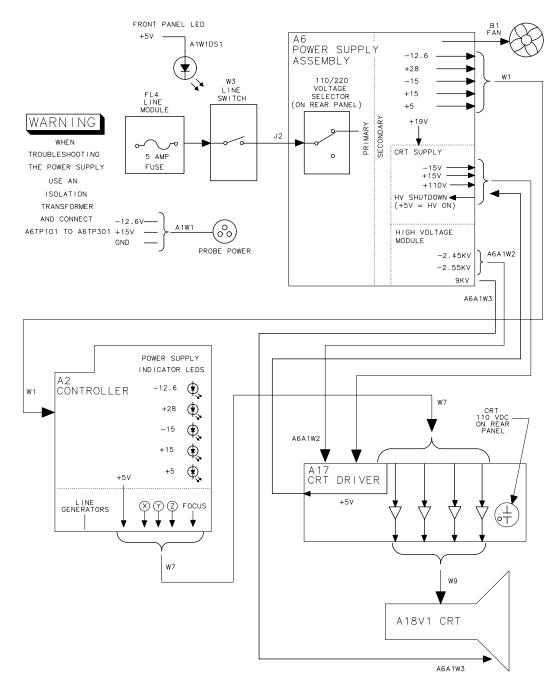

| Figure 12-1 . Simplified Section Block Diagram                         | 633 |

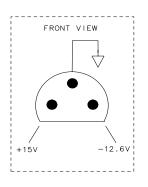

| Figure 12-2 . Probe Power Socket                                       | 635 |

| Figure 12-3. Location of +5V supplies to Inverter Board and Backlights | 637 |

| Figure 12-4 . Power Supply and CRT Block Diagram                       | 639 |

| Figure 12-5 . A17 Test Connector                                       | 640 |

| Figure 12-6 . Probe Power Socket                                       | 643 |

| Figure 12-7 . Simplified Power Supply Block Diagram                    | 652 |

| Figure 12-8 . Buck Regulator Waveform                                  | 656 |

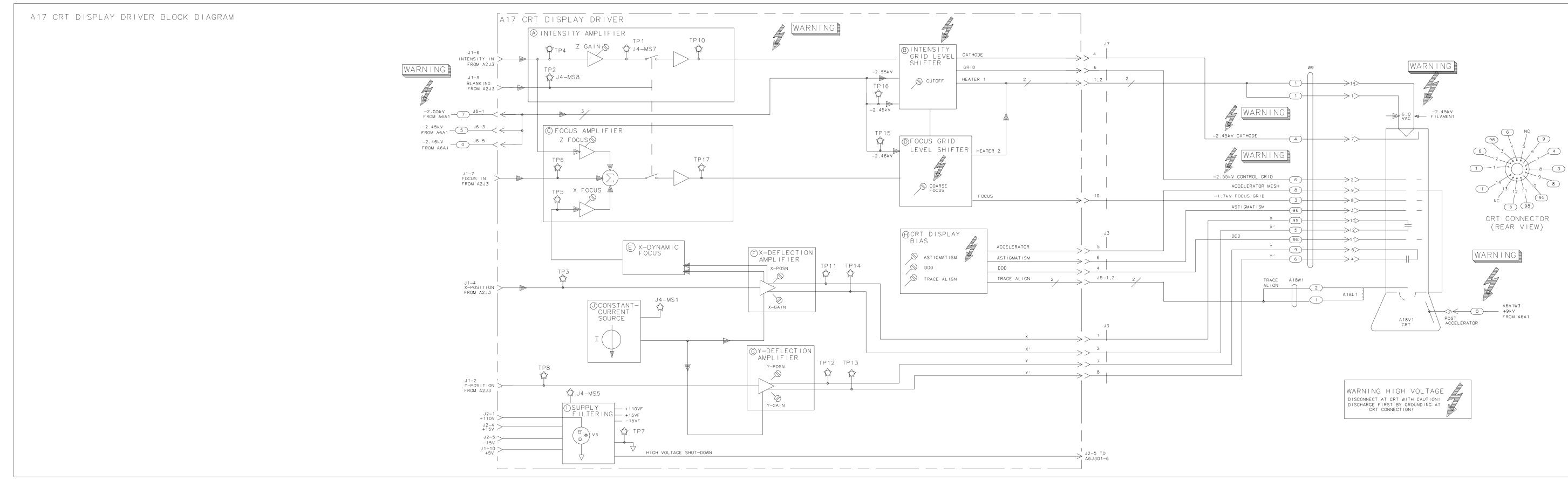

| Figure 12-9 . A17 CRT Driver Block Diagram                             | 663 |

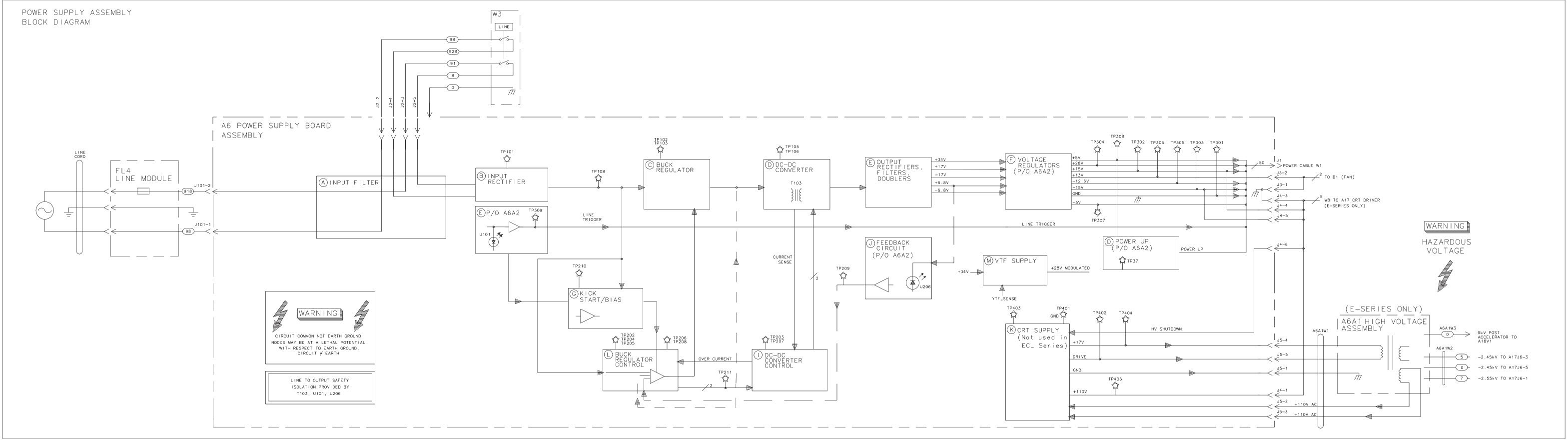

| Figure 12-10 . A6 Power Supply Block Diagram                           |     |

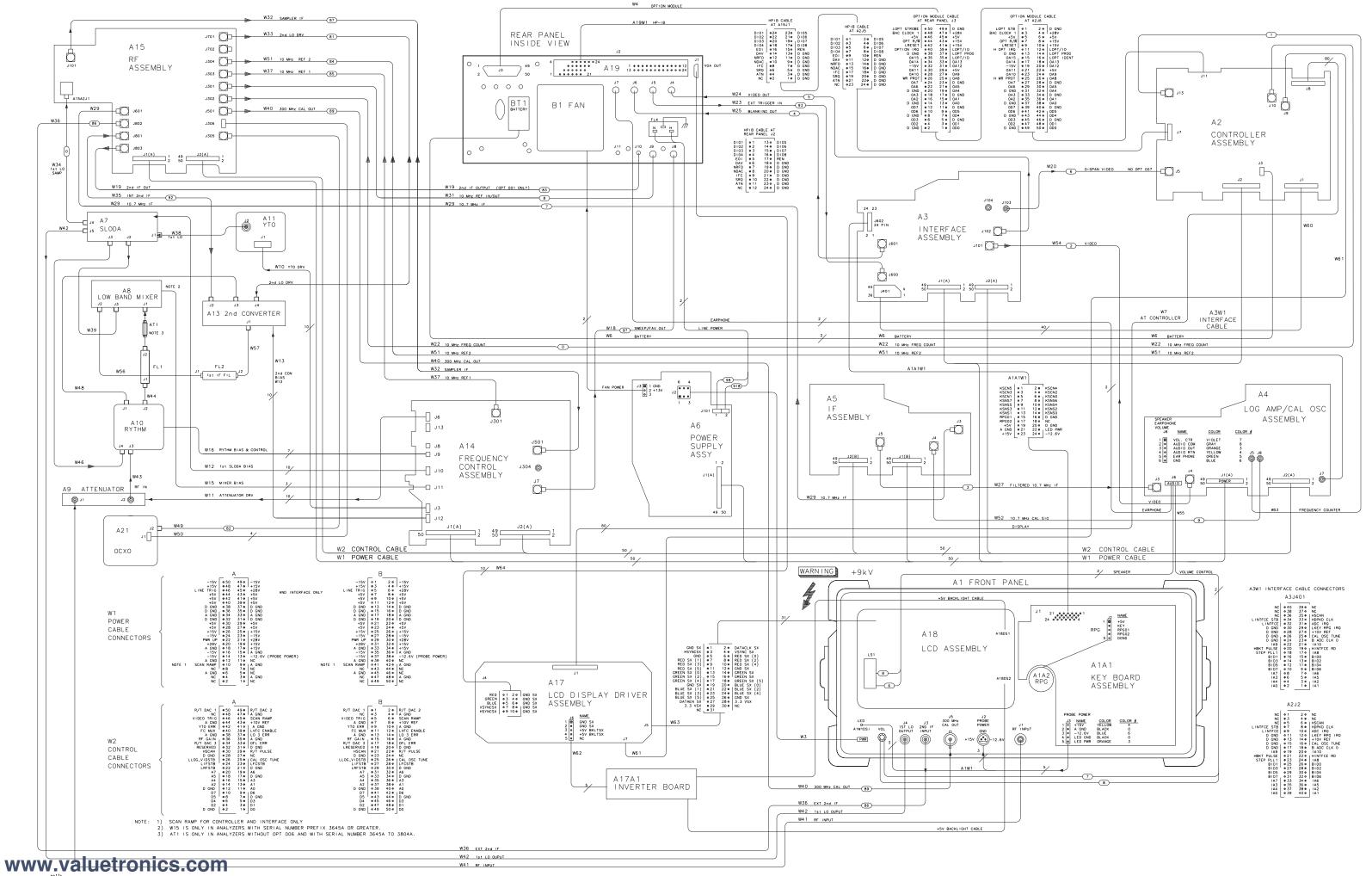

| Figure 13-1 . 8560 EC-Series Interconnect Block Diagram                | 673 |

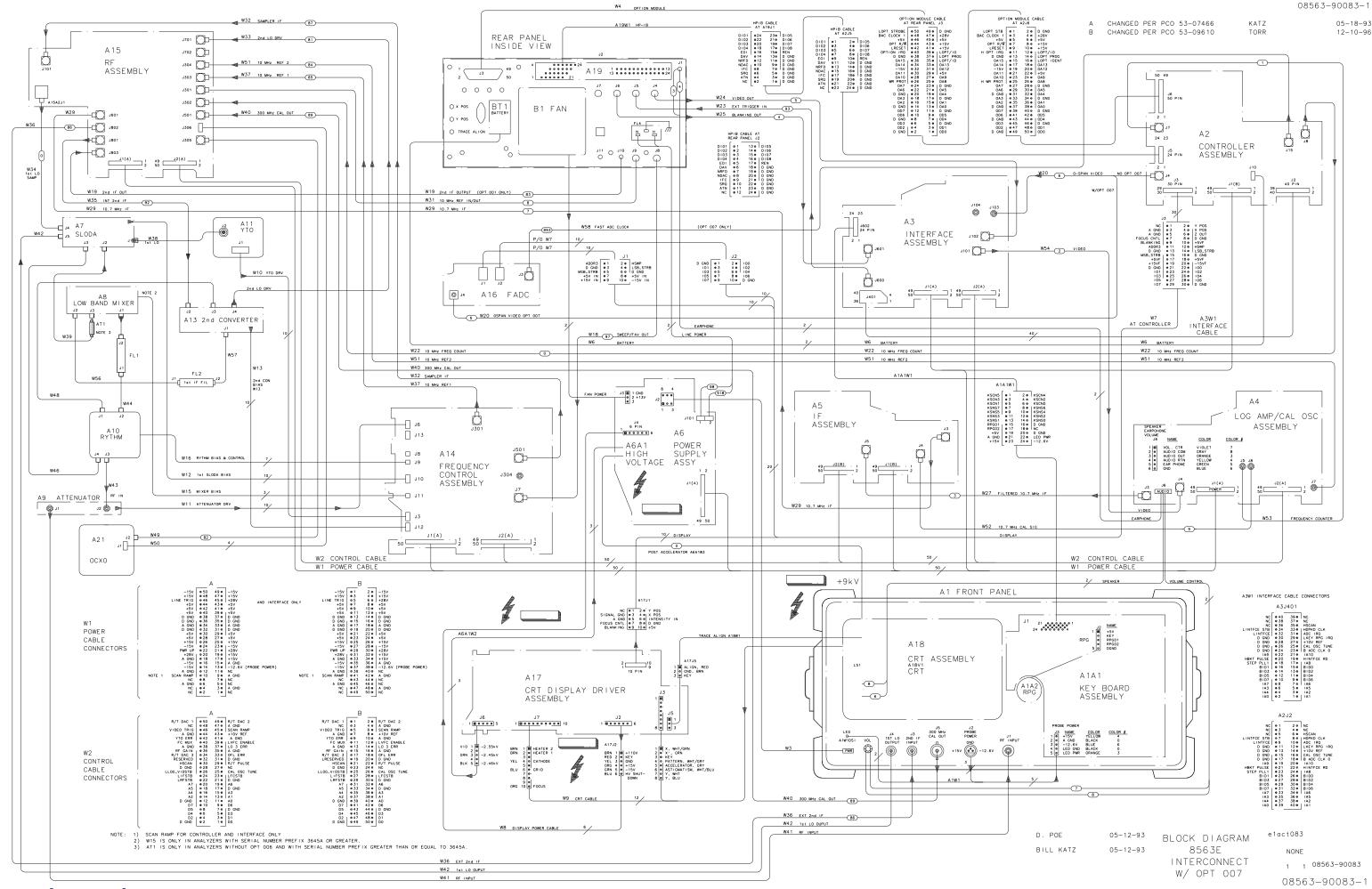

| Figure 13-2. 8560 E-Series Interconnect Block Diagram                  |     |

| Table 1-1 . Instrument Variations                                              | 29  |

|--------------------------------------------------------------------------------|-----|

| Table 1-2 . Service Kit Contents                                               |     |

| Table 1-3 . Static-Safe Accessories                                            | 35  |

| Table 1-4 . Recommended Test Equipment.                                        |     |

| Table 1-5 . Agilent Technologies Sales and Service Offices.                    | 46  |

| Table 2-1 . Related Adjustments                                                |     |

| Table 2-2 . Adjustable Components                                              | 54  |

| Table 2-3 . Factory Selected Components                                        |     |

| Table 2-4 . TAM Adjustments                                                    | 58  |

| Table 2-5 . Required Test Equipment for TAM                                    | 59  |

| Table 2-6 . Factory-Selected LC Filter Capacitors                              | 70  |

| Table 2-7 . LC Factory-Selected Capacitor Selection                            | 70  |

| Table 2-8 . Factory-Selected XTAL Filter Capacitors.                           |     |

| Table 2-9 . XTAL Factory-Selected Capacitor Selection                          |     |

| Table 2-10 . Capacitor Part Numbers                                            |     |

| Table 2-11 . Sampling Adjustments.                                             |     |

| Table 2-12 . Conversion Loss Data                                              |     |

| Table 2a-1 . Recommended Test Equipment                                        | 135 |

| Table 3-1 . Required Tools                                                     |     |

| Table 4-1 . Reference Designations                                             |     |

| Table 4-2. Abbreviations                                                       |     |

| Table 4-3 . Multipliers                                                        |     |

| Table 4-4 . Replaceable Parts.                                                 |     |

| Table 4-5 . Replaceable Parts –8561E/EC and 8563E/EC (see Figure 4-1)          |     |

| Table 4-6 . Parts List, Cover Assembly –8561E/EC and 8563E/EC (see Figure 4-2) |     |

| Table 4-7 . Parts List, Main Chassis – 8561EC and 8563EC (see Figure 4-8)      |     |

| Table 4-8 . Parts List, Main Chassis –8561E and 8563E (see Figure 4-3)         |     |

| Table 4-9. Parts List, RF Section – 8561E/EC and for 8563E/EC                  |     |

| (see Figures 4-4 and 4-5)                                                      | 256 |

| Table 4-10 . Parts List, Front Frame – 8561EC and 8563EC (see Figure 4-9)      |     |

| Table 4-11 . Parts List, Front Frame –8561E and 8563E (see Figure 4-6)         |     |

| Table 4-12 . Parts List, Rear Frame –8561EC and 8563EC (see Figure 4-10)       |     |

| Table 4-13 . Parts List, Rear Frame –8561E and 8563E (see Figure 4-7).         |     |

| Table 6-1 . Location of Assembly Troubleshooting Text                          |     |

| Table 7-1 . W2 Control Cable Connections.                                      |     |

| Table 7-2 . Automatic Fault Isolation References                               |     |

| Table 7-3 . TAM Tests versus A3 Test Connectors.                               |     |

| Table 7-4 . Keyboard Matrix                                                    |     |

| Table 7-5 . Counter Frequencies                                                |     |

| Table 7-6 . Trigger MUX Truth Table.                                           |     |

| Table 7-7 . A3U102 Latch Outputs                                               |     |

| Table 7-8 . HMUX_SELO/1 versus Detector Mode                                   |     |

| Table 7-9 . Logic Levels at A3U108                                             |     |

| Table 7-10 . Demultiplexer A3U410 Truth Table                                  |     |

| Table 7-11 . Demultiplexer A3U500 Truth Table                                  |     |

| 1                                                                              |     |

## Tables

| Table 7-12 . LP/Q Truth Table                                              |

|----------------------------------------------------------------------------|

| Table 7-13 . Control Word at Primary Address (U3 and U4).419               |

| Table 8-1 . Automatic Fault Isolation References    433                    |

| Table 8-2. TAM Tests versus Test Connectors    434                         |

| Table 8-3 . Sweep Width Settings.438                                       |

| Table 8-4 . IF Gain Application Guideline (ATTEN = 10 dB)446               |

| Table 9-1. TAM Tests versus Test Connectors    487                         |

| Table 9-2 . Gate Times                                                     |

| Table 9-3 . Gate Times                                                     |

| Table 10-1 . Measured Signal Line Location                                 |

| Table 10-2 . Automatic Fault Isolation References    525                   |

| Table 10-3 . TAM Tests versus Test Connectors                              |

| Table 10-4 . Center Frequency Tuning Values.532                            |

| Table 10-5 . Sampling Oscillator Test Frequencies536                       |

| Table 10-6 . Sampling Oscillator PLL Divide Numbers    551                 |

| Table 10-7 . Amplifier Polarities555                                       |

| Table 10-8 . Voltages in FM Coil and Main Loop Drivers560                  |

| Table 10-9 . Main Coil Coarse and Fine DACs Voltages.561                   |

| Table 10-10 . Postscaler Divide Numbers563                                 |

| Table 10-11 . Unlocked Fractional N Troubleshooting Areas    564           |

| Table 10-12 . Divider and Integrator Troubleshooting.566                   |

| Table 10-13 . Sweep Signal Destination versus Span.568                     |

| Table 10-14 . Harmonic Mixing Number versus Center Frequency    569        |

| Table 10-15 . Settings of Sweep Switches571                                |

| Table 10-16 . Settings for Switches and Comparators573                     |

| Table 10-17 . Settings for Switches and Comparators575                     |

| Table 11-1 . Automatic Fault Isolation References    596                   |

| Table 11-2 . TAM Tests versus Test Connectors                              |

| Table 11-3 . 8561E/EC Attenuator Control Truth Table                       |

| Table 11-4 . 8563E/EC Attenuator Control Truth Table                       |

| Table 11-5 . Sweep + Tune Multiplier Values616                             |

| Table 11-6 . RF Section Mnemonic Table                                     |

| Table 12-1 . Automatic Fault Isolation References    640                   |

| Table 12-2 . TAM Tests versus Test Connectors                              |

| Table 12-3 . W1 Power-Cable Connections653                                 |

| Table 12-4 . Automatic Fault Isolation References    654                   |

| Table 13-1 . CLIPs Available for 8561E, 8561EC, 8563E, and 8563EC Spectrum |

| Analyzers                                                                  |

# 1 General Information

### Introduction

This Agilent 8561E/EC and Agilent 8563E/EC Spectrum Analyzers Service Guide contains information required to adjust and service the Agilent 8561E, 8561EC, 8563E, and 8563EC to the assembly level.

| How to Use this Guide page                                | 26 |

|-----------------------------------------------------------|----|

| Differences between E-series and EC-series Analyzers page | 28 |

| Instrument Variations page                                | 29 |

| Serial Number and Repair Information page                 | 30 |

| Agilent 85629B Test and Adjustment Module page            | 32 |

| Service Kit page                                          | 33 |

| Recommended Test Equipment page                           | 38 |

| Electrostatic Discharge page                              | 34 |

| Returning Instrument for Service page                     | 36 |

### How to Use this Guide

Chapters 1 through 5 contain adjustments and parts information that can be used to adjust your spectrum analyzer and to help you fix problems.

Chapter 6, "General Troubleshooting", can be used to identify the location of a problem to a board or functional area in the spectrum analyzer.

Chapters 7 through 13, which cover functional areas, can then be used to help you localize the problem further.

### Conventions used in this guide

| Screen Text           | This font indicates text displayed on the screen                         |

|-----------------------|--------------------------------------------------------------------------|

| Кеу                   | This font indicates a softkey or a hardkey                               |

| 8561E/EC,<br>8563E/EC | These terms are used to refer to both E-series and EC-series instruments |

### **Documentation Outline**

Agilent Technologies 8560 E-Series and EC-Series Spectrum Analyzer Calibration Guide

- Tells you how to run verification software.

- Tells you what your spectrum analyzer's specifications are.

- Tells you how to test your spectrum analyzer.

Agilent Technologies 8560 E-Series and EC-Series Spectrum Analyzer User's Guide

- Tells you how to make measurements with your spectrum analyzer.

- Tells you how to install your spectrum analyzer.

- Tells you how to program your spectrum analyzer.

Agilent Technologies 8560 E-Series and EC-Series Spectrum Analyzer Quick Reference Guide

- Is an abbreviated version of the Agilent Technologies 8560 E-Series and EC-Series Spectrum Analyzer's User's Guide

- Provides you with a listing of all remote programming commands.

Agilent Technologies 8560 E-Series Spectrum Analyzer Component Level Information

• Provides schematics and parts lists for the instrument.

### Differences between 8560 EC-Series and E-Series Spectrum Analyzers