### **Discontinued Product—Support Information Only**

This literature was published years prior to the establishment of Agilent Technologies as a company independent from Hewlett-Packard and describes products or services now available through Agilent. It may also refer to products/services no longer supported by Agilent. We regret any inconvenience caused by obsolete information. For the latest information on Agilent's test and measurement products go to:

www.agilent.com/find/products

Or in the US, call Agilent Technologies at 1-800-452-4844 (8am-8pm EST)

## The HP 1670-Series Benchtop Logic Analyzers

### **Technical Data**

Identifying the cause of problems in embedded microprocessor system designs can be difficult. The Hewlett-Packard 1670-series benchtop logic analyzers have the features to help the embedded system design team find hardware and software defects quickly.

With 64K of acquisition memory (1M optional) the HP 1670-series logic analyzers are the first benchtop logic analyzers which display processor mnemonics and verify critical hardware timing relationships over a long period of time.

With the standard Ethernet LAN interface, the software designer can now capture a real-time microprocessor trace and time-correlate it to source code in C++ or other highlevel languages on a PC or workstation. For time-correlation of source code, order the HP B3740A Software Analysis package.

The combination of deep memory, large internal disk drive, and LAN make the HP 1670-series of benchtop logic analyzers especially well suited to solving your integration problems.

- Mass storage is provided by an internal hard drive which provides quick storage and retrieval of files.

- The 3.5-inch high-density flexible disk drive supports both DOS and LIF formats.

- The LAN interface enables access to the logic analyzer files via FTP or NFS. Use X11 windows to control or view the logic analyzer on a PC or workstation. The LAN interface includes both Ethertwist (10BASE-T) and ThinLan (10BASE 2) connectors.

- Store data as ASCII files and screen images in TIFF, PCX, and EPS (encapsulated PostScript<sup>TM</sup>) formats.

# Get to the root cause of problems quickly

- New graphical trigger macros make trigger setup easier.

- Centronics, RS-232, HP-IB and LAN communication ports make connecting to other devices easier than ever. All of these come standard on all models of the HP 1670-series.

- The HP 1670-series operating system includes System Performance Analysis (SPA). SPA provides state histograms, state overview, and time interval analysis.

- The HP E2450A Symbolic Download Utility is included with the HP 1670series. This utility provides the capability to extract symbolic information from popular object module formats.

PostScript $^{TM}$  is a trademark of Adobe Systems Incorporated.

#### Logic Analyzer Key Specifications and Characteristics

| Model Number                | HP 1670D          | HP 1671D                                                                       | HP 1672D           |

|-----------------------------|-------------------|--------------------------------------------------------------------------------|--------------------|

| State and Timing Channels   | 136               | 102                                                                            | 68                 |

| Timing Analysis             | Conventional: 125 | M Hz all channels, 250                                                         | M Hz half channels |

| State Analysis<br>Speed     |                   | 100 M Hz, all channels                                                         |                    |

| State Clocks/<br>Qualifiers | 4                 | 4                                                                              | 4                  |

| Memory Depth<br>per Channel | . (1M pe          | el, 128K in timing half-c<br>er channel optional mei<br>timing half-channel me | mory,              |

#### HP 1670-Series General-Product Information

| Human Inte                         | rface                                                                                                                                                                                    | Program-                          | Each instrument is fully                                                                                                                                             | Screen                                     | An image file of any display                                                                                                                                                                                   |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Front Panel                        | A knob and keypads<br>make up the front-<br>panel human interface.<br>Keys include control,<br>menu, display naviga-<br>tion, and alpha-numer-<br>ic entry functions.                    | HP Printer<br>Support             | programmable from a computer via HP-IB and RS-232 connections. This feature is standard on all models.  Printers which use the HP Printer Control Language (PCL) and | Image Files                                | screen can be stored to<br>disk via the display's<br><i>Print</i> field. Black &<br>white TIFF, PCX,<br>Encapsulated<br>PostScript (EPS), and<br>gray-scale TIFF file for-                                     |

| M ouse                             | A DIN mouse is shipped as standard equipment. It provides full instrument control. Knob functionality is replicated by holding down the right button and moving the mouse left or right. | h<br>(<br>)<br>s<br>(<br>)<br>(   | have a parallel<br>Centronics, RS-232 or<br>HP-IB interface are<br>supported: HP<br>DeskJet, LaserJet,<br>QuietJet, PaintJet, and<br>ThinkJet models.                | ASCII Data<br>Files                        | mats are available.  State or timing listings can be stored as ASCII files on a flexible disk via the display's <i>Print</i> field.  These files are equivalent in character width and line length to hardcopy |

| Keyboard                           | The logic analyzer can<br>also be operated using<br>a DIN keyboard. Order<br>the HP Logic Analyzer<br>Keyboard Kit, model                                                                | Alternate<br>Printer<br>Supported | The Epson FX80, LX80<br>and M X80 printers<br>with an RS-232 or<br>Centronics interface<br>supported in the Epson<br>8-bit graphics mode.                            |                                            | listings printed via the<br>Print All selection.  Logic analyzer files that include configuration and data information (if present) are                                                                        |

| Input/Outpu<br>Printing            | ts All units ship with a                                                                                                                                                                 |                                   | Screen images can be printed in black and white from all menus using the <i>Print</i> field. State or timing listings                                                |                                            | encoded in a binary<br>format. They can be<br>stored to or loaded<br>from the hard disk drive<br>or a flexible disk.                                                                                           |

|                                    | Centronics parallel<br>printer port, RS-232,<br>and HP-IB as standard<br>equipment.                                                                                                      |                                   | can be printed in full or part (starting from center screen) using the <i>Print All</i> selection.                                                                   | Recording of<br>Acquisition<br>and Storage | Binary format configuration/data files are stored with the time of                                                                                                                                             |

| LAN Interface                      | An Ethernet LAN interface is standard with                                                                                                                                               | Mass Stora<br>and Softwa          |                                                                                                                                                                      | Times                                      | acquisition and the time of storage.                                                                                                                                                                           |

|                                    | the HP 1670-series. The                                                                                                                                                                  | Updating the                      | The operating system                                                                                                                                                 | Acquisition                                | Arming                                                                                                                                                                                                         |

|                                    | LAN interface comes<br>with both Ethertwist<br>(10BASE-T) and<br>ThinLan (10BASE 2)                                                                                                      | Operating<br>System               | resides in Flash ROM<br>and can be updated<br>from the flexible disk                                                                                                 | Initiation                                 | Arming is started by<br>Run or the Port In<br>BNC.                                                                                                                                                             |

|                                    | connectors.The LAN supports FTP and PC/NFS connection                                                                                                                                    | Mass Storage                      | drive or the hard disk<br>drive.                                                                                                                                     | Cross Arming                               | The analyzer machines can cross-arm each other.                                                                                                                                                                |

|                                    | protocols. It also works with X11 window packages.                                                                                                                                       |                                   | internal hard disk drive<br>and by a 1.44 M byte,<br>3.5-inch flexible disk<br>drive. Supports DOS                                                                   | Output                                     | An output signal is provided at the Port Out BNC.                                                                                                                                                              |

| Software<br>Analysis<br>Capability | The HP B3740A Soft-<br>ware Analyzer provides<br>true source line refer-<br>encing and symbol<br>download capabilities.<br>Standard object<br>module formats are                         |                                   | and LIF formats.  A disk drive provides quick storage and retrieval of files.                                                                                        |                                            |                                                                                                                                                                                                                |

supported.

#### HP 1670-series Logic Analyzer Specifications and Characteristics

| Port In/Out                               |                                                                                                                                                                                       |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT IN<br>Signal and<br>Connection       | Port In is a standard<br>BNC connection.<br>The input operates at<br>TTL logic signal levels.<br>Rising edges are valid<br>input signals.                                             |

| PORT OUT<br>Signal and<br>Connection      | Port Out is a standard<br>BNC connection with<br>TTL logic signal levels.<br>A rising edge is assert-<br>ed as a valid output.                                                        |

| Arming Time                               | es                                                                                                                                                                                    |

| PORT IN<br>Arms Logic<br>Analyzer [1]     | 15 ns typical delay from signal input to a <i>don't care</i> logic analyzer trigger.                                                                                                  |

| Logic<br>Analyzer<br>Arms PORT<br>OUT [1] | 120 ns typical delay<br>from logic analyzer<br>trigger to signal<br>output.                                                                                                           |

| Operating E                               | nvironment                                                                                                                                                                            |

| Pow er                                    | 115 Vac or 230 Vac, -22%<br>to +10%, single phase,<br>48-66 Hz, 320 VA max                                                                                                            |

| Temperature                               | Instrument, 0° to 50° C<br>(+32° to 122° F). Disk<br>media, 10° to 40° C<br>(+50° to 104° F). Probes<br>and cables, 0° to 65° C<br>(+32° to 149° F)                                   |

| Humidity                                  | Instrument, up to 95%, relative humidity at +40° C (+140° F). Disk media and hard drive, 8% to 85% relative humidity.                                                                 |

| Altitude                                  | To 3,048 m (10,000 ft)                                                                                                                                                                |

| Vibration:<br>Operating                   | Random vibrations<br>5–500Hz,<br>10 minute per axis,<br>~ 0.3 g (rms).                                                                                                                |

| Vibration:<br>Non Operating               | Random vibrations<br>5–500 Hz,10 minutes per<br>axis,~ 2.41 g (rms); and<br>swept sine resonant<br>search, 5–500 Hz,<br>0.75 g (0-peak),<br>5 minute resonant<br>dwell @ 4 resonances |

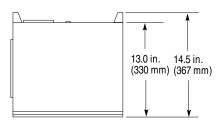

| 28.6 lbs. (13 kg) See figure 1                                                      |

|-------------------------------------------------------------------------------------|

| See figure 1                                                                        |

|                                                                                     |

| IEC 348/ HD 401,<br>UL 1244, and<br>CSA Standard C22.2<br>No. 231 (series M-89)     |

| /EN 55011 (1991):<br>ss A<br>/EN 50082-1 (1992):<br>/ AD<br>/EN 50082-1 (1992):3V/m |

|                                                                                     |

Weight 28.6 lb. (13kg)

Figure 1

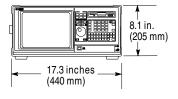

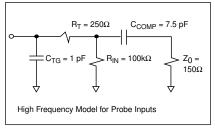

| Logic Analyzer Probes |                                |   |

|-----------------------|--------------------------------|---|

| Input<br>Resistance   | 100 kΩ ±2%                     | _ |

| Input<br>Capacitance  | approx. 8 pF<br>(see figure 2) | _ |

Figure 2

| Minimum<br>Input Voltage<br>Swing | 500 mV peak-to-peak                                                                                                |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Minimum<br>Input<br>Overdrive     | 250 mV or 30% of input<br>amplitude, whichever is<br>greater                                                       |

| Threshold<br>Range                | -6.0 V to +6.0 V in 50-m' increments                                                                               |

| Threshold<br>Setting              | Threshold levels may be defined for pods (17-channel groups) on an individual basis                                |

| Threshold<br>Accuracy*            | ± (100 mV +3% of<br>threshold setting)                                                                             |

| Input<br>Dynamic<br>Range         | ± 10 V about the<br>threshold                                                                                      |

| Maximum<br>Input Voltage          | ± 40 V peak                                                                                                        |

| +5 V<br>Accessory<br>Current      | 1/3 amp maximum<br>per pod                                                                                         |

| Channel<br>Assignment             | Each group of 34<br>channels (a pod pair)<br>can be assigned to<br>Analyzer 1, Analyzer 2<br>or remain unassigned. |

per axis.

<sup>[1]</sup> Time may vary depending upon the mode of logic analyzer operation.

<sup>\*</sup> Warranted Specification

| State Analy                         | sis                                                                |                           | State Clock<br>Qualifier                           | The high or low of the clocks can be ANDed                                                                                | Time<br>Tagging [4]                                       | Measures the time between stored states,                                                                                                                                                     |  |

|-------------------------------------|--------------------------------------------------------------------|---------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Maximum<br>State                    | 100 M Hz                                                           |                           |                                                    | or ORed with the clock specification.                                                                                     | idgging [+]                                               | relative to either the pre-<br>vious state or to the trig-                                                                                                                                   |  |

| Speed<br>Channel<br>Count [2]       | HP 1670D<br>HP 1671D<br>HP 1672D                                   | 136/68<br>102/51<br>68/34 | Setup/Hold [3<br>one clock,<br>one edge            | 3.5/0 ns to 0/3.5 ns<br>(in 0.5 ns increments)                                                                            |                                                           | ger. Max. time between<br>states is 34.4 sec. Min.<br>time between states is 8<br>ns.                                                                                                        |  |

| Memory Depth per Channel            |                                                                    |                           | one clock,<br>both edges<br>multi-clock,           |                                                                                                                           | Time Tag<br>Value                                         | 8 ns to 34.4 seconds<br>± (8 ns + 0.01% of time<br>tag value)                                                                                                                                |  |

| Standard                            | <b>64K</b> (65,536) samp                                           | les                       | multi-edge Minimum State Clock                     | (in 0.5 ns increments) 3.5 ns                                                                                             | Time Tag<br>Resolution                                    | 8 ns or 0.1%<br>(whichever is greater)                                                                                                                                                       |  |

| Time                                | 32K                                                                |                           | Pulse Width                                        | <del></del>                                                                                                               | Timing Ana                                                | lysis                                                                                                                                                                                        |  |

| Tags On<br>Compare<br>Mode On       | (32,768) samp<br>32K<br>(32,768) samp                              | ŕ                         | M inimum<br>M aster to<br>M aster<br>Clock Time [3 | 10 ns                                                                                                                     | Conventional<br>Timing                                    | Data stored at selected sample rate across all timing channels.                                                                                                                              |  |

| Compare<br>Mode and<br>Time Tags On | 32K<br>(32,768) samp                                               | ŕ                         | Minimum<br>Slave to<br>Slave<br>Clock Time [3      | 10 ns                                                                                                                     | Maximum<br>Timing<br>Speed [2]                            | 125 M Hz/250 M Hz                                                                                                                                                                            |  |

| Option 030                          | <b>1M</b> (1,032,192) sai                                          | mples                     | Minimum<br>Master to<br>Slave                      | 0.0 ns                                                                                                                    | Channel<br>Count [2]                                      | HP 1670D 136/68<br>HP 1671D 102/51<br>HP 1672D 68/34                                                                                                                                         |  |

| Time                                | 500K                                                               | nlaa                      | Clock Time [3                                      | 3]                                                                                                                        | Sample                                                    | 8 ns/4 ns minimum                                                                                                                                                                            |  |

| Tags On<br>Compare<br>Mode On       | (507,904) sam<br>250K<br>(245,760) sam                             |                           | Minimum<br>Slave to Mas<br>Clock Time [3           |                                                                                                                           | Period [2]                                                | 41 µs/10 µs<br>maximum                                                                                                                                                                       |  |

| Compare<br>Mode and<br>Time Tags On | 120K<br>(114,688) sam                                              |                           | Clock<br>Qualifiers<br>Setup/Hold [3               | 4.0/0 ns (fixed)                                                                                                          | Memory<br>Depth per<br>Channel [2]                        | 64K standard<br>64K/128K samples<br>(65,536/131,072)                                                                                                                                         |  |

| State Clocks                        | HP 1670D<br>HP 1671D<br>HP 1672D                                   | 4 clocks<br>4 clocks      | State<br>Tagging [4]                               | Counts the number of qualified states between each stored                                                                 |                                                           | 1M option<br>1M/2M samples<br>(1,032,192/2,080,768)                                                                                                                                          |  |

|                                     | Clocks can be either one or tanalyzers at a Clock edges of         | two state<br>any time.    |                                                    | state. Measurement can be shown relative to the previous state or relative to trigger. Max. count is $4.29 \times 10^9$ . | Time Covered<br>by Data [2]                               | Sample period × memory depth                                                                                                                                                                 |  |

|                                     | ORed togethe operate in sin phase, two-ph                          | r and<br>gle              | State Tag<br>Count                                 | 0 to $4.29 \times 10^9$                                                                                                   |                                                           |                                                                                                                                                                                              |  |

|                                     | demultiplexing phase mixed in                                      | g, or two-<br>mode.       | State Tag<br>Resolution                            | 1 count                                                                                                                   | [2] Full Channel /Ha                                      | lif Channel Modes                                                                                                                                                                            |  |

|                                     | Clock edge is<br>selectable as<br>negative, or b<br>for each clock | positive,<br>oth edges    |                                                    |                                                                                                                           | [3] Specified for an slew rate = 1V/n                     | input signal VH= $-0.9V$ , VL = $-1.7V$ , s, and threshold = $-1.3V$                                                                                                                         |  |

|                                     |                                                                    |                           |                                                    |                                                                                                                           | available in the<br>speed penalty fo<br>time or state tag | gging (Count Time or Count State) is<br>full-channel state mode. There is no<br>or tag use. Memory is halved when<br>is are used unless a pod pair (34-<br>remains unassigned in the<br>enu. |  |

| Time Interv                                                          | al Accuracy                                                                                                            | Range                                               | Recognize data which is                                                                                 | Qualifier                                                   | A user-specified term                                                                                                                                                                                        |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample<br>Period<br>Accuracy                                         | ± 0.01%                                                                                                                | Recognizers                                         | numerically between or<br>on two specified pat-<br>terns (ANDed combina-<br>tion of zeros and/or        |                                                             | that can be any state,<br>no state, any recogniz-<br>er, (pattern, ranges or<br>edge/glitch), any timer,<br>or the logical combina-<br>tion (NOT, AND, NAND<br>OR, NOR, XOR, NXOR)<br>of the recognizers and |

| Channel-to-<br>Channel<br>Skew                                       | 2 ns typical,<br>3 ns maximum                                                                                          | Range<br>Recognizers                                | ones).<br>2                                                                                             |                                                             |                                                                                                                                                                                                              |

| Accuracy                                                             | ± (Sample Period<br>+ channel-to-channel                                                                               | Range Width                                         | 32 channels                                                                                             | Branching                                                   | timers.                                                                                                                                                                                                      |

|                                                                      | skew + 0.01% of time interval reading)                                                                                 | Edge/Glitch<br>Recognizers                          | Trigger on glitch or edge on any channel.                                                               | Brancing                                                    | Each sequence level<br>has a branching qualifi-<br>er. When satisfied, the                                                                                                                                   |

| MaximumSample Period 4-8 ns :Delay8.389 msAfterSample Period > 8 ns: |                                                                                                                        | Edge can be specified as rising, falling or either. |                                                                                                         | analyzer will branch to<br>the sequence level<br>specified. |                                                                                                                                                                                                              |

| Triggering                                                           | 1,048,575 × sample<br>period                                                                                           | Edge/Glitch<br>Recognizers                          | 2 (in timing mode only)                                                                                 | Occurrence<br>Counters                                      | Sequence qualifier may<br>be specified to occur<br>up to 1,048,575 times                                                                                                                                     |

| Trigger Spe                                                          |                                                                                                                        | Edge/Glitch                                         | HP 1670D 136/68                                                                                         |                                                             | before advancing to<br>the next level. Each<br>sequence level has its<br>own counter.                                                                                                                        |

| Macros selected from a c                                             | Trigger setups can be selected from a categorized list of trigger                                                      | Width (in<br>channels) [2]                          | HP 1671D 102/51<br>HP 1672D 68/34                                                                       | se                                                          |                                                                                                                                                                                                              |

|                                                                      | macros. Each macro is shown in graphical form and has a written description. Macros                                    |                                                     | Sample Period 4-8 ns:<br>28 ns<br>Sample Period > 8 ns:<br>20 ns + sample period                        | Maximum<br>Occurrence<br>Count                              | 1,048,575                                                                                                                                                                                                    |

|                                                                      | can be chained together to create a custom trigger sequence.                                                           | Greater than Duration (timing only)                 | Sample period 4-8 ns:<br>8 ns to 8.389 ms.<br>Accuracy is -2 ns to                                      | Storage<br>Qualification<br>(state only)                    | Each sequence level has a storage qualifier that specifies the states that are to be stored.                                                                                                                 |

| Pattern<br>Recognizers                                               | Each recognizer is the AND combination of bit (0,1, or X) patterns in each label.                                      |                                                     | +10 ns Sample period > 8 ns: (1 to 2 <sup>20</sup> ) × sample period. Accuracy is -2 ns + sample period | Maximum<br>Sequencer<br>Speed                               | 125 M Hz                                                                                                                                                                                                     |

| Pattern<br>Recognizers                                               | 10                                                                                                                     | Less than                                           | + 2 ns ± 0.01%<br>Sample period 4-8 ns:                                                                 | State<br>Sequence<br>Levels                                 | 12                                                                                                                                                                                                           |

| Pattern Width<br>(in channels)<br>[2]                                |                                                                                                                        | <b>Duration</b> (timing only)                       | 8 ns to 8.389 ms. Accuracy is -2 ns to +10 ns. Sample period > 8 ns:                                    | Timing<br>Sequence                                          | 10                                                                                                                                                                                                           |

| Minimum Pattern and Range Recognizer Pulse Width                     | 125 M Hz and 250 M Hz<br>Timing M odes: 13 ns<br>+ channel-to-channel<br>skew<br>≤ 125 M Hz Timing<br>M odes: 1 sample |                                                     | (1 to 2 <sup>20</sup> ) × sample<br>period.<br>Accuracy is 2 ns +<br>sample period – 2 ns ±<br>0.01%    | Levels                                                      |                                                                                                                                                                                                              |

|                                                                      | period + 1 ns + chan-<br>nel-to-channel skew<br>+ 0.01%                                                                |                                                     |                                                                                                         |                                                             |                                                                                                                                                                                                              |

| Timers Timers Timer Range                                     | Timers may be Started, Paused, or Continued at entry into any sequence level after the first.  2  400 ns to 500 seconds           | Activity          | Provided in the Configuration, State Format, and Timing Format menus for monitoring device-under-test activity while setting up the analyzer.                                                                       |                                                  | are kept only when both patterns can be found in an acquisition. Statistics are minimum x to o time, maximum x to o time, average x to o time, and ratio of valid runs to total runs. |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer Resolution Timer Accuracy Timer Recovery Tim Data In to | 16 ns or 0.1% whichever is greater  ± 32 ns or ± 0.1%, whichever is greater  70 ns e  110 ns typical                              | Labels            | Channels may be grouped together and given a 6-character name called a <i>label</i> . Up to 126 labels in each analyzer may be assigned with up to 32 channels per label. Trigger terms may be given an 8-character | Compare<br>Mode<br>Functions<br>Compare<br>Image | Performs post-process ing bit-by-bit comparison of the acquired state data and Compare Image data.  Created by copying a state acquisition into                                       |

| Trigger Out<br>BNC Port                                       | то тургош                                                                                                                         |                   | name.                                                                                                                                                                                                               | J                                                | the compare image<br>buffer. Allows editing                                                                                                                                           |

|                                                               | n, M easurement                                                                                                                   |                   | ent Functions                                                                                                                                                                                                       |                                                  | of any bit in the                                                                                                                                                                     |

| and Displa                                                    | y Functions                                                                                                                       | Markers           | Two markers (x and o) are shown as dashed lines in the display.                                                                                                                                                     |                                                  | Compare Image to a 1, X or O.                                                                                                                                                         |

| Arming                                                        | Each analyzer can be armed by the Run key, the other analyzer, or the Port In.                                                    | Time<br>Intervals | The x and o markers measure the time interval between                                                                                                                                                               | Compare<br>Image<br>Boundaries                   | Each channel (column) in the compare image can be enabled or disabled via bit masks in                                                                                                |

| Run                                                           | Starts acquisition of data in specified trace mode.                                                                               |                   | events occurring on<br>one or more wave-<br>forms or states.<br>Available in state when                                                                                                                             |                                                  | the Compare Image.<br>Upper and lower<br>ranges of states (rows)                                                                                                                      |

| Stop                                                          | Stop halts acquisition and displays the current acquisition data.                                                                 | Delta States      | time tagging is on.  The x and o markers measure the number                                                                                                                                                         |                                                  | in the compare image can be specified. Any data bits that do not fall within the enabled                                                                                              |

| Trace M ode                                                   | Single mode acquires data once per trace specification; repetitive mode repeats                                                   |                   | of tagged states<br>between any two<br>states (state only).                                                                                                                                                         |                                                  | channels and the specified range are not compared.                                                                                                                                    |

|                                                               | tive mode repeats single mode acquisitions until Stop is pressed or until pattern time interval or compare stop criteria are met. | Patterns          | The x or o marker can<br>be used to locate the<br>nth occurrence of a<br>specified pattern<br>before or after trigger,<br>or after the beginning<br>of data. The o marker                                           | Stop<br>Measurement                              | Repetitive acquisitions may be halted when the comparison between the current state acquisition and the current Compare Image is equal or not                                         |

| Trigger                                                       | Displayed as a vertical dashed line in the timing waveform, state waveform and                                                    |                   | can also find the nth occurrence of a pattern before or after the x marker.                                                                                                                                         | Compare<br>M ode<br>Displays                     | equal.  Reference Listing display shows the Compare Image and                                                                                                                         |

|                                                               | X-Y chart displays and as line 0 in the state listing and state compare displays.                                                 | Statistics        | x to o marker statistics<br>are calculated for<br>repetitive acquisitions.<br>Patterns must be<br>specified for both<br>markers, and statistics                                                                     | ,                                                | bit masks; Difference<br>Listing display highlights<br>differences between<br>the current state acqui-<br>sition and the Compare<br>Image.                                            |

| Data Entry/                  | <br>Display                                                                                    | Timing                            | Displays timing                                                                                   | Symbols              |                                                                                      |

|------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|

| Display<br>M odes            | State Listing, State<br>Waveforms, State                                                       | Waveform<br>Display               | acquisition in wave-<br>form format.                                                              | Pattern<br>Symbols   | User can define a mnemonic for the spe-                                              |

|                              | Chart, State Compare<br>Listing, Compare                                                       | Sec/div [2]                       | 1 ns to 4.4 sec/div/<br>1 ns to 2.2 sec/div                                                       | ,                    | cific bit pattern of a label. When data dis-                                         |

|                              | Difference Listing,<br>Timing Waveforms,                                                       | Delay                             | - 2,500 s to + 2,500 s                                                                            |                      | play is SYM BOL,<br>mnemonic is displayed                                            |

|                              | Timing Listing, inter-<br>leaved time-correlat-                                                | Accumulate                        | Waveform display is not erased between                                                            |                      | where the bit pattern occurs.                                                        |

|                              | ed listing of two state<br>analyzers (time tags                                                |                                   | successive acquisitions.                                                                          | Range<br>Symbols     | User can define a mnemonic covering a                                                |

|                              | on), and time-correlated State Listing with Timing Waveforms on the same display.              | Overlay Mode                      | Multiple channels can<br>be displayed on one<br>waveform display line.<br>When waveform size      | oyze.e               | range of values. When data display is SYM BOL, values within the specified range are |

| State X-Y<br>Chart Display   | Plots value of a speci-<br>fied label (on y-axis)<br>versus states or<br>another label (on x-  |                                   | set to large, the value<br>represented by each<br>waveform is displayed                           |                      | displayed as mnemonic<br>+ offset from base of<br>range.                             |

|                              | axis). Both axes can be scaled.                                                                |                                   | inside the waveform in the selected base.                                                         | Number of<br>Symbols | 1000 maximum.                                                                        |

| Markers                      | Correlated to State<br>Listing, State Compare,<br>and State Waveform<br>displays. Available as | Displayed<br>Waveforms            | 24 lines maximum on<br>one screen. Up to 96<br>lines may be specified<br>and scrolled through.    |                      |                                                                                      |

|                              | pattern, time, or statis-<br>tics (with time count-                                            | System<br>Performance<br>Analysis | SPA includes state<br>histogram, state<br>overview and time<br>interval measure-                  |                      |                                                                                      |

| Accumulate                   | Chart display is not erased between successive acquisitions.                                   |                                   | ments to aid in the software optimization process. These tools                                    |                      |                                                                                      |

| State<br>Waveform<br>Display | Displays state<br>acquisitions<br>in waveform format.                                          |                                   | provide a statistical<br>overview of your syn-<br>chronous design. For<br>additional information, |                      |                                                                                      |

| States/div                   | 1 to mem length/8                                                                              |                                   | refer to HP 10390A                                                                                |                      |                                                                                      |

| Delay                        | ± memory length                                                                                |                                   | System Performance<br>Software technical                                                          |                      |                                                                                      |

| Accumulate                   | Waveform display is<br>not erased between<br>successive acquisi-                               |                                   | data sheet, pub no.<br>5091-7850E.                                                                |                      |                                                                                      |

|                              | tions.                                                                                         | Bases                             | Binary, Octal,<br>Decimal,                                                                        |                      |                                                                                      |

| Overlay<br>Mode              | Multiple channels can<br>be displayed on one<br>waveform display line.                         |                                   | Hexadecimal, ASCII<br>(display only), sym-<br>bols, two's compli-                                 |                      |                                                                                      |

| Displayed<br>Waveforms       | 24 lines maximum on<br>one screen. Up to 96<br>lines may be specified<br>and scrolled through. |                                   | ment.                                                                                             |                      |                                                                                      |

#### **Ordering Information**

| HP 1670D         | 136-Channel 100-MHz State/250-MHz Timing with 64K Memory Depth and Ethernet LAN    |

|------------------|------------------------------------------------------------------------------------|

| HP 1671D         | 102-Channel 100-MHz State/250-MHz Timing with 64K Memory<br>Depth and Ethernet LAN |

| HP 1672D         | 68-Channel 100-MHz State/250-MHz Timing with 64K Memory<br>Depth and Ethernet LAN  |

| Additional HP    | 1660C/CS and 1670D-Series Product Options                                          |

| pt 030           | Extended Memory depth to 1M samples/channel (ordered at the time of purchase)      |

| pt 0B3           | Add Service Manual                                                                 |

| ot 1CM           | Rack Mount Kit                                                                     |

| ot UK9           | Front Panel Cover                                                                  |

| t W 30           | 3-Year extended repair service                                                     |

| ot W 50          | 5-Year extended repair service                                                     |

| ot OBF           | Add Programming Manual                                                             |

| ccessory So      | ftw are                                                                            |

| P B3740A         | Software Analyzer                                                                  |

| pt AJ4           | IBM, 3.5-inch Media/Documentation                                                  |

| ot AAY           | HP 9000 Series 700 Media/Documentation                                             |

| t AAV            | SUN (Solaris and SUN OS) Media/Documentation                                       |

| ot UDY<br>ot UBY | IBM Single User License<br>HP 9000 Series 700 Single User License                  |

| ot UBK           | SUN (Solaris and SUN 0S) Single User License                                       |

| P 10391B         | Inverse Assembler Development Package                                              |

| P 1670D-Ser      | ies Upgrades                                                                       |

| P E2471D         | Upgrade HP 1670D-Series from 64K to 1M of memory                                   |

| ot 001           | Upgrades HP 1670D from 64K to 1M of acquisition memory                             |

| ot 002           | Upgrades HP 1671D from 64K to 1M of acquisition memory                             |

| ot 003           | Upgrades HP 1672D from 64K to 1M of acquisition memory                             |

| P E2427B         | Add keyboard with DIN connector (PC style)                                         |

| ate/Timing       | Analyzer Probes & Lead Sets                                                        |

| P 5959-9333      | 5 Grey Probe Leads for HP 1670D-Series                                             |

| 9 5959-9334      | 5 Short Ground Leads for HP 1670D-Series                                           |

| P 5959-9335      | 5 Long Ground Leads for All State and Timing Analyzers                             |

| 01650-61608      | 16-Channel Probe Lead Set for State and Timing Analyzers                           |

| P 01650-63203    | Termination Adapter for State and Timing Analyzers                                 |

| P 1810-1278      | 9-Channel IC Termination DIP                                                       |

| P 1810-1588      | Termination IC SIP                                                                 |

| P 1251-8106      | 2×10, 0.1-inch Center Header (Similar to 3M p/n 2520-6002)                         |

| P 5090-4356      | Surface-Mount Grabbers (package of 20)                                             |

| P 5959-0288      | Throughhole Grabbers (package of 20)                                               |

| ther Acces       | ories for HP Logic Analyzers                                                       |

| P 1180B          | Testmobile for the HP 1670-Series                                                  |

| P 92199B         | Power Strip                                                                        |

| P 5041-9456      | Front Cover for HP 1670-Series                                                     |

| 5062-7379        | Rack Mount Kit for HP 1670-Series                                                  |

| <del>-</del>     |                                                                                    |

formation on kard Test & Measurement plications or services our local Hewlett-Packard A current listing is availthrough AccessHP at p.com. If you do not have internet, please contact P centers listed below and ect you to your nearest HP

ard Company surement Organization Creek Blvd. A 95052-8059

ard Canada Ltd. n Way Ontario LAW 5G1

ard rketing Centre elveen  $^{\mathrm{nds}}$

ard Japan Ltd. Assistance Center -Cho, Hachioji-Shi, pan 6-7832 56-7840

ard n Region Headquarters oon Drive, 9th Floor a 33126, U.S.A. 5/4220

#### w Zealand:

ard Australia Ltd. Street ctoria 3130

ard Asia Pacific Ltd Tower, Times Square, treet, Causeway Bay, 6 9285

ormation in this subject to change

e U.S.A.

9/96

ard Company 1996