# LOGIC ANALYZERS

# **HP 1660 Series Benchtop Logic Analyzers**

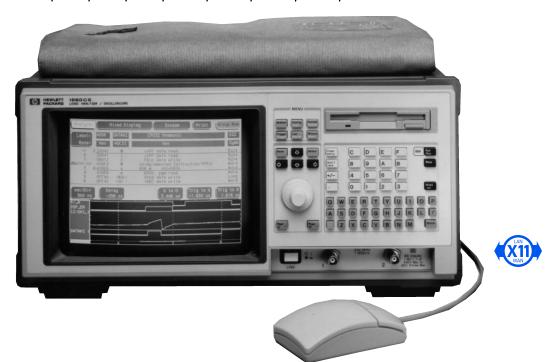

HP 1660C, 1661C, 1662C, 1663C, 1660CS, 1661CS, 1662CS, 1663CS, and 1664A

# Benchtop Logic Analyzers to Help You Identify the Root Cause of Difficult Problems Fast

- Features to bridge the hardware and software worlds

- · Broad microprocessor support with source code linkage

- · Optional Ethernet LAN for networked operation

- 5 modes of timing analysis to capture different kinds of data

- Optional built-in oscilloscope shows the analog perspective

- Upgrade paths to add more channels, LAN, or an oscilloscope

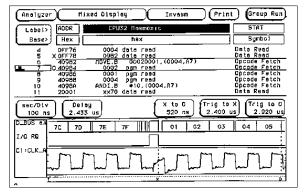

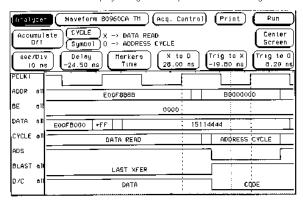

Code listings, timing waveforms, and oscilloscope waveforms can be time-correlated and displayed together to speed troubleshooting.

Timing waveforms can be displayed with data values and symbolic information to illustrate bus cycles and data flow.

### Seeing a Problem from All Sides Gives the Fastest Answers

Designing hardware and software for embedded microprocessor systems is difficult enough; getting it all to work together can be a real challenge. The HP 1660 series logic analyzers were designed to make things easier by bridging the gap between the hardware and software worlds. They cover a wide application range—from the isolation of elusive hardware flaws to the debugging of real-time code. You can see it all displayed together with time correlation and markers that track between code and waveforms.

### **An Excellent Toolset for Hardware Development**

Carpenters keep more than one kind of hammer in their toolsets so they can match the task at hand with the right hammer. The HP 1660 logic analyzers have five modes of timing analysis so hardware designers can adapt the analyzer to the speed and type of data they need to capture. Conventional timing analysis resolves time intervals as short as 2 ns between edges. Transitional timing is right for situations when you need to look at data bursts with periods of inactivity between.

Some of the tougher hardware problems can be found only with digital triggering and solved only with an oscilloscope. That's why the CS models come with a built-in, 1-GSa/s oscilloscope that can be triggered by the logic analyzer. Now, you can see what bus lines really look like at critical moments.

# More Functionality than a Software Engineer Would Expect

We've added some important capabilities to our logic analyzers to help software engineers even more. The HP 1660 models have functionality that was previously available only with more expensive logic analyzers—symbol and source code links and an Ethernet LAN interface.

A high percentage of the software written for embedded systems today is in C, a high-level language. So, the code trace taken by a logic analyzer should be shown at the source level. The HP Software Analyzer package (see page 378) gives you the high-level view required for faster debug by displaying a disassembled state analysis listing with symbolic data in a window alongside your source code listing. That makes finding elusive software defects a lot easier.

# LOGIC ANALYZERS

# **HP 1660 Series Benchtop Logic Analyzers (cont'd)**

HP 1660C, 1661C, 1662C, 1663C, 1660CS, 1661CS, 1662CS, 1663CS, and 1664A

# **Key Specifications and Characteristics for HP 1660 Series Logic Analyzers**

|                                  | HP 1660C, HP 1660CS                                                                                                                                                    | HP 1661C, HP 1661CS                             | HP 1662C, HP 1662CS | HP 1663C, HP 1663CS            | HP 1664A |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|--------------------------------|----------|--|

| State and timing channels        | 136                                                                                                                                                                    | 102                                             | 68                  | 34                             | 34       |  |

| State analysis speed             | 100 MHz in all modes 50 MHz in all m                                                                                                                                   |                                                 |                     |                                |          |  |

| State/timing memory depth        | 4K samples on all channels, 8K samples on half channels<br>(state analysis depth is halved when time tags are turned on)                                               |                                                 |                     |                                |          |  |

| Setup/hold time                  | 3.5/0 ns to 0/3.5 ns adjustable in 500-ps increments                                                                                                                   |                                                 |                     |                                |          |  |

| Timing analysis modes and speeds | Conventional: 250 MHz on all channels, 500 MHz on half channels<br>Transitional: 125 MHz on all channels, 250 MHz on half channels<br>Glitch: 125 MHz on half channels |                                                 |                     |                                |          |  |

| Min. detectable glitch width     | 3.5 ns                                                                                                                                                                 |                                                 |                     |                                |          |  |

| Probe input R & C                | 100 kΩ and ~ 8 pF                                                                                                                                                      |                                                 |                     |                                |          |  |

| Triggerresources                 | Patterns: 10 Edge and glitch terms: 2 Ranges 2 Timers: 2                                                                                                               |                                                 |                     |                                |          |  |

| Trigger sequence levels          | 12 with state analysis and 10 with timing analysis                                                                                                                     |                                                 |                     |                                |          |  |

| Trigger macros                   | 23 pre-defined trigger sequences with graphical representations and plain language descriptions                                                                        |                                                 |                     |                                |          |  |

| Mass storage                     |                                                                                                                                                                        | Hard disk drive and 1.44-MB flexible disk drive |                     | 1.44-MB flexible disk<br>drive |          |  |

| Ethernet LAN interface           | Optional; twisted pair and coaxial connectors                                                                                                                          |                                                 |                     | Not available                  |          |  |

| OS Boot Method                   | Flash ROM                                                                                                                                                              |                                                 |                     | Flexible disk                  |          |  |

#### Additional Information for 1660CS, 1661CS, 1662CS, and 1663CS

|                              | HP 1660CS              | HP 1661CS             | HP 1662CS             | HP 1663CS             |  |  |

|------------------------------|------------------------|-----------------------|-----------------------|-----------------------|--|--|

| Logic analysis capabilities  | Identical to HP 1660C  | Identical to HP 1661C | Identical to HP 1662C | Identical to HP 1663C |  |  |

| Scope channels               | 2                      |                       |                       |                       |  |  |

| Scope sample rate, bandwidth | 1 GSa/s, 250 MHz       |                       |                       |                       |  |  |

| Scope vertical resolution    | 8 bits                 |                       |                       |                       |  |  |

| Scope memory depth           | 8K samples per channel |                       |                       |                       |  |  |

#### Hard Disk Drive, I/O Connections and Ethernet LAN

A 540-MByte hard disk drive is standard in all HP Benchtop Logic Analyzers. A Centronics parallel printer port, an HP-IB and RS-232 interfaces are standard. Ethernet LAN is available as an option. Connecting a PC-style mouse and/or keyboard is easier than ever with the standard DIN connector interface. We've included the features you need to keep up with your changing needs and work environment.

#### **Compatible with a Computer-Oriented World**

You're probably spending more time working with a PC or UNIX computer today than you have in recent years. Computers are quickly becoming the center of design work for both hardware and software engineers. The HP 1660C/CS logic analyzers have features to bring your test equipment and computer closer together.

Data and screen images can be stored in standard file formats (EPS, TIF, PCX, and ASCII) on the MS-DOS® flexible disk and read into your computer for documentation or further analysis. You can move the same files across an Ethernet LAN by using FTP or NFS commands.

X-Window software lets you operate the logic analyzer from a remote location across a LAN or WAN. The instrument display is duplicated (pixel for pixel) in an X11 window on your computer. A mouse and keyboard can control the logic analyzer from a computer, just like they do when plugged into the instrument.

## **Upgrade Kits to Help You Protect Your Investment**

You don't have to buy an entirely new instrument if you own an HP 1660A/AS series logic analyzer and want the features in the C/CS models. Just order the HP E2469A CPU upgrade kit. If you wish you had purchased a scope with your logic analyzer, that can be added, too. Order the HP E2460AS oscilloscope upgrade kit. Do you need more channels to support the microprocessor in your new embedded design? The HP E2460B, E2461B, and E2462B will upgrade the number of channels in your logic analyzer. Most models, excluding the HP 1664A, can be upgraded with one of these kits. The price of each upgrade kit includes installation and testing at a qualified Hewlett-Packard service center and extends the instrument warranty by one year.

An upgrade kit costs more than if you bought the new features as part of your original purchase. But, the upgrade kit can protect a large part of the investment you have already made.

#### **Key Literature and Ordering Information**

The HP 1660 and 1670 Series Benchtop Logic Analyzers Color Brochure, p/n 5964-3665E

The HP 1660 Series Benchtop Logic Analyzers Technical Specifications, p/n 5964-3664E

The HP 1670 Series Benchtop Logic Analyzers Technical Specifications, p/n 5964-3666E

The HP 1660 and 1670 Series Benchtop Logic Analyzers Demonstration Video Tape (10 min.), p/n 5965-0939E (NTSC), or 5965-0939EE (PAL)

See pages 402 and 403 in this catalog, or the above literature for ordering information.