### **SERVICE MANUAL**

# HP 1650B/1651B Logic Analyzer

#### **SERIAL NUMBERS**

This manual applies directly to instruments prefixed with serial number:

2924A

For additional information about serial numbers see INSTRUMENTS COVERED BY THIS MANUAL in Section 1.

© COPYRIGHT HEWLETT-PACKARD COMPANY/COLORADO DIVISION 1989 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO U.S.A.

ALL RIGHTS RESERVED

Manual Part No. 01650-90915 Microfiche Part No. 01650-90815

Printed in U.S.A. August 1989

#### Dear Customer:

You have probably heard from news reports and from your sales representative that as of November 1, 1999, four of Hewlett-Packard's businesses became a new company -- Agilent Technologies. The new company includes the following former HP businesses: test and measurement, semiconductor products, healthcare solutions and chemical analysis."

We at Agilent Technologies are working diligently to make this transition as seamless as possible for you, however, we are not able to make all changes immediately. As a result, the products and related documentation may be labeled with either the Hewlett-Packard name and logo or the Agilent Technologies name and logo. Rest assured that whatever logo you see, the information, products and services come from the same reliable source.

In addition, it is our sincere intent that the transition from Hewlett Packard to Agilent Technologies should have no impact on your warranties, service levels, or purchase volume credits.

For more information about this transition, please visit our website at: http://www.agilent.com, or contact your local sales representative. It has been our pleasure to work with you for the past 60 years as part of Hewlett-Packard. We look forward to continuing to serve you as Agilent Technologies for years to come.

#### Herstellerbescheinigung

Hiermit wird bescheinigt, daβ das Gerät/System in Übereinstimmung mit den Bestimmungen von Postverfügung 1046/84 funkentstört ist.

Der Deutschen Bundespost wurde das Inverkehrbringen dieses Gerätes/Systems angezeigt und die Berechtigung zur Überprüfung der Serie auf Einhaltung der Bestimmungen eingeräumt.

Zusatzinformation für Meβ- und Testgeräte

Werden Me $\beta$ - und Testgeräte mit ungeschirmten Kabeln und/oder in offenen Me $\beta$ aufbauten verwendet, so ist vom Betreiber sicherzustellen, da $\beta$  die Funkentstörbestimmungen unter Betriebsbedingungen an seiner Grundstücksgrenze eingehalten werden.

#### Manufacturer's declaration

This is to certify that this product meets the radio frequency interference requirements of directive 1046/84. The German Bundespost has been notified that this equipment was put into circulation and was granted the right to check the product type for compliance with these requirements.

Additional Information for Test and Measurement Equipment

Note: If test and measurement equipment is operated with unshielded cables and/or used for measurements on open set-ups, the user must insure that under these operating conditions, the radio frequency interference limits are met at the border of his premises.

#### **CERTIFICATION**

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology, to the extent allowed by the Institute's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard product is warranted against defects in material and workmanship for a period of one year from date of shipment. During the warranty period, Hewlett-Packard Company will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by HP. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### **ASSISTANCE**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

CWA789

### Safety Considerations

### General Operation

This is a Safety Class I instrument (provided with terminal for protective earthing). BEFORE APPLYING POWER verify that the power transformer primary is matched to the available line voltage, the correct fuse is installed, and Safety Precautions are taken (see the following warnings). In addition, note the instrument's external markings which are described under "Safety Symbols."

# General Warnings and Cautions

- BEFORE SWITCHING ON THE INSTRUMENT, the protective earth terminal of the instrument must be connected to the protective conductor of the (mains) powercord. The mains plug shall only be inserted in a socket outlet provided with a protective earth contact. The protective action must not be negated by the use of an extension cord (power cable) without a protective conductor (grounding). Grounding one conductor of a two-conductor outlet is not sufficient protection.

- Servicing instructions are for use by service-trained personnel. To avoid dangerous electric shock, do not perform any servicing unless qualified to do so.

- If this instrument is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the power source.

- Any interruption of the protective (grounding) conductor (inside or outside the instrument) or disconnecting the protective earth terminal will cause a potential shock hazard that could result in personal injury.

- Whenever it is likely that the protection has been impaired, the instrument must be made inoperative and be secured against any unintended operation.

- Only fuses with the required rated current, voltage, and specified type (normal blow, time delay, etc.) should be used. Do not use repaired fuses or short circuited fuseholders. To do so could cause a shock or fire hazard.

- Do not operate the instrument in the presence of flammable gasses or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

- Do not install substitute parts or perform any unauthorized modification to the instrument.

- Adjustments described in the manual are performed with power supplied to the instrument while

protective covers are removed. Energy available at many points may, if contacted, result in

personal injury.

- Any adjustment, maintenance, and repair of the opened instrument under voltage should be

avoided as much as possible, and when inevitable, should be carried out only by a skilled person

who is aware of the hazard involved.

- Capacitors inside the instrument may still be charged even if the instrument has been disconnected from its source of supply.

### **Safety Symbols**

Instruction manual symbol. The product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the product.

Indicates Hazardous Voltages

Earth terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood or met.

### **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition is published.

A software and/or firmware code may be printed before the date; this indicates the version level of the software and/or firmware of this product at the time of the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

Edition 1

August 1989

01650-90915

### **List of Effective Pages**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. If an update is incorporated when a new edition of the manual is printed, the change dates are removed from the bottom of the pages and the new edition date is listed in Printing History and on the title page.

| Pages | Effective Date |

|-------|----------------|

| all   | August 1989    |

### **Contents**

| Section 1: | General Information                     |      |

|------------|-----------------------------------------|------|

|            | Introduction                            | 1-1  |

|            | Instruments Covered by this Manual      |      |

|            | Safety Considerations                   |      |

|            | Product Description                     |      |

|            | Accessories Supplied                    |      |

|            | Accessories Available                   |      |

|            | Logic Analyzer Specifications           |      |

|            | Probes                                  |      |

|            | State Mode                              |      |

|            | Timing Mode                             |      |

|            | Operating Characteristics               |      |

|            | Probes                                  |      |

|            | Measurement Configurations              |      |

|            | State Analysis                          |      |

|            | Timing Analysis                         |      |

|            | Measurement and Display Functions       |      |

|            | General Characteristics                 |      |

|            | Operating Environment                   | 1-9  |

|            | Recommended Test Equipment              |      |

| Section 2: | Installation                            |      |

| occuon 2.  |                                         | 2.1  |

|            | Introduction                            |      |

|            | Safety Considerations                   |      |

|            | Initial Inspection                      |      |

|            | Power Requirements                      |      |

|            | Line Voltage Selection                  |      |

|            | Power Cable Operating Disk Installation |      |

|            | Applying Power                          |      |

|            | User Interface                          |      |

|            | HP-IB Interfacing.                      |      |

|            | HP-IB Address Selection                 |      |

|            | RS-232-C Interface                      |      |

|            | RS-232-C Interface                      |      |

|            | Operating Environment                   |      |

|            | Storage and Shipment                    |      |

|            | Tagging for Service                     |      |

|            | Original Packaging                      |      |

|            | Other Packaging                         |      |

|            | Cleaning Dequirements                   | 2 10 |

| Section 3: | Performance Tests                                            |     |  |  |  |

|------------|--------------------------------------------------------------|-----|--|--|--|

|            | Introduction                                                 |     |  |  |  |

|            | Recommended Test Equipment                                   |     |  |  |  |

|            | Test Connector                                               |     |  |  |  |

|            | Test Record.                                                 |     |  |  |  |

|            | Self Tests                                                   |     |  |  |  |

|            | Power-up Self Test                                           |     |  |  |  |

|            | Selectable Self Tests                                        |     |  |  |  |

|            | Performance Test Interval.                                   |     |  |  |  |

|            | Test Record.                                                 |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 1                     |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 2                     |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 2                     |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 4                     |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 5                     |     |  |  |  |

|            | Clock, Qualifier, and Data Inputs Test 6                     |     |  |  |  |

|            | Glitch Test                                                  |     |  |  |  |

|            | Threshold Accuracy Test.                                     |     |  |  |  |

|            |                                                              |     |  |  |  |

| Section 4: | Adjustments                                                  |     |  |  |  |

|            | Introduction                                                 | 4-1 |  |  |  |

|            | Calibration Interval                                         |     |  |  |  |

|            | Safety Requirements                                          |     |  |  |  |

|            | Recommended Test Equipment                                   |     |  |  |  |

|            | Instrument Warmup                                            |     |  |  |  |

|            | Calibration                                                  |     |  |  |  |

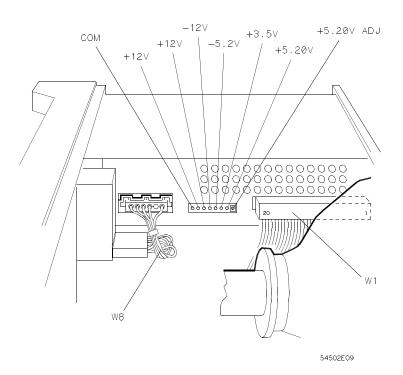

|            | Power Supply Assembly Adjustment                             |     |  |  |  |

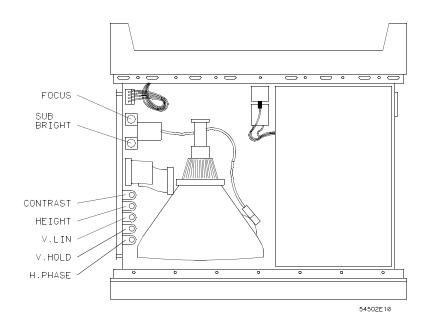

|            | CRT Monitor Assembly Adjustments                             |     |  |  |  |

|            | Intensity, Sub-bright, and Contrast Adjustment               |     |  |  |  |

|            | Focus Adjustment                                             |     |  |  |  |

|            | Horizontal Phase, Vertical Linearity, and Height Adjustments |     |  |  |  |

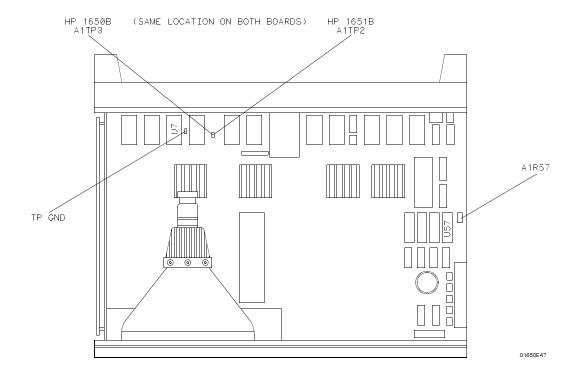

|            | System Board Assembly Threshold Adjustment                   |     |  |  |  |

|            | EXAMPLES                                                     |     |  |  |  |

|            |                                                              |     |  |  |  |

| Section 5: | Replaceable Parts                                            |     |  |  |  |

|            | Introduction                                                 | 5-1 |  |  |  |

|            | Abbreviations                                                | 5-1 |  |  |  |

|            | Replaceable Parts List                                       | 5-1 |  |  |  |

|            | Exchange Assemblies                                          |     |  |  |  |

|            | Ordering Information                                         |     |  |  |  |

|            | Direct Mail Order System                                     | 5-2 |  |  |  |

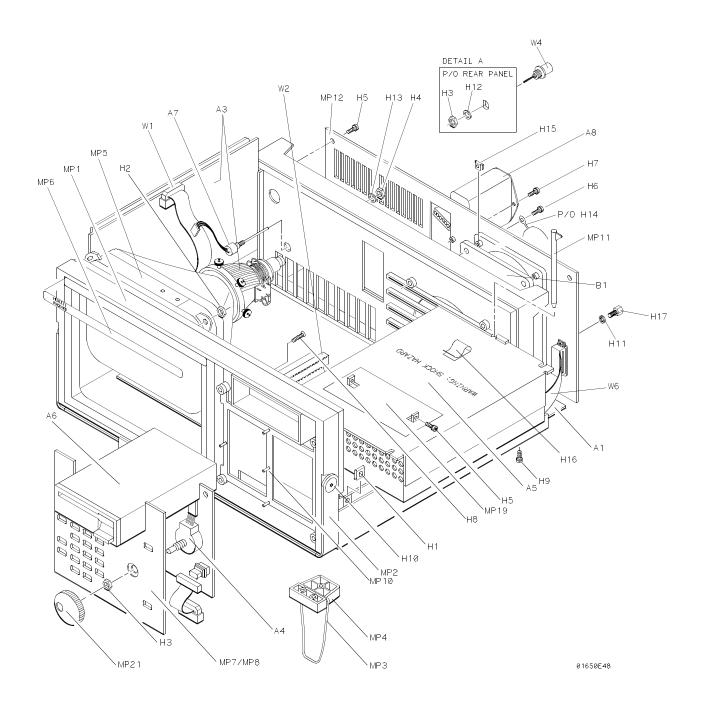

#### Section 6: Service Keypad and Knob Interface ...... 6-4 CRT Monitor Signals Check ...... 6-15 Keyboard Signals Check......6-16 Assembly Removal and Replacement . . . . . . . . . . . . 6-17 Removal and Replacement of System Assembly Board ...... 6-17 Removal and Replacement of CRT Monitor Assembly...... 6-19 Removal and Replacement of Power Supply...... 6-20 Removal and Replacement of Fan ...... 6-20 Removal and Replacement of Keyboard Assembly...... 6-21 Data Acquisition Self Test ...... 6-22

## **Contents**

| Section 1 | General Information                |      |

|-----------|------------------------------------|------|

|           | Introduction                       | 1-1  |

|           | Instruments Covered by this Manual | 1-1  |

|           | Safety Considerations              |      |

|           | Product Description                |      |

|           | Accessories Supplied               |      |

|           | Accessories Available              |      |

|           | Logic Analyzer Specifications      |      |

|           | Probes                             |      |

|           | State Mode                         |      |

|           | Timing Mode                        |      |

|           | Operating Characteristics          |      |

|           | Probes                             |      |

|           | Measurement Configurations         |      |

|           | State Analysis                     |      |

|           | Timing Analysis                    |      |

|           | Measurement and Display Functions  |      |

|           | General Characteristics            |      |

|           | Operating Environment              |      |

|           | Recommended Test Fauinment         | 1 10 |

### **General Information**

#### Introduction

This service manual explains how to test, adjust, and service the HP 1650B and HP 1651B Logic Analyzers. This manual is divided into six sections:

- General Information

- Installation

- Performance Tests

- Adjustments

- Replaceable Parts

- Service

This section of the manual includes a description of the HP 1650B/51B Logic Analyzers, specifications, options, available accessories, and recommended test equipment.

Listed on the title page of this manual is a microfiche part number. This number can be used to order 4 X 6 inch microfilm transparencies of the manual. Each microfiche contains up to 96 photo-duplicates of the manual pages. The microfiche package also includes the latest manual changes supplement and pertinent service notes.

# Instruments Covered by this Manual

The instrument serial number is on the rear panel. Hewlett-Packard uses a two part serial number consisting of a four-digit prefix and a five-digit suffix separated by a letter (0000A00000). The prefix is the same for all identical instruments and changes only when a modification is made that affects parts compatibility. The suffix is assigned and is different for each instrument. This manual applies directly to instruments with the serial prefix shown on the title page.

An instrument manufactured after the printing of this manual may have a serial number prefix that is not listed on the title page. This unlisted serial prefix indicates the instrument is different from those described in this manual. The manual for this newer instrument is accompanied by a manual changes supplement. This supplement contains "change information" that explains how to adapt the manual to the newer instrument.

In addition to change information, the supplement may contain information for correcting errors in the manual. To keep this manual as current and accurate as possible, Hewlett-Packard recommends that you periodically request the latest manual change supplement. The supplement for this manual is identified with the manual print date and part number, both of which appear on the manual title page. Complimentary copies of the supplement are available from Hewlett-Packard.

### Safety Considerations

This product is a Safety Class 1 instrument (provided with a protective earth terminal). Review the instrument and manual for safety markings and instructions before operating. Specific warnings, cautions, and instructions are placed wherever applicable throughout the manual. These precautions must be observed during all phases of operation, service, and repair of the instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this instrument.

Hewlett-Packard assumes no liability if the customer fails to comply with these safety requirements.

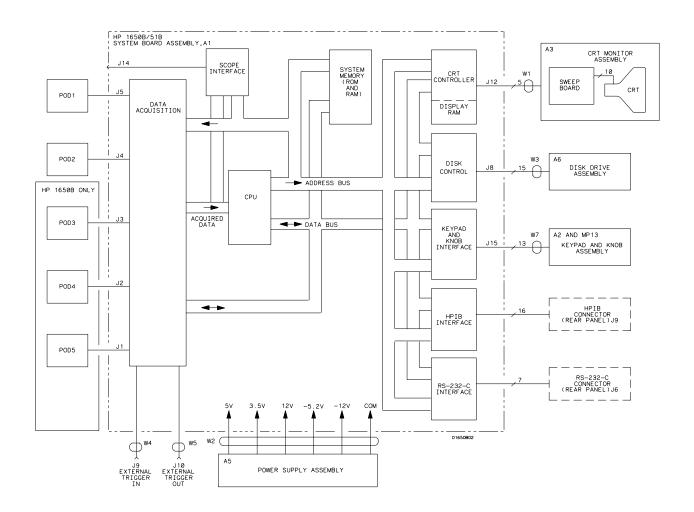

## Product Description

The HP 1650B is an 80-channel STATE/TIMING (35 MHz/100 MHz) logic analyzer, selectable in 16-channel groupings. The HP 1651B is a 32-channel STATE/TIMING (25 MHz/100 MHz) analyzer, also selectable in 16-channel groupings. The user interface for both models consists of a panel keyboard with an RPG knob and a 9-inch, white-phosphor, high-resolution CRT for information display. A 3.5-inch Sony disk drive, for setup storage and information retrieval, is integral to the analyzers. An RS-232-C port, HP-IB port, and external arming trigger are available on the rear panel. The RS-232-C and HP-IB ports are used for printer hardcopy or for logic analyzer control via a controller. Either port can be used for hardcopy or control.

The following items are other main features of the logic analyzers.

- Simultaneous state/state, or simultaneous state/timing analysis.

- Time interval; number of states; pattern search; minimum, maximum, and average time interval statistics.

- Transitional timing to store data only when there is a transition.

- Clock qualifiers, storage qualification, time and number of state tagging, and prestore.

- Small lightweight, passive probing.

## Accessories Supplied

The following accessories are supplied with the HP 1650B/51B Logic Analyzer.

- Woven probe cable (HP part number 01650-61607) with 40-pin connector on each side, 17 signal lines, 17 return lines, 2 power lines, and 2 power ground lines. Each power line supplies + 5 volts for preprocessor power. Each cable supplies 600 milliamperes with a maximum power available from the HP 1650B/51B of 2 amperes. Five probe cables are supplied with the HP 1650B and two are supplied with the HP 1651B.

- Probe Tip Assemblies (HP part number 01650-61608) that provide 16 data channels, 1 clock channel, and 1 ground lead per pod assembly. The probe input specifications are listed in table 1-1. Five Probe Tip Assemblies are supplied with the HP 1650B and two are supplied with the HP 1651B.

- Grabbers for the probe tip assemblies are supplied in packages of 20 (HP part number 5959-0288). 100 grabbers (5 packages) are supplied with the HP 1650B and 40 grabbers (2 packages) are supplied with the HP 1651B.

- Two operating system disks.

- One 2.3 meter (7.5 feet) power cord. See section 2 for available power cords.

- One operating and reference manual set.

- One service manual.

- One RS-232-C Loopback Connector.

### Accessories Available

The following accessories are available for the HP 1650B/51B Logic Analyzer.

- Termination Adapter HP Part Number 01650-63201.

- Soft Carrying Case HP Part Number 1540-1066.

- HP 1008A /006 Testmobile.

- HP 92192A 3.5-inch Microfloppy Disks (box of ten)

- Rackmount Kit HP Part Number 5061-6175.

- HP Model 10269C Probe interface to connect the logic analyzer directly to microprocessor preprocessors.

- Preprocessors for specific microprocessors and bus systems (for more information contact your Hewlett-Packard Sales and Service Office).

## Logic Analyzer Specifications

The following specifications are the performance standards or limits against which the HP 1650B/51B Logic Analyzer is tested.

**Probes** Minimum Swing: 600 mV peak-to-peak.

| Threshold Accuracy: | Voltage Range | Accuracy |

|---------------------|---------------|----------|

|                     |               |          |

$$-2.0V \text{ to} + 2.0V \pm 150 \text{ mV}$$

$$-9.9V$$

to  $-2.1V$   $\pm 300 \text{ mV}$

$$+ 2.1 \text{V to} + 9.9 \text{V} \pm 300 \text{ mV}$$

#### **State Mode**

Clock Repetition Rate: Single phase is 35 MHz maximum. With time or state counting, minimum time between states is 60 ns (16.67 MHz). Both mixed and demultiplexed clocking use master-slave clock timing; master clock must follow slave clock by at least 10 ns and precede the next slave clock by  $\geq$  50 ns.

**Clock Pulse Width:**  $\geq 10$  ns at threshold.

**Setup Time:** Data must be present prior to clock transition,  $\geq 10$  ns.

**Hold Time:** Data must be present after rising clock transition; 0 ns.

Data must be present after falling clock transition, 0 ns (HP 1651B); data must be present after falling L clock transition, 0 ns (HP 1650B); data must be present after falling J, K, M, and N clock transition, 1 ns (HP 1650B).

#### **Timing Mode**

Minimum Detectable Glitch: 5 ns wide at the threshold.

## Operating Characteristics

The following operating characteristics are are typical operating characteristics for the HP 1650B/51B Logic Analyzer.

**Probes**

**Input RC:** 100 K $\Omega \pm 2\%$  shunted by approximately 8 pF at the probe tip.

**TTL Threshold Preset:** + 1.6 volts.

**ECL Threshold Preset:** -1.3 volts.

**Threshold Range:** -9.9 to + 9.9 volts in 0.1V increments.

**Threshold Setting:** Threshold levels may be defined for pods 1 and 2 individually (HP 1651B). Threshold levels may be defined for pods 1, 2, and 3 on an individual basis and one threshold may be defined for pods 4 and 5 (HP 1650B).

**Minimum Input Overdrive:** 250 mV or 30% of the input amplitude, whichever is greater.

**Maximum Voltage:** ± 40 volts peak.

**Maximum Power Available Through Cables:** (600 mA) 2/3 amp @ 5V per cable; 2 amp @ 5V per HP 1650B/51B.

## Measurement Configurations

#### **Analyzer Configurations:**

| Analyzer 1 | Analyzer 2 |

|------------|------------|

| Timing     | Off        |

| Off        | Timing     |

| State      | Off        |

| Off        | State      |

| Timing     | State      |

| State      | Timing     |

| State      | State      |

| Off        | Off        |

**Channel Assignment:** Each group of 16 channels (a pod) can be assigned to Analyzer 1, Analyzer 2, or remain unassigned. The HP 1650B contains 5 pods; the HP 1651B contains 2 pods.

#### State Analysis MEMORY

Data Acquisition: 1024 samples/channel.

#### **Trace Specification**

**Clocks:** Five clocks (HP 1650B) or two clocks (HP 1651B) are available and can be used by either one or two state analyzers at any time. Clock edges can be ORed together and operate in single phase, two phase demultiplexing, or two phase mixed mode. Clock edge is selectable as positive, negative, or both edges for each clock.

**Clock Qualifier:** The high or low level of four ORed clocks (HP 1650B) or one clock (HP1651B) can be ANDed with the clock specification. Setup time: 20 ns; hold time: 5 ns.

**Pattern Recognizers:** Each recognizer is the AND combination of bit (0, 1, or X) patterns in each label. Eight pattern recognizers are available when one state analyzer is on. Four are available to each analyzer when two state analyzers are on.

Range Recognizers: Recognizes data which is numerically between or on two specified patterns (ANDed combination of 0s and/or 1s). One range term is available and is assigned to the first state analyzer turned on. The maximum size is 32 bits and on a maximum of 2 pods.

**Qualifier:** A user-specified term that can be anystate, nostate, a single pattern recognizer, range recognizer, or logical combination of pattern and range recognizers.

**Sequence Levels:** There are eight levels available to determine the sequence of events required for trigger. The trigger term can occur anywhere in the first seven sequence levels.

**Branching:** Each sequence level has a branching qualifier. When satisfied, the analyzer will restart the sequence or branch to another sequence level.

**Occurrence Counter:** Sequence qualifier may be specified to occur up to 65535 times before advancing to the next level.

**Storage Qualification:** Each sequence level has a storage qualifier that specifies the states that are to be stored.

**Enable/Disable:** Defines a window of post-trigger storage. States stored in this window can be qualified.

**Prestore:** Stores two qualified states that precede states that are stored.

#### **Tagging**

**State Tagging:** Counts the number of qualified states between each stored state. Measurement can be shown relative to the previous state or relative to trigger. Maximum count is 4.4 X (10 to the 12th power).

**Time Tagging:** Measures the time between stored states, relative to either the previous state or the trigger. Maximum time between states is 48 hours.

With tagging on, the acquisition memory is halved; minimum time between states is 60 ns.

#### **Symbols**

**Pattern Symbols:** User can define a mnemonic for the specific bit pattern of a label. When data display is SYMBOL, mnemonic is displayed where the bit pattern occurs. Bit pattern can include 0s, 1s, and don't cares.

**Range Symbols:** User can define a mnemonic covering a range of values. Bit pattern for lower and upper limits must be defined as a pattern of 0s and 1s. When data display is SYMBOL, values within the specified range are displayed as mnemonic + offset from base of range.

Number of Pattern and Range Symbols: 200 total used for both analyzers.

Symbols can be down-loaded over RS-232-C or HP-IB.

#### Timing Analysis Transitional Timing Mode

Sample is stored in acquisition memory only when the data changes. A time tag stored with each sample allows reconstruction of waveform display. Time covered by a full memory acquisition varies with the number of pattern changes in the data.

Sample Period: 10 ns.

Maximum Time Covered By Data: 5000 seconds.

Minimum Time Covered by Data: 10.24 us.

#### **Glitch Capture Mode**

Data sample and glitch information stored every sample period.

**Sample Period:** 20 ns to 50 ms in a 1-2-5 sequence dependent on sec/div and delay settings.

Memory Depth: 512 samples/channel.

Time Covered by Data: Sample period X 512.

#### **Waveform Display**

Sec/div: 10 ns to 100 s; 0.01% resolution.

**Delay:** -2500 s to 2500 s; presence of data dependent on the number of transitions in data between trigger and trigger plus delay (transitional timing).

Accumulate: Waveform display is not erased between successive acquisitions.

**Overlay Mode:** Multiple channels can be displayed on one waveform display line. Primary use is to view summary of bus activity.

Maximum Number Of Displayed Waveforms: 24

#### **Time Interval Accuracy**

Channel to Channel Skew: 4 ns typical.

**Time Interval Accuracy:**  $\pm$  (sample period + channel-to-channel skew + 0.01% of time interval reading).

#### **Trigger Specification**

**Asynchronous Pattern:** Trigger on an asynchronous pattern less than or greater than specified duration. Pattern is the logical AND of specified low, high, or don't care for each assigned channel. If pattern is valid but duration is invalid, there is a 20 ns reset time before looking for patterns again.

**Greater Than Duration:** Minimum duration is 30 ns to 10 ms with 10 ns or 0.01% resolution, whichever is greater. Accuracy is + 0 ns to -20 ns. Trigger occurs at pattern + duration.

**Less Than Duration:** Maximum duration is 40 ns to 10 ms with 10 ns or 0.01% resolution, whichever is greater. Pattern must be valid for at least 20 ns. Accuracy is + 20 ns to -0 ns. Trigger occurs at the end of the pattern.

**Glitch/Edge Triggering:** Trigger on glitch or edge following valid duration of asynchronous pattern while the pattern is still present. Edge can be specified as rising, falling or either. Less than duration forces glitch and edge triggering off.

## Measurement and Display Functions

#### **Autoscale (Timing Analyzer Only)**

Autoscale searches for and displays channels with activity on the pods assigned to the timing analyzer.

#### **Acquisition Specifications**

**Arming:** Each analyzer can be armed by the run key, the other analyzer, or the external trigger on rear panel.

**Trace Mode:** Single mode acquires data once per trace specification; repetitive mode repeats single mode acquisitions until stop is pressed or until time interval between two specified patterns is less than or greater than a specified value, or within or not within a specified range. There is only one trace mode when two analyzers are on.

#### Labels

Channels may be grouped together and given a six character name. Up to 20 labels in each analyzer may be assigned with up to 32 channels per label. Primary use is for naming groups of channels such as address, data, and control busses.

#### **Indicators**

**Activity Indicators:** Provided in the Configuration, State Format, and Timing Format menus for identifying high, low, or changing states on the inputs.

**Markers:** Two markers (X and 0) are shown as dashed lines on the display.

**Trigger:** Displayed as a vertical dashed line in the timing waveform display and as line 0 in the state listing display.

#### **Marker Functions**

**Time Interval:** The X and 0 markers measure the time interval between one point on a timing waveform and trigger, two points on the same timing waveform, two points on different waveforms, or two states (time tagging on).

**Delta States (State Analyzer Only):** The X and 0 markers measure the number of tagged states between one state and trigger, or between two states.

**Patterns:** The X and 0 markers can be used to locate the nth occurrence of a specified pattern before or after trigger, or after the beginning of data. The 0 marker can also find the nth occurrence of a pattern before or after the X marker.

**Statistics:** X to 0 marker statistics are calculated for repetitive acquisitions. Patterns must be specified for both markers and statistics are kept only when both patterns can be found in an acquisition. Statistics are minimum X to 0 time, maximum X to 0 time, average X to 0 time, and ratio of valid runs to total runs.

#### **Run/Stop Functions**

Run: Starts acquisition of data in specified trace mode.

**Stop:** In single trace mode or the first run of a repetitive acquisition, STOP halts acquisition and displays the current acquisition data. For subsequent runs in repetitive mode, STOP halts acquisition of data and does not change current display.

#### **Data Display/Entry**

**Display Modes:** State listing; timing waveforms; interleaved, time-correlated listing of two state analyzers (time tagging on); time-correlated state listing and timing waveform display (state listing in upper half, timing waveform in lower half, and time tagging on).

**Timing Waveform:** Pattern readout of timing waveforms at X or 0 marker.

**Bases:** Binary, Octal, Decimal, Hexadecimal, ASCII (display only), and User-defined symbols.

## General Characteristics

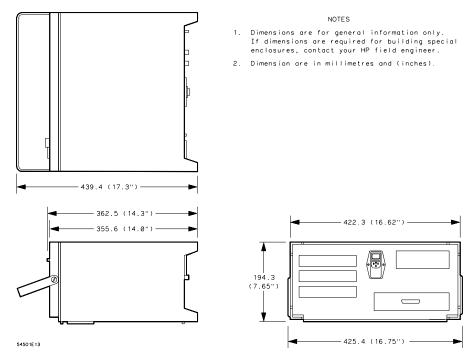

The following general characteristics for the HP 1650B/51B are the environmental operating conditions, shipping weights, and instrument dimensions.

### Operating Environment

**Temperature:** Instruments,  $0^{\circ}$  to  $55^{\circ}$  C (+  $32^{\circ}$  to  $131^{\circ}$ F); probes and cables,  $0^{\circ}$  to  $65^{\circ}$ C (+  $32^{\circ}$  to  $149^{\circ}$ F). Recommended temperature range for disk media,  $10^{\circ}$  to  $50^{\circ}$ C (+  $50^{\circ}$  to  $149^{\circ}$ F).

**Humidity:** Instruments up to 95% relative humidity at  $+40^{\circ}$ C; (104°F). Recommended humidity range for disk media, 8% to 80% relative humidity at  $+40^{\circ}$ C ( $+104^{\circ}$ F).

**Altitude:** To 4600 m (15,000 ft).

Vibration:

**Operating:** Random vibration 5-500 Hz, 10 minutes per axis, &2.41 g (rms).

**Non-operating:** Random vibration 5-500 Hz, 10 minutes per axis, & 2.41 g (rms); and swept sine resonant search, 5-500 Hz, 0.75 g (0-peak), 5 minute resonant dwell @ 4 resonances per axis.

**Weight:** 10.0 kg (22 lbs) net; 18.2 kg (40 lbs) shipping.

Power: 115V/230V, 48-66 Hz, 200 W maximum.

**Dimensions:** See outline drawing below.

### Recommended Test Equipment

Table 1-1 lists the test equipment required to test performance, make adjustments, and troubleshoot the HP 1650B/51B Logic Analyzers. The table includes the critical specifications of the test equipment and lists each procedure in which the equipment is required. Other equipment may be substituted if it meets or exceeds the critical specifications listed in the table.

**Table 1-1. Recommended Test Equipment**

| <b>Equipment Required</b>               | Critical Specifications                                                                                  | Recommended Model           | Use * |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------|-------|

| Oscilloscope dual channel dc to 300 MHz |                                                                                                          | HP 54502A                   | P,T   |

| Pulse<br>Generator                      | 5 ns pulse width 20 ns period 1.3 ns risetime double pulse 100 kHz Repetition Rate Overshoot: 5% of Amp. | HP 8161A/020                | P     |

| Power<br>Supply                         | + or - 10.2 V output<br>current: 0 - 0.4 amperes                                                         | HP 6216B                    | P     |

| Adapter                                 | BNC(f)-to-Dual Banana                                                                                    | HP Part Number<br>1251-2277 | P     |

| DMM                                     | 5.5 digit resolution                                                                                     | HP 3478A                    | A     |

| Resistor                                | 2 ohms, 25 watts                                                                                         | HP Part Number<br>0811-1390 | Т     |

| BNC Cable (2)                           | 50 ohms with UG-88C/U BNC (m) connectors                                                                 | HP 10503A                   | P     |

| BNC Adapter (2)                         | BNC tee (m) (f) (f)                                                                                      | HP Part Number<br>1250-0781 | P     |

| BNC Feedthrough                         | 50 ohm BNC                                                                                               | HP 10100C                   | P     |

| * P = Performance                       | e Tests, A = Adjustments, T = Troubleshoo                                                                |                             |       |

| Section 2 | Installation                |      |

|-----------|-----------------------------|------|

|           | Introduction                | 2-1  |

|           | Safety Considerations       | 2-1  |

|           | Initial Inspection          | 2-1  |

|           | Power Requirements          |      |

|           | Line Voltage Selection      |      |

|           | Power Cable                 |      |

|           | Operating Disk Installation |      |

|           | Applying Power              |      |

|           | User Interface              |      |

|           | HP-IB Interfacing           |      |

|           | HP-IB Address Selection     |      |

|           | RS-232-C Interface          |      |

|           | RS-232-C Configuration      |      |

|           | Operating Environment       |      |

|           | Storage and Shipment        |      |

|           | Tagging for Service         |      |

|           | Original Packaging          |      |

|           | Other Packaging             |      |

|           | Cleaning Requirements       | 2 10 |

### Installation

#### Introduction

This section of the manual contains information and instructions necessary for setting up the HP 1650B/51B Logic Analyzer. This includes inspection procedures, power requirements, hardware connections and configurations, and packaging information.

### Safety Considerations

The safety symbols used with Hewlett-Packard instruments are illustrated in the front of this manual. WARNING and CAUTION symbols and instructions should be reviewed before operating the instrument. These warnings and cautions must be followed for your own protection and to avoid damaging the instrument.

### Initial Inspection

Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, keep it until the contents of the shipment have been checked for completeness and the instrument has been checked mechanically and electrically. The contents of the shipment are listed under "Accessories Supplied" in Section 1. If the contents are incomplete, if there is mechanical damage or defect, or if the instrument does not operate properly, notify the nearest Hewlett-Packard office. If the shipping container is damaged, or the cushioning materials show signs of stress, notify the carrier as well as the Hewlett-Packard office. Keep the shipping materials for the carrier's inspection. The Hewlett-Packard office will arrange for repair or replacement at HP option without waiting for claim settlement.

# Power Requirements

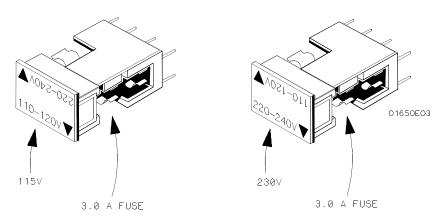

The HP 1650B/51B Logic Analyzer requires a power source of either 115 Vac or 230 Vac, -22% to + 10%; single phase, 48 to 66 Hz, 200 Watts maximum power.

Caution **W**

BEFORE CONNECTING POWER TO THIS INSTRUMENT, be sure the Line Voltage Select switch on the rear panel of the instrument is set properly and the correct fuse is installed.

## Line Voltage Selection

When shipped from the factory, the line voltage selector is set and an appropriate fuse is installed for operating the instrument in the country of destination.

To operate the instrument from a power source other than the one set at the factory:

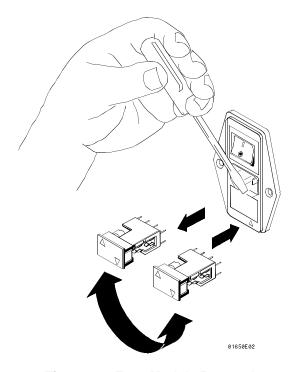

- 1. Turn the rear power switch to the OFF position and remove the power cord from the instrument.

- 2. Remove the fuse module by carefully prying it at the top center of the module until you can grasp it and pull it out by hand as shown below.

Figure 2-1. Fuse Module Removal

3. Reinsert the fuse module with the arrows aligned for your application. See fuse module below.

Figure 2-2. Fuse Module

4. Reconnect the power cord, turn the rear power switch to the ON position, and continue normal operation.

#### **Power Cable**

This instrument is equipped with a three-wire power cable. When connected to an appropriate AC power outlet, this cable grounds the instrument cabinet. The type of power cable plug shipped with the instrument depends on the country of destination. See Table 2-1 for the option numbers of available power cables and plug configurations.

## Operating Disk Installation

This instrument is shipped with a yellow protective disk in the disk drive. Before applying power to the instrument, remove the protective disk from the disk drive and install the operating disk. Reinstall the protective disk whenever the instrument is to transported.

### **Applying Power**

When power is applied to the HP 1650B/51B, a power-up self test is automatically performed. For information on the power-up self test, refer to section 3.

**Table 2-1. Power Plug Configurations**

| PLUG TYPE             | CABLE<br>PART NO.                   | PLUG DESCRIPTION                                          | LENGTH<br>IN/CM            | COLOR                                | COUNTRY                                                                                          |

|-----------------------|-------------------------------------|-----------------------------------------------------------|----------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|

| 0PT 900<br>250V       | 8120-1351<br>8120-1703              | Straight *BS1363A<br>90°                                  | 90/228<br>90/228           | Gray<br>Mint Gray                    | United Kingdom,<br>Cyprus,<br>Nigeria,<br>Zimbabwe,<br>Singapore                                 |

| OPT 901               | 8120-1369<br>8120-0696              | Straight *NZSS198/ASC 90°                                 | 79/200<br>87/221           | Gray<br>Mint Gray                    | Australia<br>New Zealand                                                                         |

| OPT 902               | 8120-1689<br>8120-1692<br>8120-2857 | Straight *CEE7-Y11<br>90°<br>Straight (Shielded)          | 79/200<br>79/200<br>79/200 | Mint Gray<br>Mint Gray<br>Coco Brown | East and West Europe,<br>Saudi Arabia,<br>So. Africa,<br>India (Unpolarized<br>in many nations)  |

| OPT 903**             | 8120-1378<br>8120-1521<br>8120-1992 | Straight *NEMA5-15P<br>90°<br>Straight (Medical)<br>UL544 | 90/228<br>90/228<br>96/244 | Jade Gray<br>Jade Gray<br>Black      | United States,<br>Canada,<br>Mexico,<br>Phillipines,<br>Taiwan                                   |

| OPT 904**             | 8120-0698                           | Straight *NEMA6-15P                                       | 90/228                     | Black                                | United States,<br>Canada                                                                         |

| OPT 905               | 8120-1396<br>8120-1625              | CEE22-V1<br>(System Cabinet Use)<br>250V                  | 30/76<br>96/244            | Jade Gray                            | For interconnecting<br>system components and<br>peripherals.<br>United States and<br>Canada only |

| OPT 906               | 8120-2104<br>8120-2296              | Straight *SEV1011<br>1959—24507<br>Type 12<br>90°         | 79/200<br>79/200           | Mint Gray<br>Mint Gray               | Switzerland                                                                                      |

| OPT 912               | 8120-2956<br>8120-2957              | Straight *DHCK107<br>90°                                  | 79/200<br>79/200           | Mint Gray<br>Mint Gray               | Denmark                                                                                          |

| OPT 917               | 8120-4211<br>8120-4600              | Straight SABS164<br>90°                                   | 79/200<br>79/200           | Jade Gray                            | Republic of South Africa<br>India                                                                |

| OPT 918               | 8120-4753<br>8120-4754              | Straight Miti<br>90°                                      | 90/230<br>90/230           | Dark Gray                            | Japan                                                                                            |

| 100V<br>Rev . 11N0V88 |                                     |                                                           |                            |                                      | ART00019                                                                                         |

<sup>\*</sup>Part number shown for plug is industry identifier for plug only. Number shown for cable is HP part number for complete cable including plug.

\*\*These cords are included in the CSA certification approval of the equipment.

E=Earth Ground

L=Line

N=Neutral

#### **User Interface**

The front-panel user interface of the HP 1650B/51B consists of front-panel keys, the KNOB, and display. The interface allows configuration of each analyzer (machine) within the logic analyzer. It also displays acquired data and measurement results.

Use the front-panel interface with the following process:

- select the desired menu with menu keys

- place the cursor on the desired field within the menu by rotating the KNOB

- display the field options or current data by pressing the SELECT key

- select the desired option by rotating the KNOB or entering new data by using the KNOB or the keypad

- Start and stop data acquisition by using the RUN and STOP keys

# HP-IB Interfacing

The Hewlett-Packard Interface Bus (HP-IB) is Hewlett-Packard's implementation of IEEE Standard 488-1978, "Standard Digital Interface for Programming Instrumentation." HP-IB is a carefully defined interface that simplifies the integration of various instruments and computers into systems. The interface makes it possible to transfer messages between two or more HP-IB compatible devices. HP-IB is a parallel bus of 16 active signal lines divided into three functional groups according to function.

Eight signal lines, called data lines, are in the first functional group. The data lines are used to transmit data in coded messages. These messages are used to program the instrument function, transfer measurement data, and coordinate instrument operation. Input and output of all messages, in bit parallel-byte serial form, are also transferred on the data lines. A 7-bit ASCII code normally represents each piece of data.

Data is transferred by means of an interlocking "Handshake" technique which permits data transfer (asynchronously) at the rate of the slowest active device used in that transfer. The data byte control lines coordinate the handshaking and form the second functional group.

The remaining five general interface management lines (third functional group) are used to manage the devices connected to the HP-IB. This includes activating all connected devices at once, clearing the interface, and other operations.

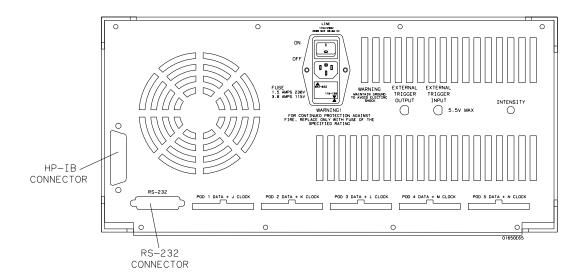

The HP-IB connector and on the rear panel are shown in figure 2-3.

Figure 2-3. HP 1650B Rear Panel

## **HP-IB Address Selection**

Each instrument connected to the HP-IB interface bus requires a unique address. The address provides a method for the system computer to select individual instruments on the bus. The address of the HP 1650B/51B defaults at power up to decimal "07". The corresponding ASCII code is a listen of """ and a talk address of "G." To change the address of the HP 1650B/51B proceed as follows:

- 1. Press the I/O key on the front-panel keypad and the I/O menu will appear on screen.

- 2. Rotate the KNOB until "I/O Port Configuration" is highlighted.

- 3. Press the SELECT key and the External I/O Port Configuration menu will appear on screen.

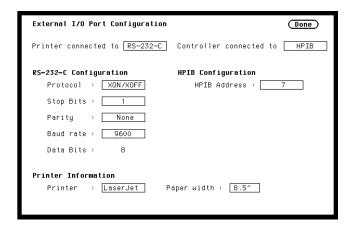

Figure 2-4. External I/O Port Configuration Menu

- 4. Select the HP-IB Address field with the KNOB and press the SELECT key.

- 5. When the pop-up field appears on screen, rotate the KNOB to select the desired HP-IB address.

- 6. Press the SELECT key to enter the new address.

- 7. Select the DONE field in the upper-right corner with the KNOB to exit the External I/O Port Configuration menu.

### RS-232-C Interface

The HP 1650B/51B interfaces with RS-232-C communication lines through a standard 25 pin D connector. The HP 1650B/51B is compatible with RS-232-C protocol. When a hardwire handshake method is used, the Data Terminal Ready (DTR) line (pin 20 on the Computer/Modem connector) is used to signal whether space is available in the logical I/O buffer for more data. Pin outs of the RS-232-C connectors are listed in table 2-4.

Table 2-1. RS-232-C Signal Definitions

| Pin No. | Function                  | Standard | Signal Direction and Level                                                                     |

|---------|---------------------------|----------|------------------------------------------------------------------------------------------------|

| 1       | Protective Ground         | AA       | Not applicable                                                                                 |

| 2       | Transmitted Data (TD)     | BA       | Data from Logic Analyzer High = Space = "0" = + 12 V Low = Mark = "1" = -12 V                  |

| 3       | Received Data (RD)        | BB       | Data to Logic Analyzer  High = Space = "0" = + 3 V to + 25 V  Low = Mark = "1" = -3 V to -25 V |

| 4       | Request to Send (RTS)     | CA       | Signal from Logic Analyzer High = ON = + 12 V Low = OFF = -12 V                                |

| 5       | Clear to Send (CTS)       | СВ       | Signal to Logic Analyzer High = ON = + 3 V to + 12 V Low = OFF = -3 V to -25 V                 |

| 6       | Data Set Ready (DSR)      | CC       | Signal to Logic Analyzer High = ON = + 3 V to + 25 V Low = OFF = -3 V to -25 V                 |

| 7       | Signal Ground             | AB       | Not applicable                                                                                 |

| 8       | Data Carrier Detect (DCD) | CF       | Signal to Logic Analyzer High = ON = + 3 V to + 25 V Low = OFF = -3 V to -25 V                 |

| 20      | Data Terminal Ready (DTR) | CD       | Signal from Logic Analyzer High = ON = + 12 V Low = OFF = -12 V                                |

| 23      | Data Signal Rate Selector | CH/CI    | Signal from Logic Analyer<br>Always High = ON = + 12 V                                         |

# RS-232-C Configuration

At power up, the RS-232-C interface is configured as shown in previous figure. To change the RS-232-C configuration:

- 1. Press the I/O key on the front-panel keypad and the I/O menu will appear on screen.

- 2. Rotate the KNOB until "I/O Port Configuration" is highlighted.

- 3. Touch the SELECT key and the External I/O Port Configuration menu will appear on screen.

- 4. Using the KNOB and SELECT key, configure the RS-232-C interface as desired.

- 5. Select the DONE field in the upper-right corner with the KNOB to exit the External I/O Port Configuration menu.

## Operating Environment

The operating environment for the HP 1650B/51B is described in table 1-2. Note the non-condensing humidity limitation. Condensation within the instrument cabinet can cause poor operation or malfunction. Protection should be provided against temperature extremes which cause condensation within the instrument.

The HP 1650B/51B operates at all specifications within the temperature and humidity range given in table 1-2.

## Storage and Shipment

The instrument may be stored or shipped in environments within the following limits:

Temperature:-40 degrees C to + 75 degrees C.

Humidity:Up to 90% at 65 degrees C.

Altitude:Up to 15,300 metres (50,000 feet).

## Tagging for Service

If the instrument is to be shipped to a Hewlett-Packard office for service or repair, attach a tag to the instrument identifying the owner, address of the owner, complete instrument model and serial numbers, and a description of the service required.

# Original Packaging

If the original packaging material is unavailable or unserviceable, materials identical to those used in factory packaging are available through Hewlett-Packard offices. If the instrument is to be shipped to a Hewlett-packard office for service, attach a tag identifying the owner, address of the owner, complete instrument model and serial numbers, and a description of the service required. Mark the container FRAGILE to ensure careful handling. In any correspondence, refer to the instrument by model number and full serial number.

# Other Packaging

The following general instructions should be followed for repacking the instrument with commercially available materials.

- Remove discs from disk drives and install yellow shipping discs.

- Wrap the instrument in heavy paper or plastic.

- Use a strong shipping container. A double-wall carton made of 350 lb. test material is adequate.

- Use a layer of shock-absorbing material 70 to 100 mm (3 to 4 inches) thick around all sides of the instrument to provide firm cushioning and prevent movement inside the container. Protect the control panel with cardboard.

- Seal the shipping container securely.

- Mark the shipping container FRAGILE to ensure careful handling.

- In any correspondence, refer to the instrument by model number and serial number.

### Cleaning Requirements

Use MILD SOAP AND WATER to clean the HP 1650B/51B cabinet and front panel. Care must be taken to not use a harsh soap which may damage the water-base paint finish of the instrument.

## **Contents**

| Performance Tests                     |                                                                                                                           |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Introduction                          | 3-1                                                                                                                       |

| Recommended Test Equipment            | 3-1                                                                                                                       |

| Test Connector                        |                                                                                                                           |

| Test Record                           | 3-1                                                                                                                       |

| Self Tests                            | 3-2                                                                                                                       |

|                                       |                                                                                                                           |

| Selectable Self Tests                 |                                                                                                                           |

| Performance Test Interval             | 3-3                                                                                                                       |

| Test Record                           | 3-3                                                                                                                       |

|                                       |                                                                                                                           |

| · · ·                                 |                                                                                                                           |

| · · ·                                 |                                                                                                                           |

|                                       |                                                                                                                           |

| •                                     |                                                                                                                           |

| · · · · · · · · · · · · · · · · · · · |                                                                                                                           |

|                                       |                                                                                                                           |

|                                       |                                                                                                                           |

|                                       | Introduction. Recommended Test Equipment. Test Connector Test Record. Self Tests Power-up Self Test Selectable Self Tests |

### **Performance Tests**

#### Introduction

These procedures test the electrical performance of the logic analyzer by using the specifications in table 1-1 as the performance standards. All tests may be performed without access to the interior of the instrument.

### Recommended Test Equipment

Equipment required for the performance tests in this section is listed in the Recommended Test Equipment table in Section 1. Any equipment that satisfies the critical specification listed in the table may be substituted for the recommended model.

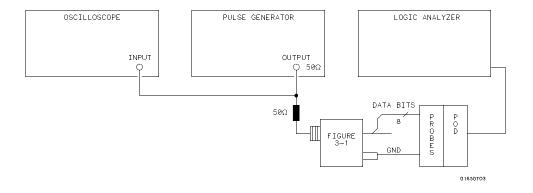

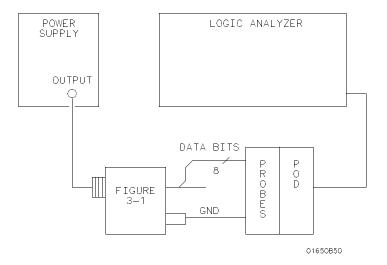

#### **Test Connector**

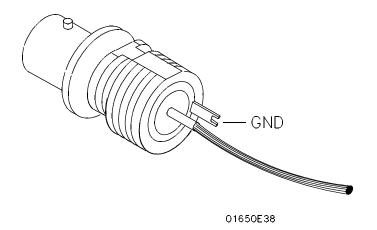

The performance tests and adjustments require connecting pulse generator outputs to probe pod inputs. Figure 3-1 is a test connector that may be built to allow testing of multiple channels (up to eight at one time). The test connector consists of a BNC connector and a length of wire. Connecting more than eight channels to the test connector at a time will induce loading of the circuit and true signal representation will degrade. Test results may not be accurate if more than eight channels are connected to the test connector.

The Hewlett-Packard part number for the BNC connector in figure below is 1250-1032. An equivalent part may be used in place of the Hewlett-Packard part.

Figure 3-1. Test Connector

#### **Test Record**

The results of the performance tests may be tabulated on the Test Record provided at the end of this section. The Test Record lists the performance tests and provides an area to mark whether the pod passed or failed the test. The results recorded in the table at incoming inspection may be used for later comparisons of the tests during periodic maintenance, troubleshooting, and after repairs or adjustments.

#### **Self Tests**

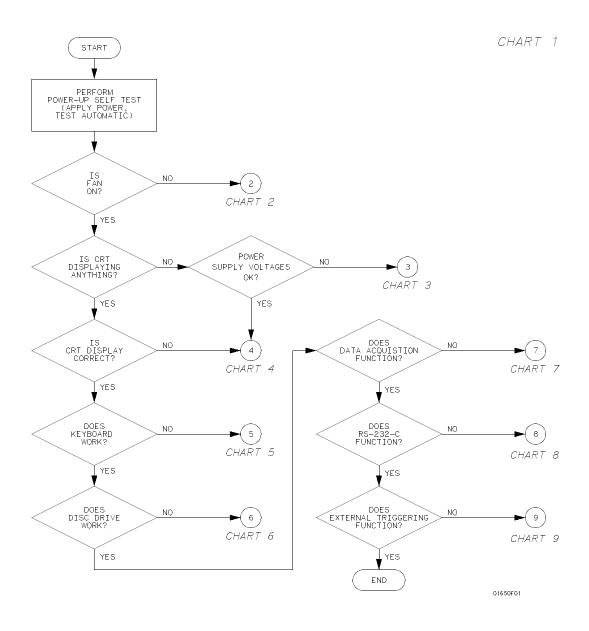

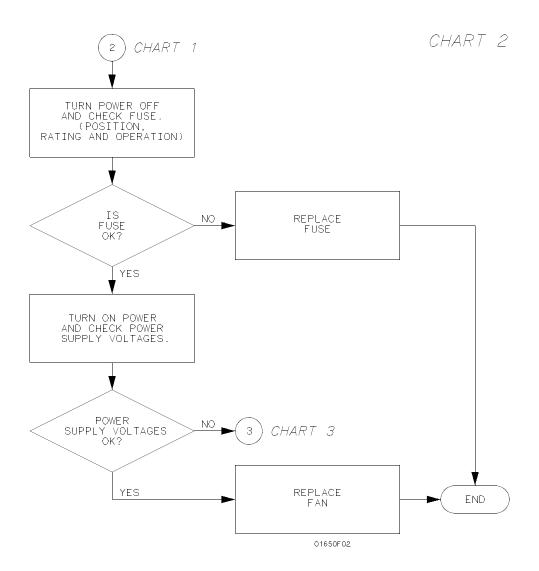

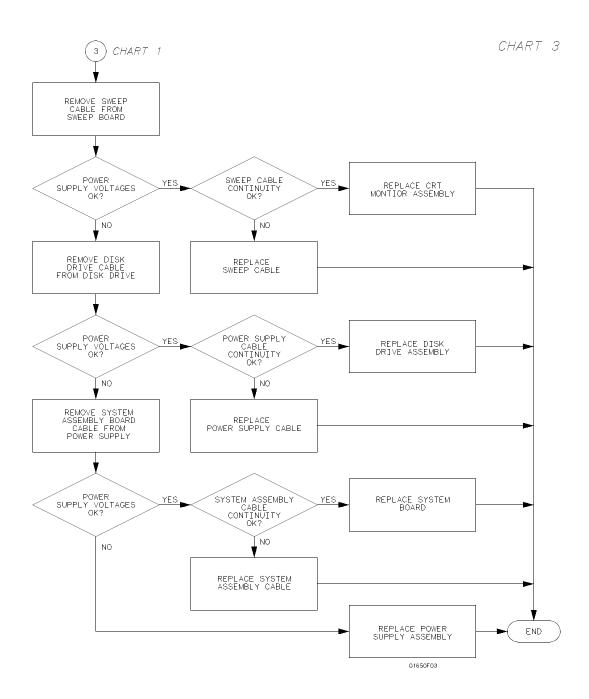

The power-up self test is automatically performed upon applying power to the logic analyzer. Since the performance tests require test equipment, self tests may be performed individually to provide a higher level of confidence that the instrument is operating properly. A message that the instrument has failed the test will appear if any problem is encountered during the test. The individual self tests may be performed for functions listed in the self test menu which is invoked via the I/O menu. The HP 1650B/51B self test is located on the operating system disk and is required to run the tests.

#### **Power-up Self Test**

The power-up self test is automatically invoked at power-up of the HP 1650B/51B Logic Analyzer. The revision number of the operating system firmware is given in the upper right of the screen during the power-up self test. As each test completes, either passed or failed is printed in front of the name of the test in the following manner:

#### PERFORMING POWER-UP SELF TESTS

passed ROM test

passed RAM test

passed Interrupt test

passed Display test

passed Keyboard test

passed Acquisition test

passed Threshold test

passed Disk test

#### LOADING SYSTEM FILE

As indicated by the last message, the HP 1650B/51B automatically loads the operating system disk in the disk drive. If the operating system disk is not in the disk drive, the message SYSTEM DISC NOT FOUND is displayed at the bottom of the screen and NO DISK is displayed in front of disk test in place of "passed".

If the above message appears, turn off the instrument, insert the operating system disk into the disk drive, and again apply power.

# Tests

**Selectable Self** Seven self tests may be invoked individually via the Self Test menu. The seven selectable self tests are:

- Data Acquisition

- RS-232-C

- External Trigger BNCs

- Keyboard

- RAM

- ROM

- · Disk Drive

- Cycle through all tests

The required test is selected by moving the cursor to the test and pressing the front panel SELECT key. A pop-up menu appears with a description of the test to be performed. The self test does not begin until the cursor is placed on Execute and the front panel SELECT key is pressed.

After the test has been completed, either Passed, Failed, or Tested is displayed on the Self Test menu in front of the test. These tests are used as troubleshooting aids. Section 6 contains information on the individual tests used for troubleshooting.

## **Performance Test Interval**

The calibration cycle for the logic analyzer is two years, therefore, periodic performance verification of the HP 1650B/51B is recommended at two year intervals. The instrument's performance should be verified after it has been serviced, or if improper operation is suspected. Calibration should be performed before any performance verification tests. Further checks requiring access to the interior of the instrument are included in the adjustment section, but are not required for the performance verification.

#### **Test Record**

The results of the performance tests may be tabulated on the Test Record provided at the end of this section. The Test Record lists the performance tests and provides an area to mark whether the pod passed or failed the test. The results recorded in the table at incoming inspection may be used for later comparisons of the tests during periodic maintenance, troubleshooting, and after repairs or adjustments.

## Clock, Qualifier, and Data Inputs Test 1

**Description:** This test verifies maximum clock rate with counting mode for the HP 1650B/51B. This test also verifies the setup and hold times for the falling edge of the HP 1650B L clock specification, and the falling edge of the HP 1651B J and K clock specification.

**Specification:** Clock repetition rate: with time or state counting mode on, minimum time between states is 60 ns.

Setup time: Data must be present prior to clock transition;  $\geq 10$  ns.

HP 1650B hold time: Data must be present after falling edge of L clock transition; 0 ns.

HP 1651B hold time: Data must be present after falling edge of J and K clock transition; 0 ns.

#### **Equipment:**

```

Pulse Generator

HP 8161A/020

Oscilloscope

HP 54502A

50 Ohm Feedthru (2)

HP 10100C

Test Connector see figure 3-1

(2)

```

#### Procedure:

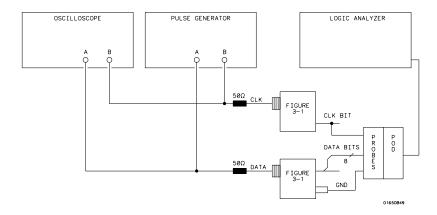

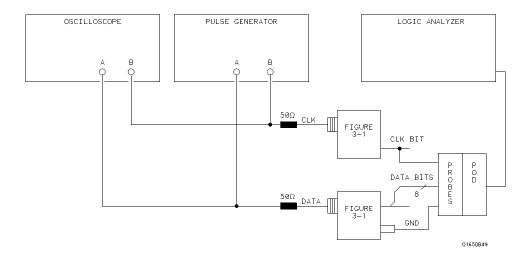

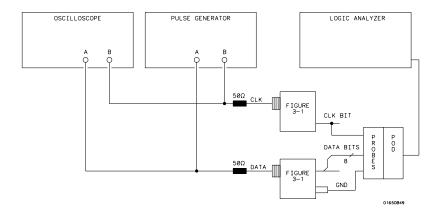

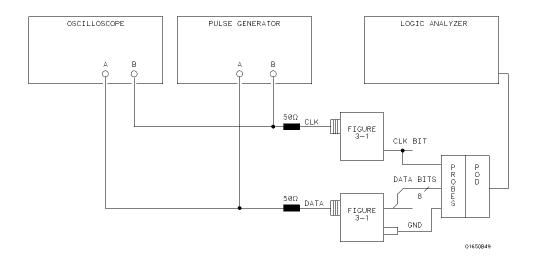

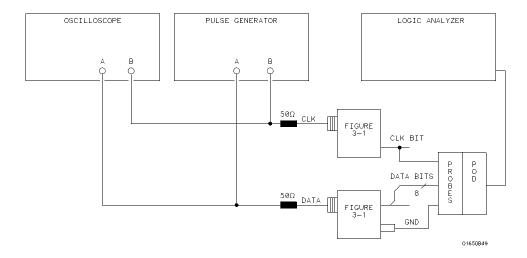

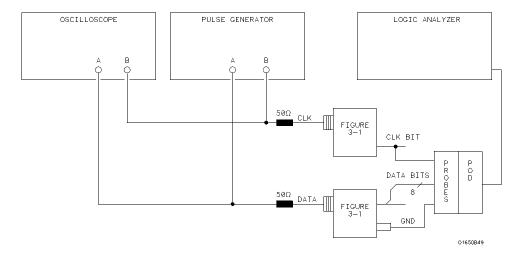

1. Connect the HP 1650B\51B and test equipment as in figure 3-2.

Figure 3-2. Setup for Data Test 1

In this setup, only eight channels are tested at a time to minimize loading. Ground lead must be connected to ensure accurate test results.

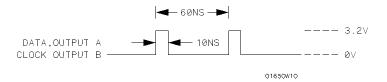

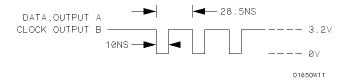

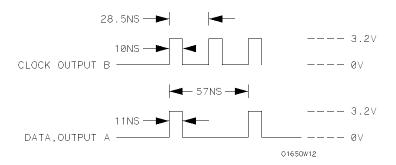

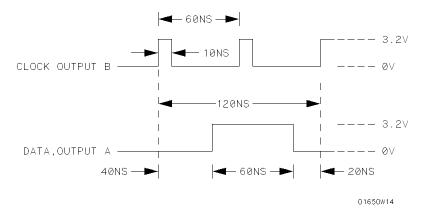

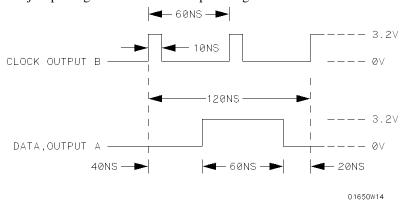

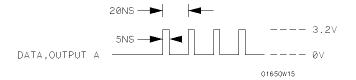

2. Adjust pulse generator for the output in figure 3-3.

Figure 3-3. Waveform for Data Test 1

#### Setting for HP 8161A:

| Parameter                                                                                                   | Output A                                               | Output B                               |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|

| Input Mode Period (PER) Width (WID) Leading Edge (LEE) Trailing Edge (TRE) High Level (HIL) Low Level (LOL) | Norm<br>60 ns<br>10 ns<br>1 ns<br>1 ns<br>3.2 V<br>0 V | 10 ns<br>1 ns<br>1 ns<br>1 ns<br>3.2 V |

| Delay (DEL)<br>Output Mode                                                                                  | 0 ns<br>ENABLE                                         | 0 ns<br>ENABLE                         |

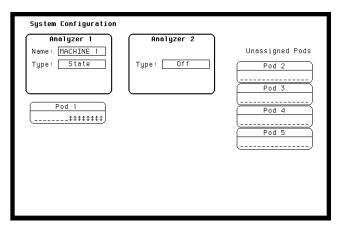

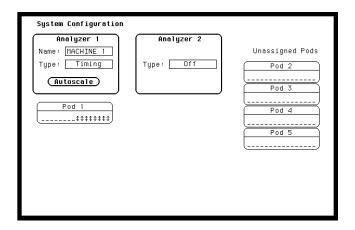

3. Assign the pod under test to **Analyzer 1** in the **System Configuration** as in 3-4. Refer to steps a through c if unfamiliar with menu.

Figure 3-4. System Configuration for Data Test 1

- a. Move cursor to **Type** field of **Analyzer 1** and **SELECT**.

- b. Set the analyzer **Type** to **State** using cursor and SELECT.

- c. Move cursor to Pod to be tested and assign to Machine 1.

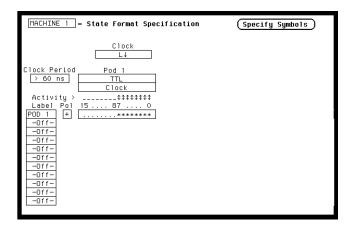

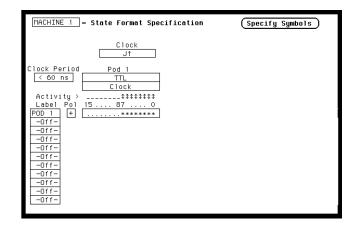

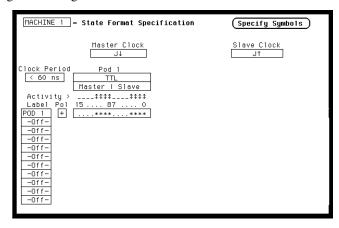

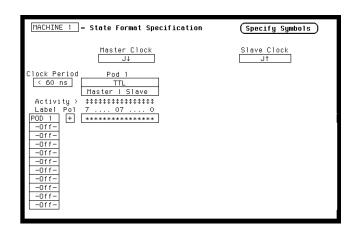

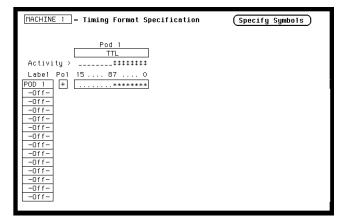

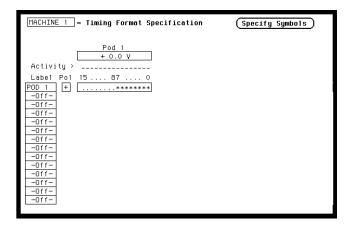

4. In the **State Format Specification** assign **Clock Period** > **60** ns. Also assign lower 8 channels of the pod under test to a label as shown in next figure. If testing HP 1650B then assign falling edge of L clock for all pods. If testing HP 1651B then assign falling edge of J clock for all pods. Refer to steps a through c if unfamiliar with the menus.

Figure 3-5. State Format Specification for Data Test 1

- a. Press front-panel FORMAT key.

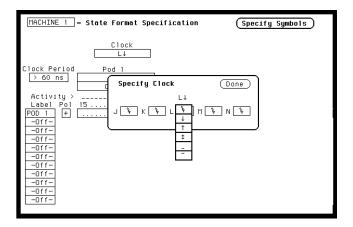

- b. Move cursor to **Clock** field of menu. Use cursor and SELECT key to set appropriate clock for falling edge as in next figure.

Figure 3-6. Clock Assignment for Data Test 1

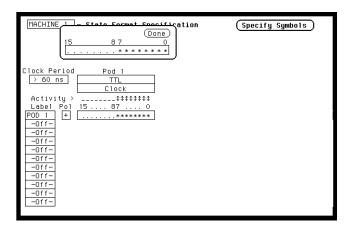

c. Move cursor to the bit assignment field and turn on appropriate eight bits to be tested (\* = on; . = off) as in figure below.

Figure 3-7. Bit Assignment for Data Test 1

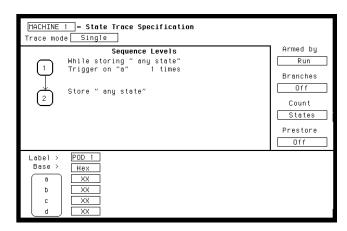

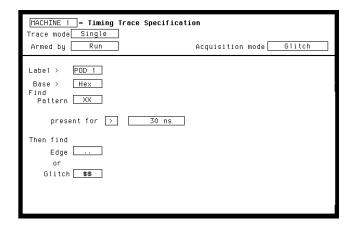

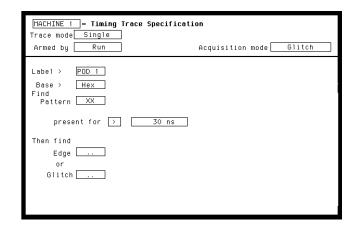

5. Set up the **State Trace Specification** without sequencing levels and set **Count States** as in next figure.

Figure 3-8. Trace Specification for Data Test 1

- a. Press front-panel TRACE key.

- b. Move cursor to **Count**, press SELECT, then move cursor to **States**, press SELECT, and set to **any state** by pressing SELECT again.

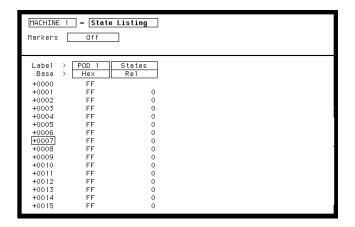

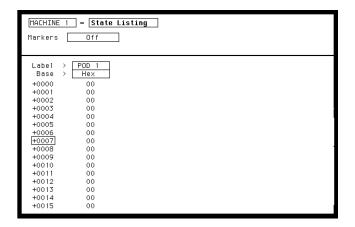

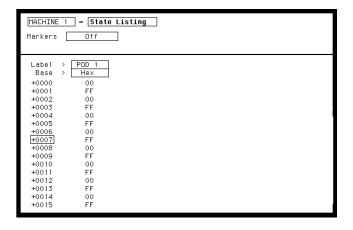

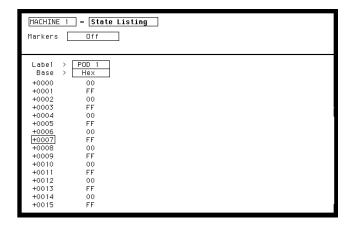

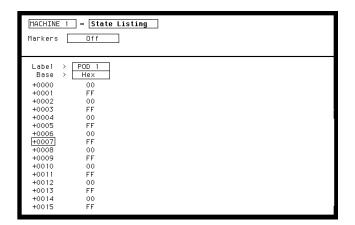

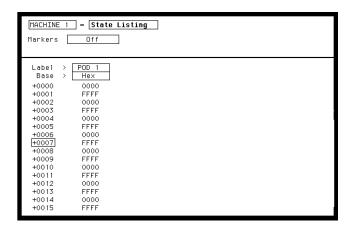

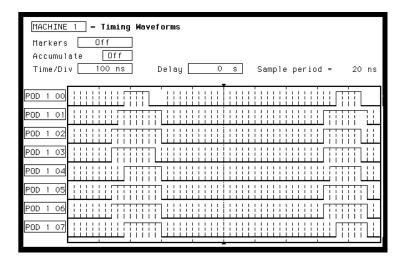

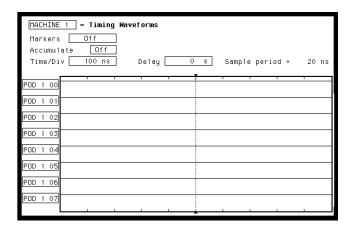

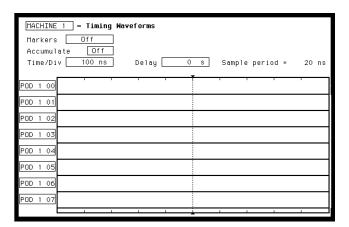

6. Press RUN. The **State Listing** is displayed and shows Fs for the channels under test, when test is passed, as in figure 3-9.

Figure 3-9. State Listing for Data Test 1

To ensure consistent pattern of Fs in listing, use front-panel ROLL field and knob to scroll through **State Listing**.

- 7. If testing the HP 1651B, connect the K clock of Pod 2 to the test connector and repeat steps 4 and 6 for the falling edge of K clock.

- 8. Remove the probe tip assembly from the logic analyzer probe cable and attach to the next logic analyzer probe cable to be tested. Take care not to dislodge grabbers from the test connector. If testing the HP 1651B then re-assign the falling edge of J clock.

- 9. Repeat steps 3, 4, 6 and 7 until all pods have been tested.

- 10. Disconnect lower eight bits (bits 0 through 7) from test connector. Attach upper eight bits (bits 8 through 15) to the test connector.

- 11. Repeat steps 3, 4, 6, 7 and 8 until the upper bits of all pods have been tested.

## Clock, Qualifier, and Data Inputs Test 2

**Description**: This test verifies the setup and hold time specification for the rising edge transition of all clocks on the HP 1650B/51B.

#### **Specification**:

Setup time: Data must be present prior to clock transition;  $\geq 10$  ns.

Hold time: Data must be present after rising clock transition; 0 ns.

#### **Equipment:**

| Pulse Generator |       | HP   | 8161A/020  |

|-----------------|-------|------|------------|

| Oscilloscope    |       |      | HP 54502A  |

|                 | (2)   |      |            |

| Test Connectors | (2)so | ee - | figure 3-1 |

#### Procedure:

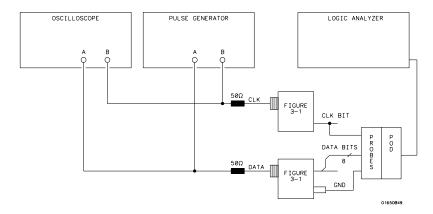

1. Connect the HP 1650B\ 51B and test equipment as in figure 3-10.

Figure 3-10. Test Setup for Data Test 2

In this setup, only eight channels are tested at a time to minimize loading. Ground lead must be connected to ensure accurate test results.

2. Adjust pulse generator for the output in figure 3-11. Pulse generator settings

Figure 3-11. Waveform for Data Test 2

are different for HP 1650B and HP 1651B.

#### Setting for HP 8161A:

| Parameter                  | Output  | A Output B |

|----------------------------|---------|------------|

| Input Mode<br>Period (PER) | Norm    |            |

| HP 1650B                   | 28.5 ns |            |

| HP 1651B<br>Width (WID)    | 40 ns   |            |

| HP 1650B                   | 18.5 ns | 18.5ns     |

| HP 1651B                   | 30 ns   | 30 ns      |

| Leading Edge (LEE)         | 1 ns    | 1 ns       |

| Trailing Edge (TRE)        | 1 ns    | 1 ns       |

| High Level (HIL)           | 3.2 V   | 3.2 V      |

| Low Level (LOL)            | 0 V     | 0 V        |

| Delay (DEL)                | 0 ns    | 0 ns       |

| Output Mode                | ENABLE  | ENABLE     |

- 3. Assign the pod under test to **Analyzer 1** in **System Configuration** as in previous test figure 3-4.

- 4. In the **State Format Specification** assign **Clock Period** < **60** ns, and rising edge of J clock. Also, assign lower 8 channels of the pod under test to a label as in figure 3-12.

Figure 3-12. State Format Specification for Data Test 2

5. Set the **State Trace Specification** without sequencing levels and set **Count** to **Off** as in Figure 3-13.

Figure 3-13. State Listing for Data Test 2

6. Press RUN. The **State Listing** is displayed and lists all 0s for the channels under test, if passed test, as in figure 3-14.

Figure 3-14. Setup for Data Test 3

To ensure consistent pattern of 0s in listing, use front-panel ROLL keys and knob to scroll through **State Listing**.

- 7. Connect the next clock to the test connector and repeat steps 4 and 6 for the appropriate clock. Repeat until all clocks have been tested (clocks J, K, L, M and N).

- 8. Remove the probe tip assembly from the logic analyzer probe cable and attach to the next logic analyzer probe cable to be tested. Take care not to dislodge grabbers from the test connector.

- 9. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1 through 5). Start again with the rising edge of J clock and test the pod with all clocks.

- 10. Repeat until the lower bits of all pods have been tested (pods 1 through 5).

- 11. Disconnect lower eight bits (bits 0 through 7) from test connector. Attach upper eight bits (bits 8 through 15) to the test connector. Repeat steps 3, 4, 6, 7, and 8 until the upper bits of all pods have been tested (pods 1 through 5).

Clock, Qualifier, and Data Inputs Test 3 (HP 1650B Only)

$\begin{array}{ll} \textbf{Description:} \ \ This \ performance \ test \ verifies \ the \ hold \ time \ specification \ for \ the \ falling \ clock \ transitions \ of \ the \ J, \ K, \ M \ and \ N \ clock \ on \ the \ HP \ 1650B. \end{array}$

**Specification**: HP 1650B Hold time: Data must be present after falling J, K, M and N clock transition; 1 ns.

**Equipment:**

| Pulse Generator                | ΗP | 8161A/020 |

|--------------------------------|----|-----------|

| Oscilloscope                   |    | HP 54502A |

| 50 ohm Terminators             |    | HP 10100C |

| Test Connectors see figure 3-1 |    | (2)       |

#### **Procedure:**

1. Connect the HP 1650B and test equipment as in figure 3-15.

Figure 3-15. Setup for Data Test 3

In this setup, only eight channels are tested at a time to minimize loading. Ground lead must be connected to ensure accurate test results.

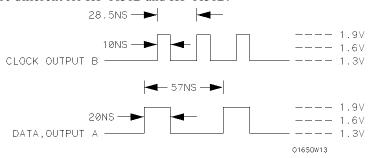

2. Adjust pulse generator for the outputs in figure 3-16.

Figure 3-16. Waveform for Data Test 3

#### Setting for HP 8161A:

| Parameter                                                                                                   | Output A                                               | Output B                           |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------|

| Input Mode Period (PER) Width (WID) Leading Edge (LEE) Trailing Edge (TRE) High Level (HIL) Low Level (LOL) | Norm<br>57 ns<br>11 ns<br>1 ns<br>1 ns<br>3.2 V<br>0 V | Output B 10 ns 1 ns 1 ns 3.2 V 0 V |

| Delay (DEL)                                                                                                 | 0 ns                                                   |                                    |

| Double Pulse (DBL)                                                                                          | 0 115                                                  | 28.5 ns                            |

| Output Mode                                                                                                 | ENABLE                                                 | ENABLE                             |

- 3. Assign the pod under test to **Analyzer 1** in the **System Configuration** as in previous test figure 3-4.