#### Errata

Title & Document Type: 1630A/D Logic Analyzer Operating Manual

Manual Part Number: 01630-90901

Revision Date: February 1983

## **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. The HP XXXX referred to in this document is now the Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

# **About this Manual**

We've added this manual to the Agilent website in an effort to help you support your product. This manual provides the best information we could find. It may be incomplete or contain dated information, and the scan quality may not be ideal. If we find a better copy in the future, we will add it to the Agilent website.

# **Support for Your Product**

Agilent no longer sells or supports this product. You will find any other available product information on the Agilent Test & Measurement website:

# www.tm.agilent.com

Search for the model number of this product, and the resulting product page will guide you to any available information. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available.

# **OPERATING MANUAL**

# LOGIC ANALYZER 1630A/D

© COPYRIGHT HEWLETT-PACKARD COMPANY/LOGIC SYSTEMS DIVISION 1982 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO, U.S.A.

ALL RIGHTS RESERVED

#### **SAFETY SUMMARY**

The following general selety preceditions must be observed during all phases of operation, service, and repair of this instrument. Fellure to comply with these preceditions or with specific warnings elsewhere in this menual violates selety standards of design, manufacture, and intended use of the instrument. Hewlett-Packerd Company assumes no liability for the customer's failure to comply with these requirements

#### GROUND THE INSTRUMENT

To imminize that hazard the instrument chassis and tables must be connected to an electrical ground. The instrument is equipped with a three-confluction acipower rapid. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact in two-contact adapter with the glounding wire injection front, connected to an electrical ground crailet, grounding the power outle. The power just and mating plug of the power rapid must randomly the holeconical Commission (IEC safety, standards).

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the instrument in the presence of flammable gases or times. Operation of any element in such an environment constitutes a do into safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remote instrument covers. Computed in placement and internal additional must be made by qualified in a behavior personnel. Or not replace components with place cache connected. Under cuttain up offices dangered, unitages may exist even with the power cache removed. To scool organise always deconnect power and discharge cuttons before houghing them

### DO NOT SERVICE OR ADJUST ALONE

Do not attempt a turnal service or adjustment, inless another person capable of rendering hist aid and resuscitation is present.

#### USE CAUTION WHEN EXPOSING OR HANDLING THE CRT

Breakage of the daths term, Tritle CRTI causes a high-velocit, scattering of glass fragments implasion to devertige timp psion, award rough handling or jairing of the instrument. Handling of the CRT shall be done only by qualified maintenance purported using approved staffy mask and gloves.

#### DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT.

Because of the cangur of infroducing additional hazards do not install substitute parts or perform an illinauthorized modification of the instrument. Rulum the instrument to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

We many s which as the example below procede potential, dangerous procedures throughout this change for unfined contained in the walnings must be followed.

Dangerous voltages, capable of causing death, are present in this instrument. Use extreme caution when handling, testing, and adjusting.

# **Table of Contents**

| Chapter 1: General Information                  |

|-------------------------------------------------|

| Introduction                                    |

| Manual Contents                                 |

| Analyzer Description                            |

| Physical Configurations                         |

| Analyzer Memory                                 |

| The System Specification                        |

| The Format Specification                        |

| The Trace Specification                         |

| List Drsplays                                   |

| Waveform Displays                               |

| Chart Displays                                  |

| Performance Verification1-5                     |

| Chapter 2: Installation                         |

| Introduction                                    |

| Site Selection                                  |

| Rear-Panel Address Switches                     |

| Rear-Panel Output BNC Connectors                |

| Connecting Analyzer To System Under Test        |

| Connecting Analyzer Through Probe Interface     |

| Connecting Probes Directly To System Under Test |

| Connecting Operating Power                      |

| Chapter 3: Getting Started                      |

| Introduction                                    |

| Setup and Connections                           |

| Making Simple State Measurements                |

| Capturing Activity From The System Under Test   |

| Greating Meaningful Labels                      |

| Triggering A Trace On A Unique Occurrence       |

| Controlling The State Display 3-1:              |

| Simple Timing Measurements 3-15                 |

| Activating The Timing Analyzer                  |

| Controlling The Timing Display                  |

| Selecting Trace Positions On The Display        |

| Triggering On A Timing Event 3-20               |

| Using The Relocation Feature                    |

| Setup For Relocation Use 3-24                   |

| Running A Trace With Relocation Addresses 3-29  |

# Table of Contents (Cont'd)

# Table of Contents (Cont'd)

| Waveform Displays                                   |

|-----------------------------------------------------|

| Analyzer List Displays                              |

| Chapter 7: Performance Analysis Measurements        |

| ntroduction                                         |

| Performance Analysis By Overview Of A State Label   |

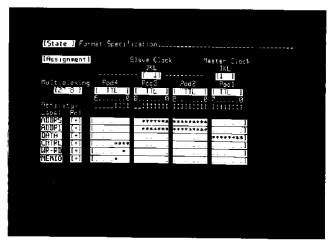

| State Label Overview FORMAT Specification           |

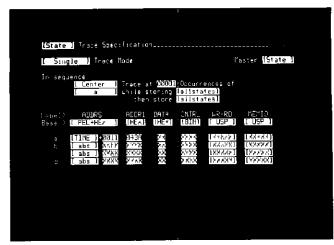

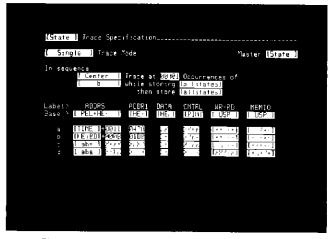

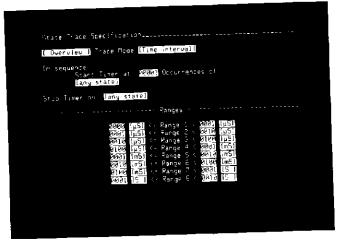

| State Label Overview TRACE Specification            |

| State Label Overview Histogram Chart                |

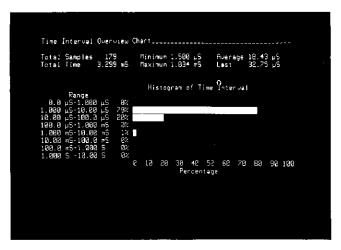

| Performance Analysis By Overview Of A Time Interval |

| Time Interval Overview FORMAT Specification         |

| Time Interval Overview TRACE Specification          |

| Time Interval Overview Histogram Chart              |

| Chapter 8: Timing Measurements                      |

|                                                     |

| Chapter 8A: The Timing FORMAT Specification         |

| introduction                                        |

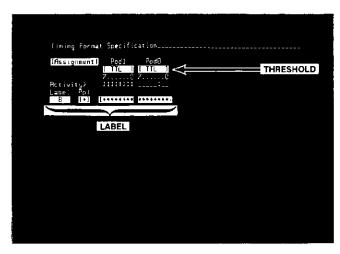

| Timing Format Specification [Assignment]            |

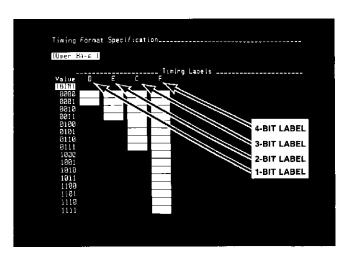

| Timing Format Specification [User Base]             |

| Chapter 8B: The Timing TRACE Specification          |

| Introduction                                        |

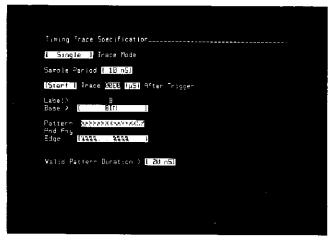

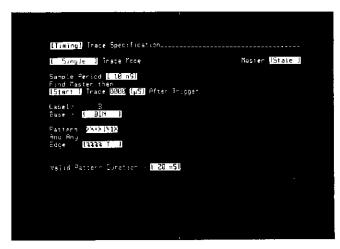

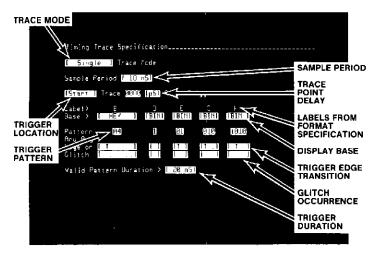

| [Single] Timing Trace Specification                 |

| Continuous] Timing Trace Specification              |

|                                                     |

| Chapter 8C: The Timing Display                      |

| Introduction                                        |

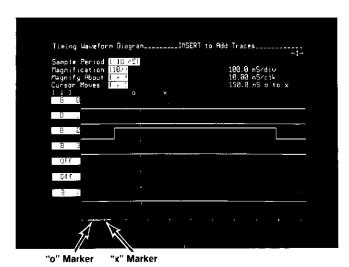

| Waveform Displays 8C-1                              |

| List Displays 8C-3                                  |

| Chart Displays 8C-6                                 |

| Chapter 9: Combined State/Timing Measurements       |

| Introduction                                        |

| The FORMAT Specification                            |

| The TRACE Specification 9-1                         |

| Interactive State/Timing Displays                   |

| interactive State/ Hilling Displays                 |

| Appendix A: Using The Tape Memory Accessory         |

| Introduction A-1                                    |

# Table of Contents (Cont'd)

| How To Create A New File                                               |                                 |  |  |  |

|------------------------------------------------------------------------|---------------------------------|--|--|--|

| Introdu<br>Obtaini                                                     | tix B: Using A Printer ction    |  |  |  |

| Appendix C: Using The HP-IB or HP-IL Interface Introduction            |                                 |  |  |  |

|                                                                        | lix D: Display Messages         |  |  |  |

| Index                                                                  |                                 |  |  |  |

|                                                                        | List of Illustrations           |  |  |  |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7.<br>3-8.<br>3-9<br>3-10. | Front Panel Controls            |  |  |  |

| J 10.                                                                  | Trace List With [Show] Selected |  |  |  |

# List of Illustrations (Cont'd)

| 3-11  | Selecting The Timing Analyzer Configuration                                  |

|-------|------------------------------------------------------------------------------|

| 0.40  | In 1630D       3-15         Default Timing Measurement For 1630D       3-16  |

| 3-12. |                                                                              |

| 3-13. | Magnification Around "x" 3-17                                                |

| 3-14. | Selecting Waveform Positions On Display                                      |

| 3-15. | Triggering On A Pattern And Edge Transition                                  |

| 3-16. | Triggering On A Timing Event                                                 |

| 3-17  | Address Map For Relocation Example 3-23                                      |

| 3-18. | State Analyzer System Configuration 3-24                                     |

| 3-19. | State Assignment Format Specification For 1630D 3-25                         |

| 3-20. | Relocation Menu Assignments                                                  |

| 3-21  | Trace List Using Values From Relocation Menu 3-29                            |

| 3-22  | State Assignment Format Specification With                                   |

|       | Two Labels For The Address Bits                                              |

| 3-23  | Trace List Using Values From Relocation Menu And                             |

|       | Corresponding Absolute Values                                                |

| 3-24  | State Assignment Format Specification With                                   |

|       | Labels Added For WR-RD And MEMIO                                             |

| 3-25  | State User Base Menu Setup                                                   |

| 3-26  | Trace List Using Values From Relocation And                                  |

|       | User Base Menus Together 3-34                                                |

| 3-27  | Combined State/Timing Analyzer System                                        |

|       | Configuration                                                                |

| 3-28. | State Assignment Format Specification                                        |

| 3-29  | State Trace Specification In State/Timing                                    |

| J 25. | Measurements                                                                 |

| 3-30  | State Trace Specification With Trigger                                       |

| 5 00  | In Row "b"                                                                   |

| 3-31. | Timing Trace Specification For Combined                                      |

| J-J1. | State/Timing Measurements                                                    |

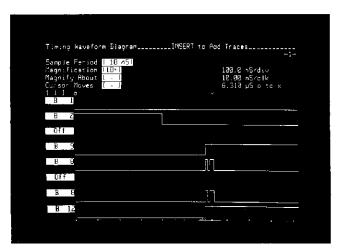

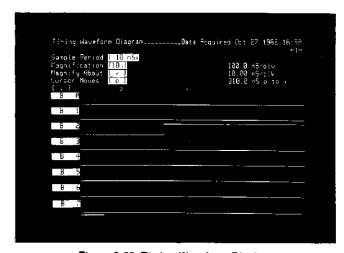

| 3-32  | Timing Waveform Display                                                      |

| 3-32  | Timing Trace Specification With Master [Timing] 3-40                         |

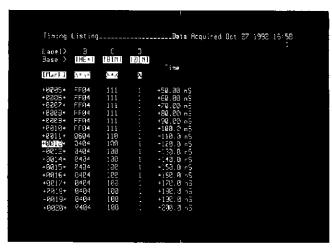

|       | Timing Trace Specification with Master [Timing] 3-40  Timing Listing Display |

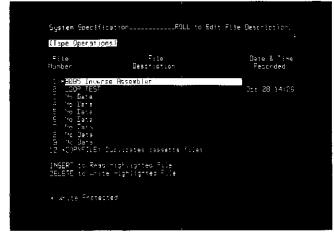

| 3-34. | Tape Operations Menu                                                         |

| 3-35. | Tape Operations Menu                                                         |

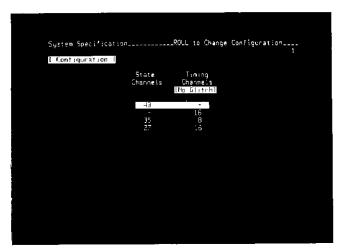

| 5-1   | Configuration System Specification 5-2                                       |

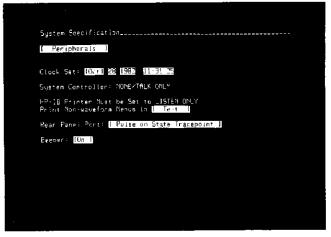

| 5-2   | Peripherals System Specification                                             |

|       | , , ,                                                                        |

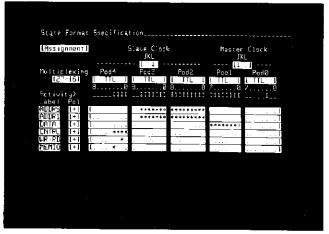

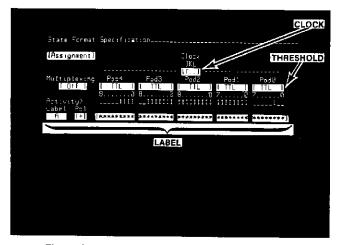

| 6A-1  | State Assignment Format Specification 6A-1                                   |

| 6A-2. | State Relocation Format Specification 6A-3                                   |

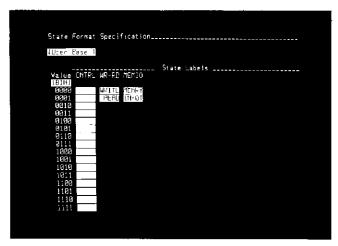

| 6A-3  | State User Base Format Specification                                         |

# List of Illustrations (Cont'd)

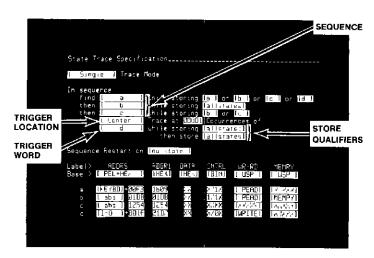

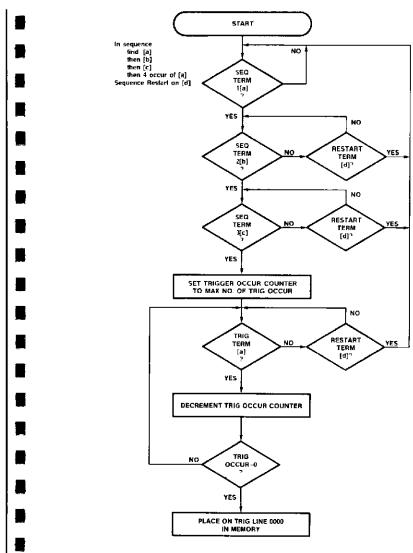

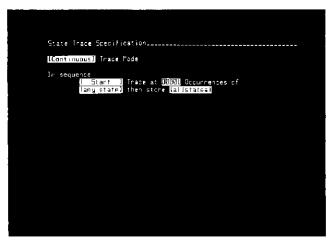

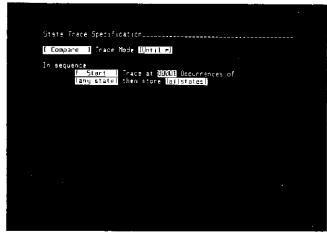

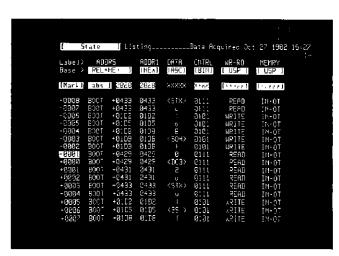

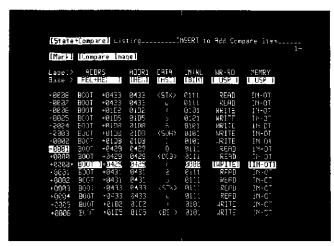

|                | 6B-1.<br>6B-2.<br>6B-3.<br>6B-4.<br>6B-5. | State Single Trace Specification68-2Sequence/Trigger Flow Chart68-3Storage Example68-4State Continuous Trace Specification68-5State Compare Trace Specification68-6                                                                   |

|----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

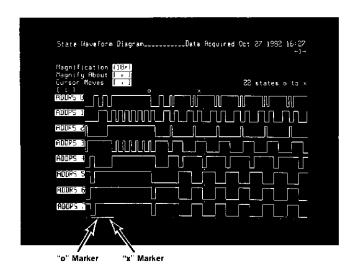

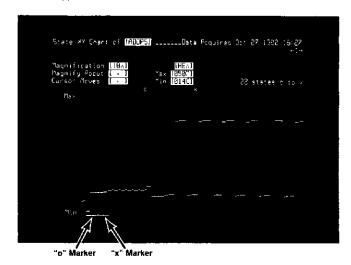

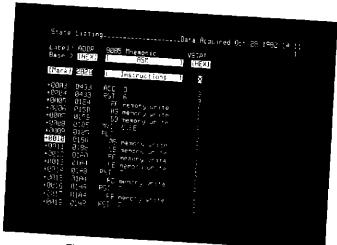

|                | 6C-1<br>6C-2<br>6C-3<br>6C-4<br>6C-5      | Typical List Display In Single Trace Mode 6C-2 Typical List Display In Compare Trace Mode 6C-4 Typical State Waveform Display 6C-5 Typical State XY Chart Of A Label 6C-6 Example Display Showing HP Inverse-Assembled Data List 6C-9 |

|                | 7-1<br>7-2<br>7-3<br>7-4.                 | State Label Overview Trace Specification7-3State Label Overview Histogram Chart7-4State Time-Interval Overview Trace Specification7-6Time Interval Histogram Chart7-7                                                                 |

|                | 8A-1<br>8A-2                              | Timing Assignment Format Specification 8A-2 Timing User Base Format Specification                                                                                                                                                     |

|                | 8B-1                                      | Timing Trace Specification 8B-2                                                                                                                                                                                                       |

|                | 8C-1<br>8C-2<br>8C-3                      | Typical Timing Waveform Display                                                                                                                                                                                                       |

|                | <b>A-</b> 1                               | Tape Operations System Menu                                                                                                                                                                                                           |

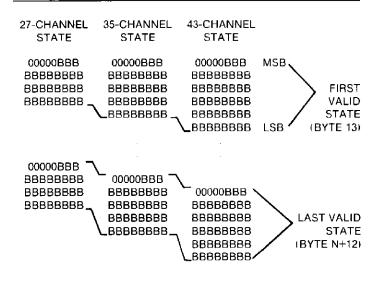

|                | C-1                                       | Data Format For State Acquisition Learn String Sent On HP-IB                                                                                                                                                                          |

| List of Tables |                                           |                                                                                                                                                                                                                                       |

|                | 1-1.<br>1-2.                              | Specifications                                                                                                                                                                                                                        |

|                | C-1                                       | HP-IB/HP-IL Keyboard Mnemonics                                                                                                                                                                                                        |

# Chapter 1 General Information

#### Introduction

This manual describes how to operate the Hewlett-Packard Model 1630A and 1630D Logic Analyzer. This chapter describes the physical and electrical characteristics of the analyzer. At the end of this chapter are two tables: one lists the analyzer specifications guaranteed by HP, and the other lists the analyzer operating characteristics. The last paragraph in this chapter describes how to initiate the analyzer performance verification.

## **Manual Contents**

This manual contains instructions and information to help you install and operate the analyzer. It shows how to assign labels in the format specification to identify signals from the input probes, and shows how to assign symbols to represent values found on those labeled inputs.

Chapter 3 of this manual is called Getting Started. As soon as you can, you should perform the procedures in chapter 3. These will help you become familiar with the analyzer

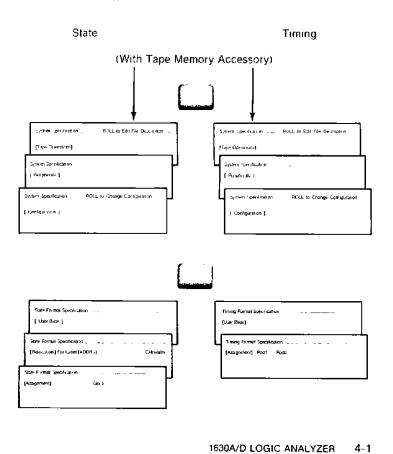

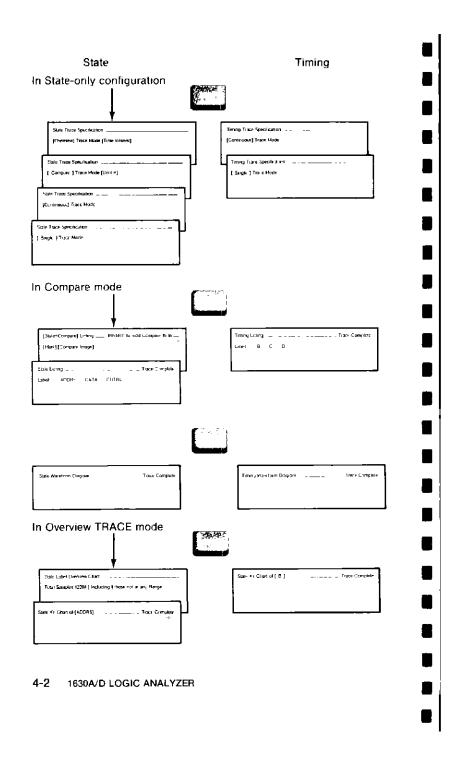

Chapter 4 is a map of the menus in the analyzer. It will help you understand the organization of the analyzer.

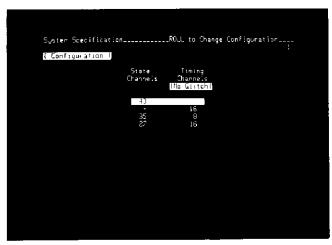

Chapter 5 discusses the System menus which you will use to set up the basic analyzer configuration for the type of measurements you will make

Chapters 6 through 9 describe how to use the analyzer to perform state measurements, timing measurements, performance analysis measurements, and combined state/timing measurements, respectively. Each of these chapters discusses how to set up the menus and read the displays for the corresponding measurements

Appendices in this manual show how to use the accessory digital cassette drive for a tape memory, how to obtain hard copy on an accessory printer, and how to control the analyzer through the HP-IB and/or HP-IL interfaces. The last appendix lists all of the error and status messages displayed by the analyzer.

1630A/D LOGIC ANALYZER 1-1

## **Analyzer Description**

The analyzer performs trace measurements. It can trace the flow of synchronous states in a microprogrammed state machine. It can also trace electrical activity at several points during a period of system operating time. The analyzer can perform both state and timing measurements together, and interactively control the capture of information in each of these two functions.

The analyzer can perform overview measurements which allow you to analyze the performance of code modules in software-intensive systems. The analyzer can perform all of its measurements as a stand-alone instrument, or as part of a system controlled through a standard HP-IB or HP-IL interface bus.

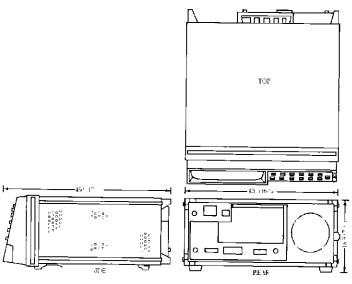

#### **Physical Configurations**

The following is a list of the analyzer configurations, components, and optional accessories:

- HP Model Number 1630A Logic Analyzer. Offers 35 channels for state, timing, and combined state/timing measurements.

- 2 HP Model Number 1630D Logic Analyzer Same as 1630A, except offers 8 additional channels for state and timing measurements.

- 3 HP Part Number 10271A General Purpose State Probe Nine channels for collecting state activity plus an input clock channel. Used to supply state activity only

- 4 HP Part Number 10272A General Purpose State/Timing Probe Eight channels for collecting state activity or timing activity. No input clock channel.

- 5 HP Model Number 82161A Digital Cassette Drive HP Option used to store instrument setups and captured data in tape memory.

- HP Model Number 10269A Probe Interface with HP preprocessor option. HP option used to make all connections to interface the analyzer to a specific microprocessor.

1-2 1630A/D LOGIC ANALYZER

## **Analyzer Memory**

The trace memory of the analyzer is 1024 states deep. It stores each qualified state captured by the input probes. The trace memory also stores measurements of time for the timing listing so you can analyze periods between occurrences of interest.

The compare memory in the analyzer is 16 states deep. It can store up to sixteen lines for comparison with the corresponding lines in the trace memory. You can set the analyzer to save any trace in which the lines of the trace memory are identical to the lines of the compare memory, or where the lines of the trace memory are not identical to the lines of the compare memory. Each state in the compare memory can be edited to specify polarity and set "don't care" comparisons.

#### The System Specification

Use the menus in this specification to identify how the analyzer will be used whether as a state analyzer, a liming analyzer (with or without glitch capture), or a combined state and timing analyzer. In this menu, you also identify the way the analyzer will operate when used as part of a system, or when using capabilities offered by accessories.

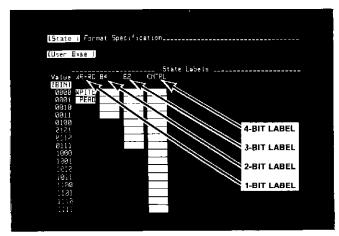

#### The Format Specification

Use the menus in this specification to set up the way the analyzer formulates displays from its captured information. You can label individual bits or sets of bits, and assign names to identify address ranges and/or specific values found in those labeled sets. The analyzer will compose displays using your labels and names, if desired.

### The Trace Specification

Use the menus in this specification to enter parameters for making your measurements. You can set up the analyzer to trace state flow and/or record electrical activity at nodes in a system under test. The analyzer can also perform overview measurements to gauge the efficiency of selected software routines.

#### List Displays

The analyzer composes lists of information captured from labeled sets of bits. These lists show a series of software executions, and/or a sequence of electrical activities at nodes in a system under test. Values shown in these lists can be expressed using names of your choice, as well as using numbers in the binary, octal, decimal, and hexadecimal number bases. Values can also be expressed as ASCII codes for labels having from 6 to 16 bits.

1630A/D LOGIC ANALYZER

1-3

#### Waveform Displays

The waveform display shows up to 16 individual traces of electrical activity on selected bits. Each trace is shown as a continuous line of high and low states. The waveform shows how the states changed with time at each monitored point. You can also see points on the traces where glitches were detected during the measurement, if desired. Glitch detection is accomplished by combining two timing probes to make a single channel, and using one of the probes as a glitch detector.

#### **Chart Displays**

The analyzer can format two types of chart displays XY charts, and histograms. XY charts show a plot of the flow of values on a labeled set of bits. You can control the horizontal and vertical scales of the chart to examine the details around areas of interest on the XY chart.

Histogram charts are bar graphs used to measure the performance of software modules in a system under test. The analyzer can show two types of histograms state label histograms, and time interval histograms. A state label histogram shows the relative number of executions within each range of states you define. Up to eight ranges of states can be defined for a label histogram. Time interval histograms show eight time ranges; you can define the period of each range. You can set up the analyzer to make time interval measurements each time the software executes from one selected point to another in the system under test. The time interval histogram shows how often execution of the selected software module was completed within each of the time ranges you defined.

### **Performance Verification**

The performance verification is a self-test routine contained in the analyzer ROM. It checks for proper functioning of the measurement channels within the analyzer, and provides an indication on the display if the analyzer functions are normal. It also provides troubleshooting information in case an analyzer function is not normal.

To initiate the analyzer self-test, proceed as follows

- 1 In the rear-panel set of address switches, set switch 6 to "1" (switch lever up)

- 2 Turn off the LINE power and then turn it back on During power up, the analyzer will execute the self-test routine. When it has completed the self-test, the display will show "PV Tests Pass". Any other message (or a blank screen) is indicative of a problem.

Possible Messages

PV Tests Pass

Error in RAM

Error in ROM #n Expected XX was YY

Acq error

nn nn nn nn nn nn nn

To return to the normal logic analysis mode after the test, set switch 6 to "0" (switch lever down). It is not necessary to cycle the LINE power switch at this time

If your instrument does not pass the self-test, and you want to return it to Hewlett-Packard for service, fill out one of the tags at the back of this manual and attach it to your instrument. Be sure to note the failure message from the CRT on the tag.

1630A/D LOGIC ANALYZER

1-5

Table 1-1. Specifications

Measurement Configurations

| Measurement Configurations      |                                                                                                                                                 |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ST                              | ATE TIMING                                                                                                                                      |  |

| 1630A 3                         | 35 0                                                                                                                                            |  |

|                                 | 0 8                                                                                                                                             |  |

| 2                               | 27 8                                                                                                                                            |  |

| 1630D: 4                        | 13 0                                                                                                                                            |  |

|                                 | 0 16                                                                                                                                            |  |

| 3                               | 35 8                                                                                                                                            |  |

| Ž                               | 27 16                                                                                                                                           |  |

| Note: Number of tim             | ing channels halved in Glitch mode                                                                                                              |  |

| Measurement Functions<br>Memory |                                                                                                                                                 |  |

| Data Acquisition                | 1024 words                                                                                                                                      |  |

| Compare                         | 16 words.                                                                                                                                       |  |

| Search.                         | Memory may be searched for any pattern<br>defined within a label set. All pattern matches<br>in memory may be marked or separately<br>displayed |  |

| Input Specifications            |                                                                                                                                                 |  |

| Clock repetition rate           |                                                                                                                                                 |  |

| Single Phase                    | 25 MHz with single clock and single edge                                                                                                        |  |

|                                 | specified.                                                                                                                                      |  |

|                                 | 20 MHz with any ORed combination of                                                                                                             |  |

|                                 | clocks and edges                                                                                                                                |  |

| Multiplexed                     | Master Slave clock timing Master clock must follow slave clock by at least 10 ns and                                                            |  |

|                                 | preceed next slave clock by 50 ns or more.                                                                                                      |  |

|                                 |                                                                                                                                                 |  |

| Clock Pulse Width               | ≥10 ns at threshold.                                                                                                                            |  |

| RC                              | 100 kilohms +/-2% shunted by approx 5 pF                                                                                                        |  |

|                                 | at probe body                                                                                                                                   |  |

| Setup time                      | time data must be present prior to clock                                                                                                        |  |

|                                 | transition, ≥20 ns.                                                                                                                             |  |

| Hold time                       | time data must be present after clock transi-                                                                                                   |  |

|                                 | tion, 0 ns                                                                                                                                      |  |

| Minimum swing.                  | 600 mV p-p.                                                                                                                                     |  |

| Minimum input overdrive         |                                                                                                                                                 |  |

|                                 | 250 mV or 30% of input amplitude, which-                                                                                                        |  |

|                                 | ever is greater                                                                                                                                 |  |

|                                 |                                                                                                                                                 |  |

1-6 1630A/D LOGIC ANALYZER

# Table 1-1. Specifications (Cont'd)

Maximum voltage:

+ -40 volts, peak

Threshold Range

-9.9 volts to +9.9 volts in 0.1-volt incre-

ments. Accuracy 2.5% ±/-120 mV

Dynamic Range:

Glitch

+ -10 volts about threshold.

With glitch detection on, number of timing channels are halved. Minimum detectable

glitch 5 nsec width at threshold.

Operating environment

Temperature

0 to 55 degrees C (32 to 131 degrees F), 20 to

30 degrees C recommended.

Humidity:

up to 95% relative humidity at +40 degrees

C, 40% to 80% relative humidity recom-

mended

Altitude<sup>.</sup> Vibration:

to 4600 m (15 000 ft)

n: vibrated in three planes for 15 min each

with 0.3 mm excursions, 5 to 55 Hz.

Dimensions:

1630A/D LOGIC ANALYZER

# Table 1-2. Operating Characteristics

| <u> </u>          | <del></del>                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State Mode        |                                                                                                                                                                                                                                                                  |

| Clocks            | three ORed clocks operate in single-phase or two-phase demultiplexing mode. Clock edge is selectable as positive, negative, or both edges for each clock. Different edge selections may be made on the same clock if used in each phase of the multiplexed mode. |

| Data Indexing     |                                                                                                                                                                                                                                                                  |

| Resources:        | four terms including the Boolean NOT of<br>each term, ALL patterns, or NO pattern. (A<br>term is the AND combination of bit patterns<br>in each label.) Terms may be used as often<br>as desired                                                                 |

| Trigger:          | up to four resource terms may be used in sequence to establish the trace parameter. The last term in the sequence may use up to four resource terms in an ORed format                                                                                            |

| Restart:          | one to four resource terms may be used in<br>an ORed condition for a sequence-restart<br>condition                                                                                                                                                               |

| Store qualifiers: | one to four resource terms may be used in<br>an ORed format. Store qualification may be<br>separately defined for each term in the<br>trigger sequence                                                                                                           |

| Occurrence        | occurrence of the last event in the sequence may be specified up to n = 59999                                                                                                                                                                                    |

| Compare           | trace until compare "equal to" or "not equal to" is provided. The compare file is the width of the analyzer, with a depth up to 16 words. Each word in the compare buffer can have "don't cares" and can be compared anywhere in the 1024 deep memory            |

| Arming:           | the state analyzer can be armed by the full<br>Data Indexing capability of the Timing<br>Analyzer.                                                                                                                                                               |

Table 1-2. Operating Characteristics (Cont'd)

Overview

XY Chart:

a chart of any user-defined label can be shown. The user can change the upper and lower bounds of the chart, and all 1024 states of the memory can be simultaneously displayed

Time measurement: a timer can be started on completion of a sequence of up to three resource terms with restart and occurrence capability like state data indexing. The timer can be stopped and/or restarted on OR'd combinations of one to four resource terms. A histogram of the start/stop time measurement is displayed. The user can specify up to eight time ranges Minimum time, maximum time, average time, last time, total time, and total samples are also displayed.

> Resolution - displayed statistics 250 ns or 0.1% of reading, whichever is greater.

4-digit display.

State histogram

- Histogram ranges 1 microsecond a histogram of any user-defined label can be shown. The user can specify up to eight

labels and ranges. Maximum Count - 263-1.

Resolution - actual count is rounded to 0.1% (4-digit display).

Timing mode

Clock Ranges

10 ns to 500 ms in 1, 2, 5 sequence

+/-0.01%

Accuracy: Data Indexing

Asynchronous pattern:

20 ns to 1 ms in 1, 2, 5 sequence with an accuracy of +/- 20% or 15 ns, whichever is greater

Glitch or edge on any channels AND d with asynchronous pattern Maximum time delay

> approx 218 times the sample period to a maximum of 9999 sec.

> > 1630A/D LOGIC ANALYZER

1-9

## Table 1-2. Operating Characteristics (Cont'd)

| Arming:                 | the timing analyzer may be armed by the full data indexing capability of the state analyzer                                                                                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Markers                 | time between dual markers (x and o) is displayed to accuracy of one sample period.                                                                                                                                                                                                                       |

| Expansion               | X1 to X40 in 1, 2, 4 sequence. Display is a compressed representation of the 1K memory in X1 magnification. In X2 magnification, each displayed sample represents a single sample in memory.                                                                                                             |

| Overview <sup>-</sup>   | a chart of any user-defined label can be shown. The user can change the upper and lower bounds of the chart, and all 1024 states of the memory can be simultaneously displayed.                                                                                                                          |

| General Characteristics |                                                                                                                                                                                                                                                                                                          |

| Labels                  |                                                                                                                                                                                                                                                                                                          |

| Input channel label     | S                                                                                                                                                                                                                                                                                                        |

|                         | up to 8 state, 16 timing, user-defined, 5-<br>character labels may be assigned bit pat-<br>terns in any configuration. Bits may be used<br>in more than one label and need not be<br>contiguous. Primary use is for identifying<br>bits assigned to bus structures such as<br>Address, Data, and Status. |

| User field              | all labels with 4 bits or less allow mnemonics to be assigned to specific patterns. Primary use is to identify such functions as Read, Write, Op Code, etc.                                                                                                                                              |

| Relocatable field       | any single state label may be defined to have relocatable properties to facilitate view-                                                                                                                                                                                                                 |

ing software modules in the format they were written. Up to 16 module starting locations may be specified, allowing trigger parameters to be based on module names. plus an offset value. An onboard calculator that operates in hex, octal, binary, or decimal facilitates general offset calculations

24-hour clock prints out time of data collec-

tion on all stored records.

1-10 1630A/D LOGIC ANALYZER

Time-of-day-clock:

Table 1-2. Operating Characteristics (Cont'd)

**Activity Markers**

provided in format display for quick identification of active inputs.

Outputs HP-IB.

HP-IB connector with 8-position HP-IB switch located on rear panel. Five positions on switch are used to determine address. 2 positions used to determine TALK ONLY mode for hardcopy, or system controller HP-IB can be used in following environments

- Logic analyzer being controlled from a controller, such as HP 9826A Maximum bus transfer rate is approximately 4K bytes per second

- 2 Stand-alone hard copy on a graphics printer, such as HP 2671G

HP-IL

HP-IL connector located on rear panel for HP-IL control, or for interfacing to HP 82161A, low-cost mini-cassette drive. Not required to use analyzer, but enhances analyzer operation as follows:

- Storage of user setups and measurement results, 10 different files can be stored on one cassette

- When coupled with an appropriate preprocessor, allows analyzer to assume a processor-specific personality to present data in mnemonic format.

Rear-panel BNCs

one output BNC labeled PORT, located on rear panel, with a TTL output level, high ≥2V into 50 ohms; low ≤0 4V into 50 ohms. The BNC can be programmed from the keyboard to provide the following signals.

- 1. Pulse on State Trace Point

- 2. High until State Trace Point

- 3. Low until State Trace Point

- 4 High on last Sequence.

- 5 High on Timing Pattern

- 6 Constant High

- 7. Constant Low

1630A/D LOGIC ANALYZER 1-11

## Table 1-2. Operating Characteristics (Cont'd)

one BNC labeled ACCESSORY POWER supplies +5V for preprocessor or logic

probes

1630A: 12.6 kg (28 lb) net, 17 kg (38 lb) Weight

shipping

1630D: 13.2 kg (29 lb) net 17.7 kg (39 lb)

shipping

Power requirement 115/230 Vac, -22% to ±10%; 275W max, 48

to 66 Hz.

Accessories supplied three 10-bit 10271A state probes and one

10272A state and timing probe with 1630A (two 10272A with 1630D), one 2.3 m (7.5 ft)

power cord, one Operating Manual

Service And Calibration Support

The 1630A/D contains all necessary interfaces to allow high-speed troubleshooting and calibration with automatic equipment Guided probe techniques, utilizing signature analysis under computer control, coupled with special test instruments and fixtures allow most failures to be isolated to the component level in a minimum amount of time. After repair, full and complete calibration can be accomplished in minutes, using the same equipment. Since this integrated design can only be serviced efficiently and economically with this automated system, all major HP service facilities have installed this special equipment. This HP investment will provide you with the fastest, most complete and lowest cost repairs and calibrations For those companies where economies of scale make in-house repair and calibration cost-effective, an option is available that provides the special hardware, software and related documentation and training to allow 1630A/D repair. Additional test equipment is required. Contact your local HP sales representative for further information.

1-12 1630A D LOGIC ANALYZER

# Chapter 2

### Introduction

The purpose of this section is to show you how to set up the analyzer and connect the probe cables to make measurements in a system under test

## Site Selection

Place the logic analyzer on a clean workspace which has adequate ventiliation

# **Rear-Panel Address Switches**

The address switches are a set of eight switches on the mainframe rear panel. These configure the analyzer to operate on the HP-IB and/or HP-IL interface buses, and to execute the performance verification self-test. Refer to the label located below the address switches to set the switches for desired operation.

- a If you are operating the analyzer as part of a system, set switches one through five to select the system address for your analyzer Set switches seven and eight to select the desired system controller.

- b If you are operating the analyzer in a stand-alone configuration, with or without an external printer, set switches seven and eight to select the TALK ONLY mode (both switches to "0").

- Set switch six to "0" Switch six is only set to "1" during the performance verification self-test

# NOTE

A switch is set to "1" when its toggle lever is up, and set to "0" when its toggle lever is down

1630A/D LOGIC ANALYZER

2-1

# **Rear-Panel Output BNC Connectors**

The rear-panel BNC labeled ACCESSORY POWER provides 5 volts for operating an external HP preprocessor or logic probes.

The rear-panel BNC labeled PORT provides a TTL control signal whose characteristics are selectable in the SYSTEM [Peripherals] menu for control of external measurement instruments and equipment

# Connecting Analyzer To System Under Test

The analyzer can gather information through either the Model 10269A Probe Interface or through direct connections from the general purpose probes. The procedures to be followed when making connections differ. Refer to the procedure that describes how to make connections using your interface

#### Connecting Analyzer Through Probe Interface

- Connect the probe pods from the analyzer to the appropriate pod sockets on the probe interface. Refer to the manual for the general purpose preprocessor.

- Connect the ribbon cable from the probe interface (with preprocessor interface module installed) to the microprocessor in the target system.

- 3 Connect a BNC cable from the ACCESSORY POWER BNC on the analyzer rear panel to the ACCESSORY POWER (+5v) BNC connector on the probe interface

#### Connecting Probes Directly To System Under Test

- 1. Snap on the adapters for each of the general purpose probe pods.

- 2 Connect the line for each probe bit to monitor a node in the system under test. Leave extra lines unconnected. Do not connect signals with different threshold levels (some TTL and some ECL, for example) in the same probe pod.

- 3 Connect the ground probe from each pod to a ground point in the system under test

2-2 1630A/D LOGIC ANALYZER

# **Connecting Operating Power**

Before connecting operating power, set the associated power selector switch to identify the kind of power in use either 115V or 230V. Then connect the line power cord from the analyzer to a source of operating power.

1630A/D LOGIC ANALYZER 2-3/(2-4 blank)

# Chapter 3 Getting Started

#### Introduction

The purpose of this chapter is to help you become familiar with the Model 1630A/D. Logic Analyzer. This chapter shows you how to use the analyzer by leading you through a series of steps in which you gather information about the software in your system. First, you will use the analyzer to make state measurements. Next, you will make timing measurements. Then you will make a series of measurements using some of the special features of the analyzer. Finally, you will make coordinated state and timing measurements together.

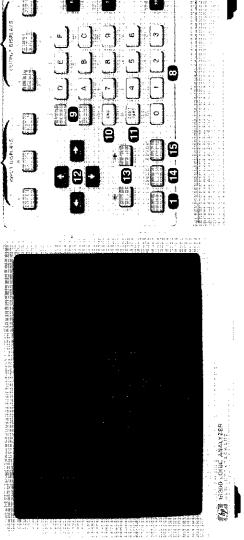

The keyboard of the 1630A/D Logic Analyzer is simple to use, after a short familiarization, but it is not a key-per-function keyboard. Functions are layered on the keys via the instrument menus. The functions of each of the keyboard keys is discussed in figure 3-1.

## **Setup And Connections**

The demonstration procedures in this chapter can be performed using any 8-bit or 16-bit microprocessor system as a source. If you are going to make measurements on a system which has an Intel 8085, these connections will apply directly to you. If you are going to use a system which has any other microprocessor, this procedure will describe the modifications you need to make to obtain proper operation.

- 1 Set the rear-panel power-selector switch to identify the operating power in use (either 115V or 230V)

- 2 Connect the power cord to a source of operating power.

- 3 Refer to chapter 2 of this manual and follow all of the procedures, as applicable

- 4. If you are using a preprocessor interface with a personality module to connect to the microprocessor in your system, the interface will make all of the clock and probe channel connections. You can skip the remainder of this procedure and begin with Making Simple State Measurements.

1630A/D LOGIC ANALYZER 3-1

- blue key. This key activates the blue SHIFT function assigned to function for the next keystroke. The SHIFT function will continue each keyboard key. A momentary press activates the SHIFT as long as you keep the blue key pressed.

- set up secondary configurations and outputs for peripherals, and active). FORMAT has three menus that determine how data is collected and interpreted on the display. TRACE has a series of menus that specify the measurement mode and parameters for INPUT DISPLAYS: Three keys that select sets of 1630A/D menus. SYSTEM calls up menus that define the instrument configuration, control tape operations (when the 82161A drive is connected and collecting data. N

- OUTPUT DISPLAYS, three keys that select a state display (LIST), timing display (WFORM), or performance overview chart (CHART). 0

- 4 LINE, Turns on operating power.

- 6

- complete measurement that was halted by pressing the STOP 5 RUN initiates a new measurement: RESUME continues an in-

- STOP. Terminates a measurement; RETURN TO LOCAL overrides an HP-IB or HP-IL controller to return control of the analyzer to the keyboard. 9

- PRINT commands the current display content to be printed on an HP-IB graphics printer; PRINT ALL prints the entire content of the displayed menu or list, including all on-screen and off-screen information

- Hex keyboard for data entry. ω

- 9 NEXT [] and PREV [] keys cycle through all the menu selections available for fields enclosed in brackets. []

Figure 3-1. Front Panel Controls

- CHS. Used to change +/- signs when specifying memory locations in either direction from the trigger event, and when specifying polarities. This key will also print a dash when used in a text field

- DON'T CARE enters an "X" in lieu of a number, to indicate "any value will serve"

- CURSOR. These keys move the cursor from field to field in the menus. The blue SHIFT function allows these keys to rearrange the order of labels in the menus, and to move the cursor from pod to pod in the label lines of the FORMAT [Assignment] menu. The CURSOR keys can also move the configuration bar in the SYSTEM [Configuration] menu, and the "x" and "o" markers on the waveform and chart displays.

- ROLL keys move timing displays left or right, state lists up or down, and the configuration bar in the SYSTEM [Configuration] menu

- 113 INSERT/DELETE are used to add or delete fields and labels

- **15** CLEAR ENTRY This is the field eraser key, DEFAULT returns all fields in the displayed menu to their power-up conditions

Figure 3-1. Front Panel Controls (Cont'd)

1630A/D LOGIC ANALYZER

3-3

- 5 If you are using the general purpose adapters to connect analyzer probe channels to pins of the microprocessor in your system, make the connections as follows:

- a Connect the channels of pod 2 to the lower nine bits of the address bus (channel 0 to the LSB, channel 1 to the next bit, etc.)

- Connect the channels of pod 3 to the next higher seven bits of the address bus. (Leave channels 7 and 8 open on pod 3)

- c. Connect the channels of pod 1 to the least significant eight bits of the data bus (channel 0 to the LSB, channel 1 to the next higher bit, etc).

- d Connect the channels of pod 4 to the control lines in your system under test to obtain status information

- Connect the clock line of pod 2 (the L clock) to the address clock. Connect the clock line of pod 4 (the J clock) to the data clock.

#### NOTE

If you are making connections to a system that uses a single clock, connect it to the L clock line of pod 2.

Leave all remaining channels of the probe pods unconnected. This completes the connections required to use the analyzer in the procedures described in this chapter.

# **Making Simple State Measurements**

The following procedure will show you how to capture state flow using the analyzer. It will show you how to arrange the state activity into labeled fields, how to trigger a trace during particular occurrences in state flow; and how to get a desired portion of the captured information on the display.

## Capturing Activity From The System Under Test

Turn on operating power in the system you are going to use as a signal source for making these tests.

3-4 1630A/D LOGIC ANALYZER

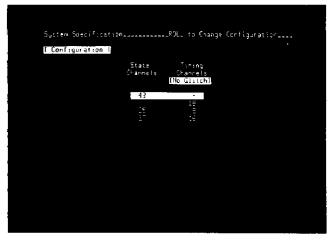

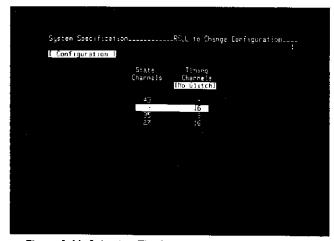

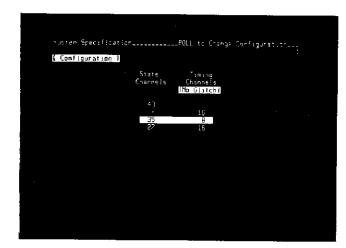

- Turn on the LINE pushbutton power switch on the front panel of the analyzer. The analyzer will execute its boot-up routines and configure itself to make a simple state measurement (all channels will be dedicated to making state measurements, and none to making timing measurements). This configuration is shown by the position of the bright bar on the system specification (figure 3-2).

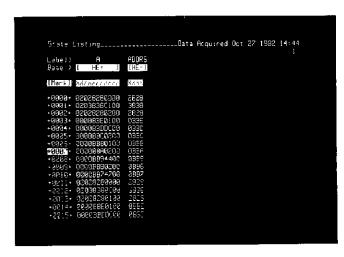

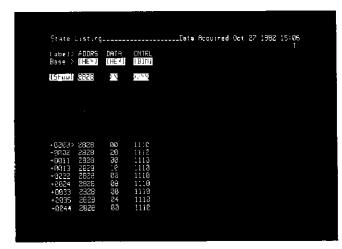

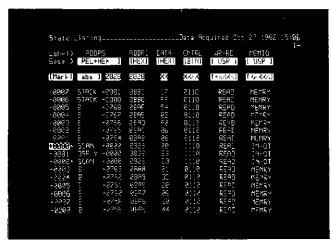

- 3. Press the RUN key on the front panel. The analyzer will execute a single trace, capture data, and present a list on screen. The list will be one column of information. The column will include all of the activity captured from all of the analyzer channels. An unconnected probe bit will show up as 0 on the trace list. The list may not make much sense right now, but its presence ensures that the analyzer is connected to the system under test, and it can gather data. See figure 3-3.

Figure 3-2. Default System Configuration For 1630D (1630A has 8 less channels)

1630A/D LOGIC ANALYZER

3-5

Figure 3-3. Default Trace List

## Creating Meaningful Labels

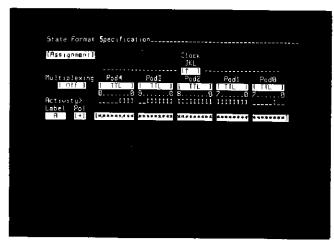

- 1 Press the FORMAT key. This selects the Format Specification menu. In this menu, you select the arrangement for presenting captured data so that the information will be easy to read and interpret. See figure 3-4

- 2 The cursor selects the field of the menu to be edited by the keyboard keys. Use the CURSOR keys to move the cursor from field to field on the State Format Specification menu. Notice that the cursor will advance left-to-right and right-to-left if you hold down the corresponding CURSOR arrow key, and it will stop at the end of the row. By a series of presses of the same CURSOR arrow key, the cursor will travel across each row and it will advance from row to row on the menu.

- 3 Notice that the format specification was automatically loaded with label "A", and that label A includes all of the bits of information from all of the probe lines in the analyzer. (Each asterisk indicates the corresponding probe line is included in the label.)

3-6 1630A/D LOGIC ANALYZER

Figure 3-4. Default Format Specification

- 4. Press the CURSOR-down-arrow key three times. This places the cursor in the name assignment field of label A.

- 5. Notice the message at the top of the screen. This tells you that the analyzer is ready to create new labels, if desired

- Press the INSERT key. This creates a new label field in the format specification. It has no name, and no bits are assigned to it

- From the keyboard, type in ADDRS under label in the new field (Press the blue SHIFT key to obtain keyboard blue functions, press and hold the blue shift key to type a series of SHIFT functions.)

- 8. Press and hold the CURSOR-right-arrow key to move the cursor down the label line until it is in bit 6 of pod 3.

- 9 Press the NEXT[] key sixteen times or hold it down. The asterisks that appear in the entries under Pod3 and Pod2 assign the corresponding probe bits to the label named ADDRS.

1630A/D LOGIC ANALYZER 3-7

Figure 3-5. Labeling Address Bits In Trace List

- 10. Press the LIST key. See figure 3-5. The information collected from the sixteen channels of pod 3 and pod 2 (connected to the address bus in your system) is shown under a separate label called ADDRS. Is this the address space you expected to see executed by the system under test? If not, check your probe connections and check the clock polarity in the format specification.

- Press the FORMAT key. Now you can create new labels for the information collected from the data bus and the control bus.

- 12. Press the INSERT key. This opens a blank field for a new label on screen.

- 13 Type in DATA from the keyboard, and then press the CURSOR-right-arrow key and hold it until the cursor steps down the label field to bit 7 of pod 1

3-8 1630A/D LOGIC ANALYZER

- 14. Press the NEXT[] key eight times. This gathers all of the information obtained by the eight probe channels of pod 1 under the label called DATA. These are the channels you connected to the data bus in your system under test.

- 15 Press the INSERT key again.

- 16 Type in CNTRL, and use the CURSOR keys to move the cursor into the probe field under pod 4 where you connected the probe channels to control lines in your system under test.

- 17 Press the NEXT[] key, as required, to assign (with asterisks) the bits of pod 4 that are connected to control lines in the system under test

#### NOTE

The bits included in a label do not need to be physically adjacent. Channel 2 in pod 1 can be combined with channel 5 in pod 3 to make a single label consisting of two probe bits.

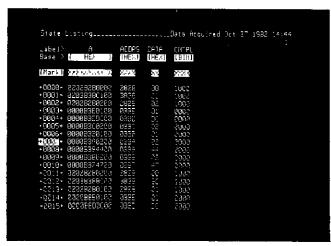

- 18 Press the LIST key. Now your list display will show the original label A, along with separate columns of information collected from the address lines, the data lines, and the control lines. (See figure 3-6.)

- 19 Use the CURSOR-right-arrow key to move the cursor to the [HEX] field under the CNTRL label

- 20 Press the NEXT[] key two times to select binary as the numerical base for display of control information. Now you can see the conditions of each of the control lines as the measurement was made

- 21 Press the FORMAT key.

- 22 With the CURSOR-up-arrow key, move the cursor up into the row of label A.

- 23 Press the blue SHIFT key and DELETE key to remove label A from your analyzer.

1630A/D LOGIC ANALYZER 3-9

Figure 3-6. Labeling Address, Data, and Control Bits In Trace List

24 Press the LIST key. See that only your own labels are present on the list display.

# Triggering A Trace On A Unique Occurrence

- Select one of the addresses from the ADDRS column on the list display, and write it down.

- Press the TRACE key. This brings the trace specification to the display. In this specification, you can set up the conditions that will define the trigger point and the kind of activity to be captured in the trace memory.

- Press the CURSOR-down-arrow key to place the cursor in the [any state] field. This is where trigger selections can be specified.

- Press the NEXT[] key two times. This selects trace triggering to occur when the analyzer finds the state defined in row "a" on the display.

3-10 1630A/D LOGIC ANALYZER

Figure 3-7. Specifying A Trigger State

- Press the CURSOR-down-arrow key to place the cursor in row "a"

- 6. Using keyboard keys, type in the address you wrote down in step 1 above. This sets up the state measurement function to trigger when it finds your selected state on the address lines. The X's under DATA and CNTRL indicate that any states on those lines will satisfy the row "a" specification. See figure 3-7.

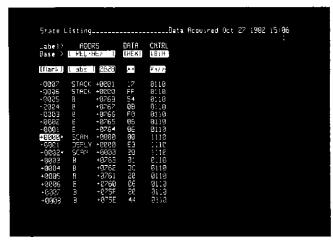

- 7. Press the RUN key. The analyzer will monitor activity from the system under test until it finds the state you specified on the address lines. Then it will capture that state into memory and store each state that it finds after that until its memory is filled one time. Then it will stop storing states and place the message "Trace Complete" at the top of the screen. See figure 3-8.

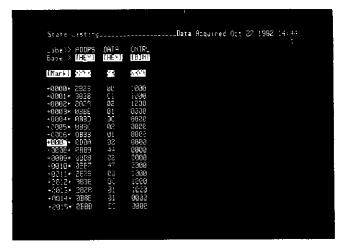

1630A/D LOGIC ANALYZER 3-

Figure 3-8. Trace List With Trigger At Start

- 8. Note that the state you specified as trigger is the first state on your display (line number 0000). Trigger was specified to be the start of the trace.

- 9 Press the TRACE key

- Press the CURSOR-up-arrow key to place the cursor in the [Start] trigger position field.

- Press the NEXT[] key to select center of memory for your trigger position

- 12. Press the RUN key. The analyzer will begin storing states into memory. When it finds the state you specified as trigger, it will capture that state and then store an additional number of states equal to one-half of the memory. The states that were captured before trigger will be identified on the list with line numbers preceded by minus signs. The states captured after the trigger state will be identified by line numbers preceded by plus signs. See figure 3-9.

3-12 1630A/D LOGIC ANALYZER

Figure 3-9. Trace List With Trigger At Center

#### NOTE

If the trigger state is found before the first half of memory is completely filled with states, the portion of unfilled memory will not be available for display in the list.

#### Controlling The State Display

- Press the CURSOR-down-arrow key to place the cursor in the ADDRS field beside the [MARK] indicator.

- Type in the state you selected for a trigger state. The analyzer will

place an asterisk on screen to mark each line that has your

selected state. You can use the ROLL-up-arrow and ROLL-downarrow keys to scroll through memory and see the states with

asterisks beside them.

- Press the CURSOR-left-arrow key to bring the cursor into the [MARK] field

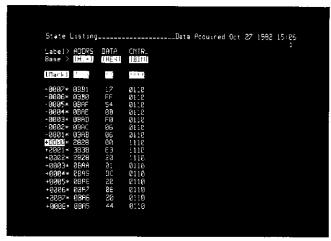

Figure 3-10. Trace List With [Show] Selected

- Now press the NEXT[] key. The field will change to [SHOW], and the display will show only those lines from memory that have the address state you selected. See figure 3-10.

- If the display shows many lines, alternately press the ROLL-uparrow and ROLL-down-arrow keys. The display will scroll through memory and show you all of the memory locations that meet the specification of the [SHOW] line above.

- 6 Notice the ">" symbol beside one of the line numbers on screen. This identifies which line in memory will be shown on screen. If you select a [MARK] display (which includes all lines of memory).

- 7 Press the NEXT[] key to select a [Mark] display. The line that had the ">" symbol beside it is centered on screen. Its line number is shown in inverse video.

- 8 Press the CURSOR-down-arrow key to move the cursor into the inverse-video line number field

3-14 1630A/D LOGIC ANALYZER

Use the CURSOR-right-arrow key to move the cursor two locations to the right. Now type in a different line number. See that the display window is repositioned to the location in memory which includes the line number you just typed in.

# **Simple Timing Measurements**

The following procedure shows you how to make measurements of timerelated activity in logic systems. You will see how to trigger traces of electrical activity and how to compose desired displays and measure activity on the displays

### **Activating The Timing Analyzer**

- 1. Press the SYSTEM key.

- Press the ROLL-down-arrow one time or CURSOR-down-arrow two times. This moves the bright bar to the second analyzer configuration. All channels which can collect timing information are activated for timing measurements. No channels are active for state measurements. See figure 3-11.

Figure 3-11. Selecting The Timing Analyzer Configuration In 1630D (1630A has 8 less channels)

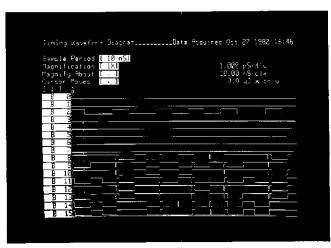

Figure 3-12. Default Timing Measurement For 1630D (1630A has 8 less channels)

3 Press the RUN key. The analyzer will execute a measurement at the default specification (trigger on anything), and present a waveform display on screen. This display is at X1 magnification. It shows the entire 1K memory content on screen. Unconnected timing bits are constant lows. See figure 3-12.

### **Controlling The Timing Display**

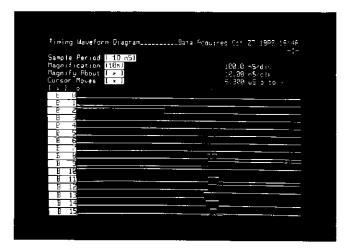

- 1 Press the CURSOR-down-arrow to select the Magnification field.

- 2 Press the NEXT[] key to obtain 4X magnification. This shows a window in the timing memory. One-fourth of the memory is on screen

- Press the ROLL-down-arrow to see the window move through the timing memory (display moves across the screen)

- Press the NEXT[] key several times to see the magnifications available. Select a magnification factor that leaves several waveform transitions on screen.

3-16 1630A/D LOGIC ANALYZER

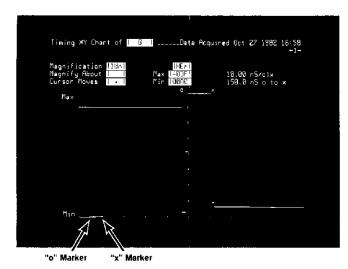

- 5. Press and hold the CURSOR-right-arrow key until the "x" marker moves out onto the display area. Place the "x" marker on one of the waveform transitions on the display. The first line above the waveforms on the right-hand side of the screen shows the measurement of time between the start of the memory and the position where you placed the "x" (o to x).

- Press the NEXT[] key several times to see that magnification of the display occurs around the area in memory you selected by the position of "x". See figure 3-13.

- 7. Press the CURSOR-down-arrow to select the Magnify About field.

- 8. Press the NEXT[] key to change "x" to "o".

- 9. Move the cursor up into the "Magnification" field

- Press the NEXT[] key several times. Notice that display magnification now occurs around the position of "o" (at the start of the timing memory).

- 11. Select a magnification that leaves the "x" marker on screen

Figure 3-13. Magnification Around "x"

- Press the CURSOR-down-arrow key to select the "Cursor Moves" field

- 13 Press the NEXT[] key to change "x" to "o".

- 14 Press the CURSOR-right-arrow key and hold it to move the "o" out on the display. Notice the time measurement indication change as the "o" moves closer to the "x"

- 15 Place the "o" marker on another waveform transition on the display.

- 16 The time measurement indication on the display will show you the measure of time between the two waveform transitions you selected using the "x" and "o" markers.

- 17 With the cursor in the "Cursor Moves" field, press the NEXT[] key to obtain the [x&o] indication. With this selection, the "x" and "o" markers will move together and maintain a constant interval between them. You can use these two markers together to compare intervals between any two points of interest on the display.

- 18 Move the cursor into the "Magnification" field and use the NEXT[] key to obtain a X1 display

- 19 Use the CURSOR-right-arrow and CURSOR-left-arrow keys to move the "o" and "x" markers together to another set of waveform transitions on the display

- 20 Place the "x" marker on one of the waveform transitions

- 21 Move the cursor down into the "Cursor Moves" field and press the PREV[] key to select "Cursor Moves [o]".

- 22 If the events are not the same distance apart as the first set, use the CURSOR keys to move the "o" marker alone. You can measure the dimension between the two new waveform transitions

- 23. Press the CURSOR-left-arrow and CURSOR-right-arrow keys Notice that the "o" marker can cross the "x" marker, and the measurement indication above the traces will correct itself (show "x to o" or "o to x")

3-18 1630A/D LOGIC ANALYZER

#### Selecting Trace Positions On The Display

- Press the CURSOR-down-arrow key to move the cursor into the B5 field.

- Press the PREV[] key several times. You can place any of the bits from the timing memory at any location on the display. You can also turn off a display channel, if desired

- 3 Press the DELETE key several times. You can eliminate channels from the display, if desired. Note that the vertical display is magnified when eight or less channels are on screen.

- 4 Press the INSERT key several times. You can add channels to the display, up to a maximum of 16 channels in non-glitch mode and 8 in glitch mode. See figure 3-14.

- 5 Press the blue SHIFT key and DEFAULT This restores all channels in the display to their original positions

Figure 3-14. Selecting Waveform Positions On Display

#### Triggering On A Timing Event

- 1 Find a point on the waveform display where two of the channels are high at the same time that one of the other channels has a transition from low to high (change display magnification, if necessary) Write down these three channel numbers and their conditions

- 2. Press the TRACE key

- 3. Use the CURSOR keys to place the cursor in the row of X's in the Pattern field. This is an AND field. Its default state is all don't cares. All "1" or "0" specifications that you enter in this field must be met during the same clock period in order for the timing analyzer to recognize its trigger.

- 4. Use the CURSOR keys to place the cursor at the points in the "Pattern" field which correspond to the bits that you noted as having high states. Enter a "1" from the keyboard in each of these two bits. (B0 is the first bit on the right-hand side of the field.)

- 5. Use the CURSOR keys to place the cursor in the "Edge" field. The "Edge" field is an OR field. You can specify recognition of low-to-high transitions, high-to-low transitions, or both transitions in any of the bits where such selections are available. If any of the selected transitions occurs in any bit during a clock period, the entire field is satisfied.

- 6 Use the CURSOR keys to position the cursor on the point in this field corresponding to the bit you noted as having a low-to-high transition (B0 is on the right-hand side).

- 7 If there is a dot in the field where you positioned the cursor, press the NEXT[] key one time to obtain the rising-edge arrow. If there is an N/A (not available) notation in this field, you will have to return to the WFORM display and select new channels, a different one with a low-to-high transition and two other channels that are high, if required. Edge recognition is not available for all of the timing bits. See figure 3-15.

3-20 1630A/D LOGIC ANALYZER

Figure 3-15. Triggering On A Pattern And Edge Transition

- 8 Press the RUN key. The analyzer will search the incoming activity until it finds a clock period in which both of the high channels you specified are high and a low-to-high transition occurs in the channel you selected. Then the analyzer will trigger a trace and fill its memory.

- 9 See figure 3-16. Note the vertical, dashed line on the display. This line identifies the trigger point.

- Move the cursor up into the "Sample Period" field and press the NEXT[] key several times.

- 11 Press the RUN key to take a measurement using the new sample period

Figure 3-18. State Analyzer System Configuration

#### **Setup For Relocation Use**

- 1 Press the SYSTEM key.

- 2 Press the ROLL-up-arrow one time to select use of the analyzer as a state measurement instrument. See figure 3-18.

- 3. Press the FORMAT key.

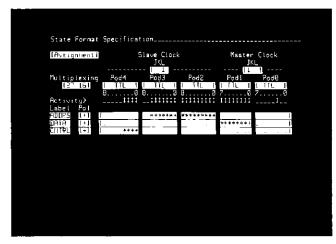

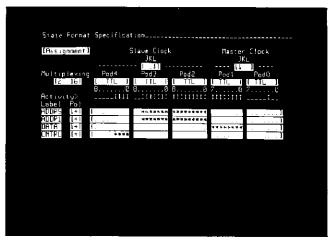

- Set up the [Assignment] menu of the State Format Specification as in figure 3-19. Move the cursor into the appropriate fields and use the NEXT[] or PREV[] keys and the keyboard keys, as required.

#### NOTE

This is the correct assignment setup for a system using an Intel 8085 microprocessor. You may need to change clock assignments if your system uses a different microprocessor.

3-24 1630A/D LOGIC ANALYZER

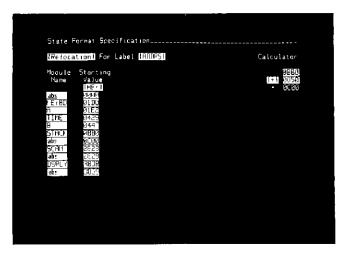

Figure 3-19. State Assignment Format Specification For 1630D (1630A does not have POD0)

- 5. Move the cursor into the [Assignment] field

- 6 Press the NEXT[] key to get [Relocation] on screen.

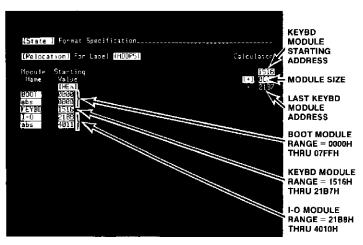

- 7 Press the CURSOR-right-arrow one time. You should have "For Label [ADDRS]" on screen. If not, press the NEXT[] key or PREV[] key until you have [ADDRS].

- Use the CURSOR-down-arrow to place the cursor in the abs 0000 field. The code starting at this address is not named in the example listing of figure 3-17. This code can be shown in absolute values.

- Press the INSERT key. This brings up a new field for entry of the next starting address. The cursor will be in the first position for entry of the new module name.

- 10. Type in KEYBD from the analyzer keyboard

- 11. Move the cursor into the Starting Value area and type in 01D0 from the analyzer keyboard

- 12. Press the INSERT key. The number of addresses used by KEYBD is 0012H. The next module (TIME) does not start right after KEYBD. There is unnamed code in the address space between the end of the KEYBD routine and the start of TIME. Determine the starting address value of this unknown code, as follows.

- Move the cursor into the upper field of the Calculator, and type in 01D0 (the starting address of KEYBD)

- b Move the cursor into the middle field of the Calculator, and type in 0012 (the number of addresses used by the KEYBD routine).

- c. The bottom field of the Calculator shows 01E2 (the first address after the end of the KEYBD routine). This is the starting address of the undefined code. Assign name A to this undefined code space.

- 13 Move the cursor to the bottom [abs] field under Module Name and type in A.

- 14 Place the cursor in the Starting Value area for the block of absolute code labeled A. Then type in 01E2 from the keyboard

- 15. Press the INSERT key.

- 16. Type in TIME from the analyzer keyboard

- 17. Place the cursor in the "Starting Value" field, and type in 0429

- 18. Press the INSERT key. Again, there is unknown code between the end of the present routine and the start of the next routine. You can use the calculator to determine the address where unknown code begins by placing the address of the start of the last known routine on the top line (0429) and the number of steps in that routine on the second line (001E). Label the unknown code B, and enter its starting value (4047)

- 19. Press the INSERT key

- 20. Type in STACK from the analyzer keyboard

- 21. Move the cursor into the Starting Value field, and type in 0BB0.

3-26 1630A/D LOGIC ANALYZER

- 22 Press the INSERT key. Again, there is unknown code between the end of the present routine and the start of the next routine. Use the calculator to determine the address where unknown code begins by placing the address of the start of the last known routine on the top line (0BB0) and the number of steps in that routine on the second line (0050). Beside the bottom "abs" module name, enter its starting value (0C00).

- 23 Press the INSERT key

- 24 Type in SCAN from the keyboard.

- 25 Move the cursor into the Starting Value column, and type in 2828 from the keyboard (the address of an I/O single value).

- 26 Press the INSERT key

- 27 Move the cursor into the new field and type in 2829 in the Starting Value column (the first absolute address after the end of the I/O address).

- 28 Press the INSERT key.

- 29 Type in DSPLY from the analyzer keyboard.

- 30 Move the cursor into the Starting Value column, and type in 3838, the address of another IO location.

- 31 Press the INSERT key

- 32 Move the cursor into the Starting Value field and type in 3839 beside the bottom "abs" entry. Your display should be the same as in figure 3-20.

1630A/D LOGIC ANALYZER

3-27

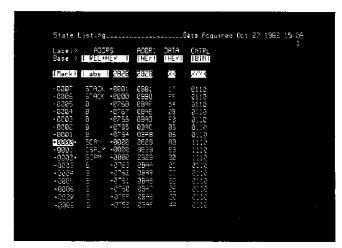

Figure 3-20. Relocation Menu Assignments

#### **Running A Trace With Relocation Addresses**