## Agilent E1437A

# 20 MSample/second ADC with Filters and FIFO

User's Guide

Agilent Part Number E1437-90002

Printed in U.S.A Print Date: March 2000, Third Edition

©Agilent Technologies, Inc., 1997, 2000. All rights reserved. 8600 Soper Hill Road Everett, Washington 98205-1209 U.S.A.

#### NOTICE

The information contained in this document is subject to change without notice.

AGILENT TECHNOLOGIES, INC., MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MANUAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Agilent Technologies shall not be liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### WARRANTY

A copy of the specific warranty terms applicable to your Agilent Technologies product and replacement parts can be obtained from your local Sales and Service Office.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Agilent Technologies, Inc.. This information contained in this document is subject to change without notice.

Use of this manual is restricted to this product only.

- © Copyright 1983, 1984, 1985, 1986, 1987, 1988, 2000 Agilent Technologies Inc. .

- © Copyright 1979 The Regents of the University of Colorado, a body corporate.

- © Copyright 1979, 1980, 1983 The Regents of the University of California.

- © Copyright 1980, 1984 AT&T Technologies. All Rights Reserved.

- © Copyright 1986, 1987 Sun Microsystems, Inc.

- © Copyright 1984, 1985 Productivity Products Intl.

#### **TRADEMARKS**

FibreXpress<sup>™</sup> is a trademark of Systran Corporation.

Tachyon<sup>TM</sup> is a trademark of Agilent Technologies Inc..

#### RESTRICTED RIGHTS LEGEND

Use, duplication or disclosure by the U.S. Government is subject restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013

Agilent Technologies, Inc. 395 Page Mill Road Palo Alto, CA 94303-0870 USA

Rights for non-DOD U.S. Government Departments and Agencies are as set forth in FAR 52.227-19(c)(1,2).

Copyright © 1997, 2000 Agilent Technologies, Inc., All rights Reserved.

### The E1437A at a Glance

The E1437A 20 Msample/second Analog-to-Digital Converter with Filtering and Memory provides high precision digitizing for time and frequency domain applications along with signal conditioning, filtering, and memory. The module plugs into a single C-size slot in a VXI mainframe.

Number of Channels Type of Input Input Bandwidth Sample Rate Voltage Range Raw ADC resolution VXI Bus Support VXI Device type Size 1

50 ohm

40 MHz, 8 MHz alias protected

20 MSamp/sec

20 mV to 10.24 Vpeak

23 bits

VME and Local Bus

Register/Message based

C-sized, single slot

### What you get with the E1437A

The following items are included with your E1437A

#### Hardware:

- E1437A ADC, C-size VXI module

- Software media:

MS-Windows<sup>®</sup> disks HP-UX tape

#### **Software:**

- ☐ MS-Windows disks

- A setup program which installs:

The E1437A VXI*plug&play* libraries and drivers

The E1437A HP-VEE driver

Soft Front Panel program for the E1437A

Windows online help for the E1437A

HPDSP function library and online help

Example programs

Library and example program source files

Microsoft® Visual Basic header files

### ☐ HP-UX tape

• An installation utility which installs:

The E1437A C Interface libraries and drivers

Helpview online help for the E1437A

HPDSP function library and online help

E1485 C library binaries

Example programs

Library and example program source and make files

#### **Documentation:**

- E1437A User's Guide (this book)

- Online manual pages for Windows and HP-UX (Windows Help and Helpview Help formats)

### In This Book

This book documents the E1437A module. It provides:

- installion information

- verification information

- operational information

- a programmer's reference

- circuit descriptions

- technical specifications

If you plan to use this module with the E1485A/B signal processing module and the 35635T Programmer's Toolkit you should also use the documentation for those products in order to form an application program development environment.

If you are using your E1437A module in the Windows 3.1®, Windows NT®, Windows 95®, or HP-UX environment the programmer's reference and other programming information are available as online help. The online help may be more convenient to use while programming. See the "Getting Started" chapter of this book for information on accessing the online help.

### TABLE OF CONTENTS

### 1 Installing the E1437A

Installing the E1437A 1-2

To inspect the E1437A 1-2

To install the E1437A 1-3

To store the module 1-6

To transport the module 1-6

### 2 Getting Started with the E1437A

Introduction 2-2

To Install the Programmer's Libraries 2-3

System Requirements (Microsoft Windows) 2-3

System Requirements (HP-UX) 2-3

To install the Windows VXIplug&play drivers for the E1437A

(for Windows 3.1, Windows 95 and Windows NT) 2-4

To install the HP-UX C-language drivers for the E1437A

(for HP-UX systems): 2-5

The Resource Manager 2-5

To Use the Program Group (Windows) 2-6

To Use the VXIplug and play Soft Front Panel (SPF) 2-7

To Use Online Help in Windows 2-10

To Use the Example Programs 2-11

To View the Visual Basic Example Program 2-14

To Use the HP-VEE Example Program 2-15

### 3 Using the E1437A

Programming the E1437A 3-2

WIN framework 3-2

HP-UX, Series 700 Environment 3-3

C Programming 3-3

ASCII Programming 3-4

Register Programming 3-4

The Measurement loop 3-5

The Measurement Loop in Multi-module systems 3-6

Frequency and Filtering 3-7

### Managing multiple modules 3-8

Clock distribution 3-8

Managing Multi-module Systems 3-10

Managing Multi-Mainframe Systems 3-11

Synchronizing Changes in Multi-module Systems 3-12

Synchronous Digital Filter Changes 3-12

Synchronous Center Frequency Changes 3-12

Transferring data 3-13

### 4 E1437A VXIplug&play Programmer's Reference

Introduction 4-2

Functions Listed by Functional Group 4-3

Analog Setup 4-4

Data Format 4-4

Debugging 4-5

Digital Processing 4-5

Diagnostics 4-5

Initialization 4-5

Interrupts 4-5

Measurement 4-6

Reading data 4-6

Timing 4-6

Trigger 4-6

Synchronization 4-7

Functions Listed alphabetically 4-8

VXIplug&play Programming Reference 4-11

Visual Basic Quick Reference 4-68

Parameter numeric equivalents 4-71

Errors 4-73

Functions Which Abort Measurements 4-75

### **5 ASCII Overview and Commands**

Introduction 5-2

Command Syntax 5-2

Special Syntactic Elements 5-2

Conventions 5-2

Using ASCII Commands in Your Environment 5-3

Using ASCII commands with HP BASIC 5-3

Using ASCII commands with VISA 5-3

ASCII Programming Reference 5-4

### **6 Module Description**

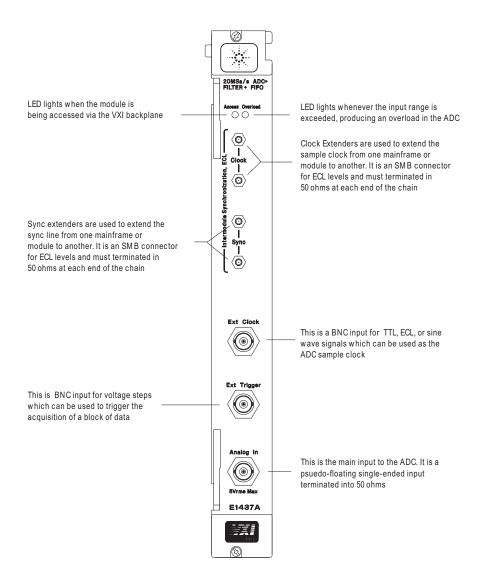

Front Panel Description 6-2

VXI Backplane Connections 6-3

Power Supplies and Ground 6-3

Data Transfer Bus 6-3

DTB Arbitration Bus 6-3

Priority Interrupt Bus 6-3

Utility Bus 6-3

Local Bus 6-3

Trigger Lines 6-4

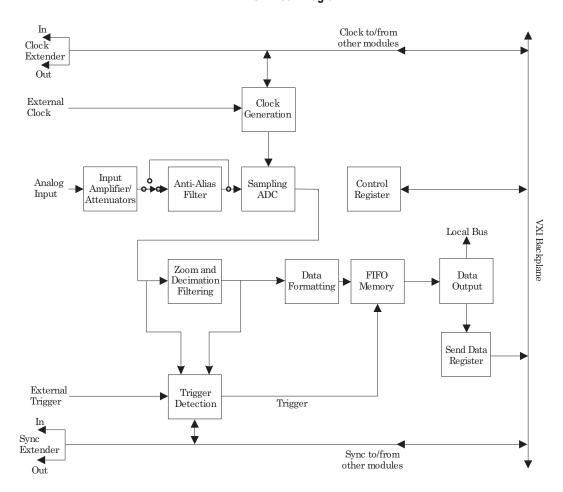

### Block Diagram and Description 6-5

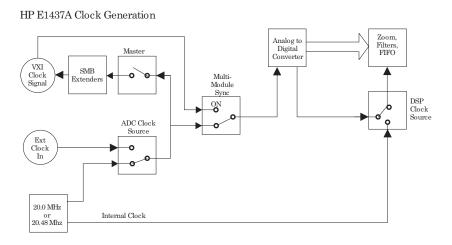

Clock Generation 6-6

Input Amplifier 6-6

Anti-alias Filter 6-6

Sampling ADC 6-7

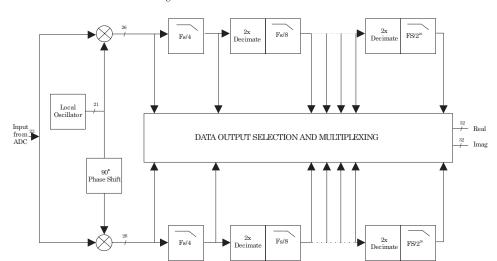

Zoom and Decimation Filtering 6-7

Data Formatting and FIFO Memory 6-8

Data Output 6-8

Trigger Detection 6-9

Control Registers 6-9

### 7 Verifying the E1437A

To verify the E1437A 7-2

### 8 Replacing Assemblies

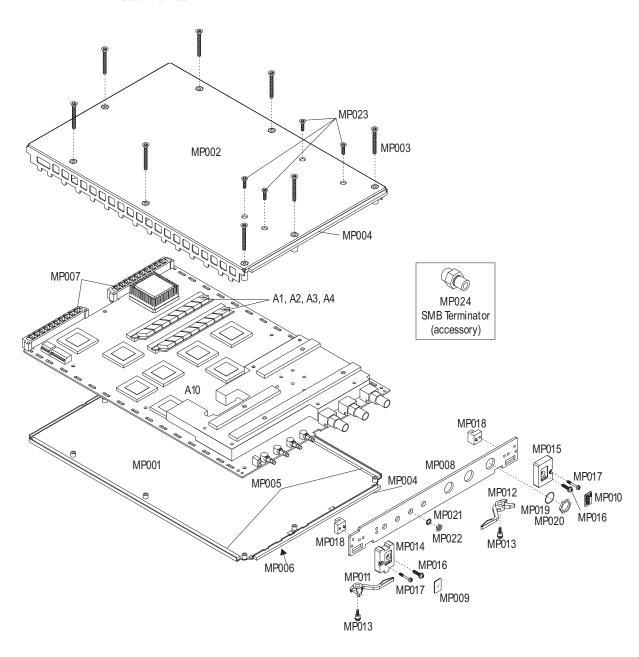

Replaceable Parts 8-2

Ordering Information 8-2

Direct Mail Order System 8-3

Code Numbers 8-3

Assemblies 8-4

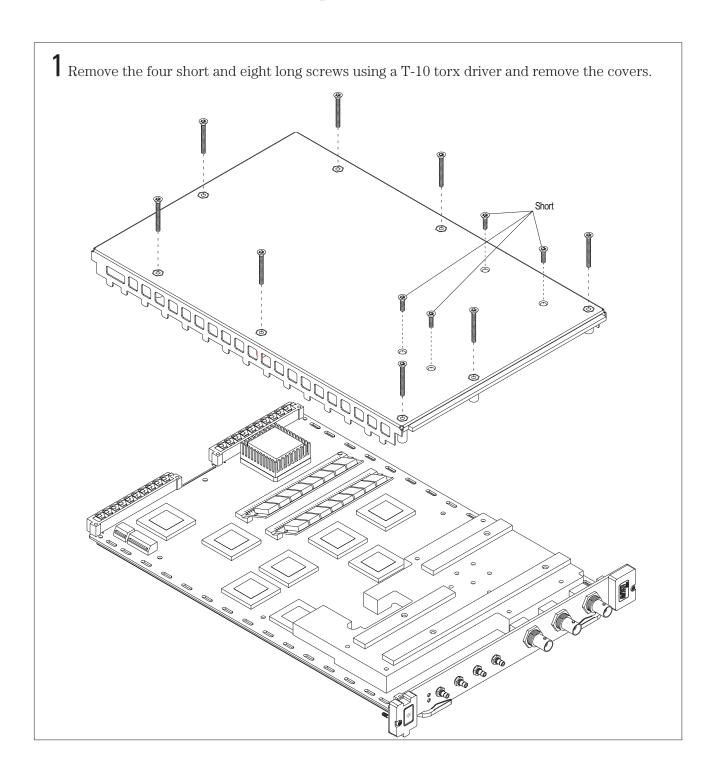

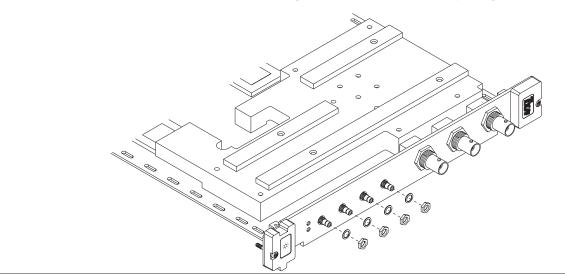

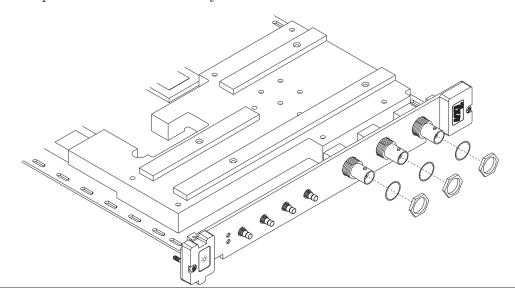

To remove the top and bottom covers 8-6

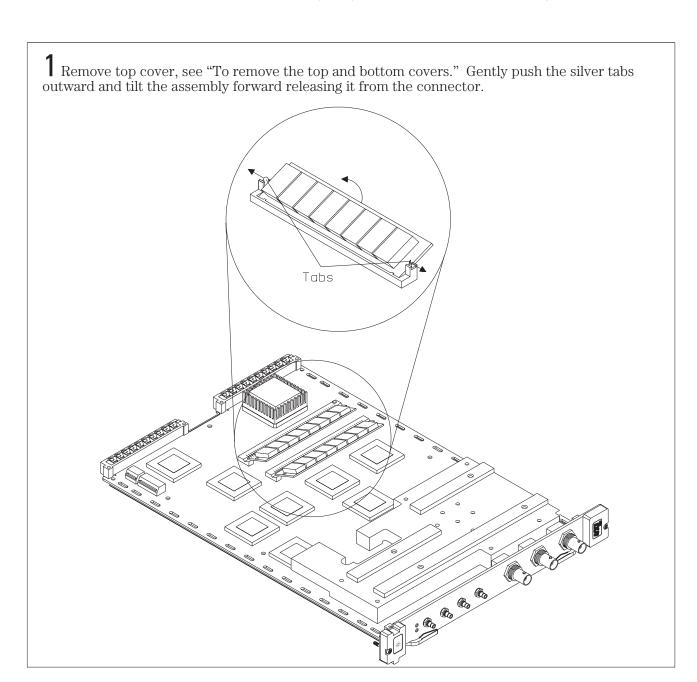

To remove the A1, A2, A3 or the A4 assembly 8-7

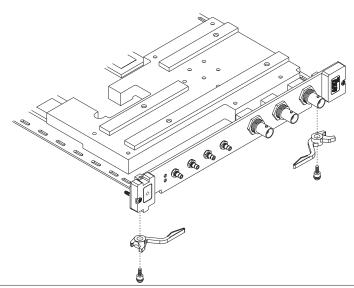

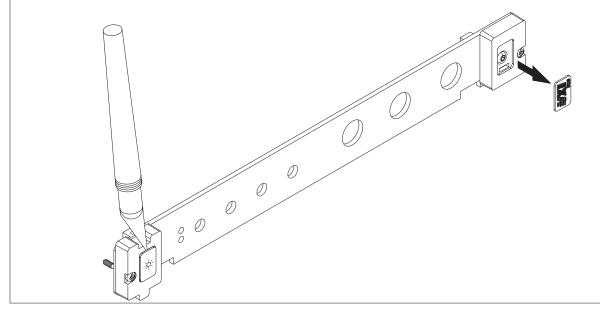

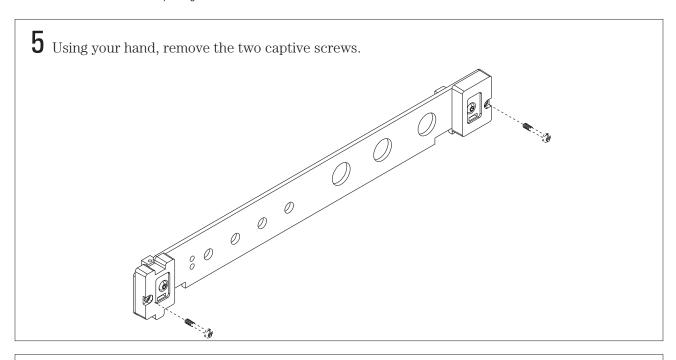

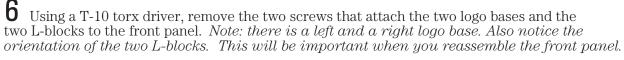

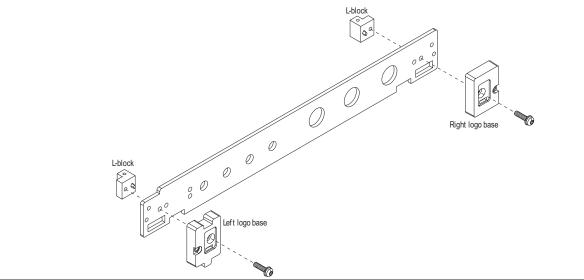

To remove the front panel 8-8

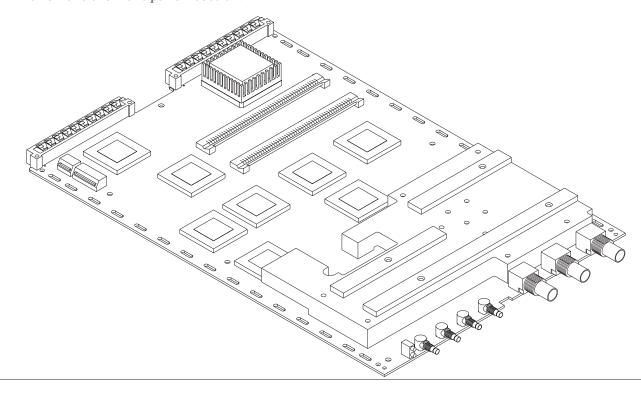

To remove the A10 main assembly 8-11

### 9 Backdating

Backdating 9-2

Table of Contents

Glossary

Index

**Need Assistance?**

**About this Edition**

1

Installing the E1437A

### Installing the E1437A

This chapter contains instruction for installing the E1437A VXI ADC Module and its drivers. This chapter also includes instruction for transporting and storing the module.

### To inspect the E1437A

The E1437A single channel VXI ADC Module was carefully inspected both mechanically and electrically before shipment. It should be free of marks or scratches and it should meet its published specifications upon receipt.

If the module was damaged in transit, do the following:

- Save all packing materials.

- File a claim with the carrier

- Call your Hewlett-Packard sales and service office.

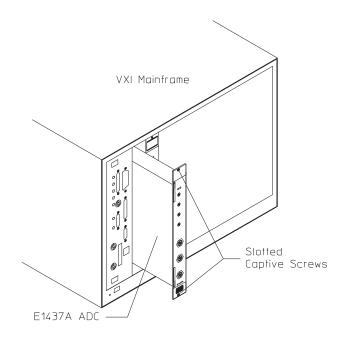

### To install the E1437A

#### Caution

To protect circuits from static discharge, observe anit-static techniques whenever handling the  $E1437A\ VXI\ ADC\ Module$

- 1 Set up your VXI mainframe. See the installation guide for your mainframe.

- 2 Select a slot in the VXI mainframe for the E1437A module

The E1437A module's local bus receives ECL-level data from the module immediately to its left and outputs ECL-level data to the module immediately to its right. Every module using the local bus is keyed to prevent two modules from fitting next to each other unless they are compatible. If you will be using the local bus, select adjacent slots immediately to the left of the data-receiving module. If the VXI bus is used, maximum data rates will be reduced but the module can be placed in any available slot.

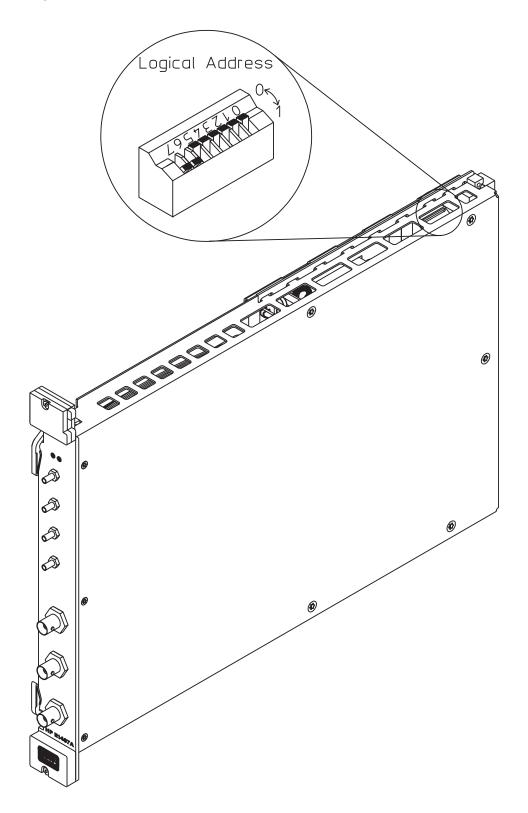

- **3** Using a small screwdriver or similar tool, set the logical address configuration switch on the E1437A.

(See the illustration on the next page.) Each module in the system must have a unique logical address. The factory default setting is 1100 0000 (192). If an GPIB command module will be controlling the E1437A module, select an address that is a multiple of 8.

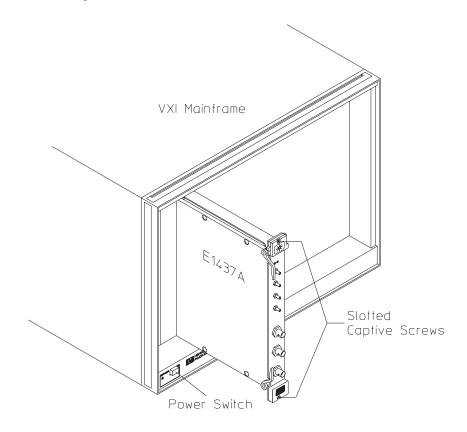

### 4 Set the mainframe's power switch to off (0).

### **Caution**

Installing or removing the module with power on may damage components in the module.

- **5** Place the module's card edges (top and bottom) into the module guides in the slot.

- **6** Slide the module into the mainframe until the module connects firmly with the backplane connectors. Make sure the module slides in straight.

- **7** Attach the module's front panel to the mainframe chassis using the module's captive mounting screws.

### To store the module

Store the module in a clean, dry, and static free environment

For other requirements, see storage and transport restriction in "Technical Specifications".

### To transport the module

- Package the module using the original factory packaging or packaging identical to the factory packaging.

- If returning the module to Hewlett-Packard for service, attach a tag describing the following:

- Type of service required

- Return address

- Model number

- Full serial number

In any correspondence, refer to the module by model number and full serial number.

- Mark the container FRAGILE to ensure careful handling.

- If necessary to package the module in a container other than original packaging, observe the following (use of other packaging is not recommended):

- Wrap the module in heavy paper of anti-static plastic.

- Protect the front panel with cardboard.

- Use a double-wall carton made of at least 350-pound test material.

- Cushion the module to prevent damage.

#### Caution

Do not use styrene pellets in any shape as packing material for the module. The pellets do not adequately cushion the module and do not prevent the module from shifting in the carton. In addition, the pellets create static electricity which can damage electronic components.

2

Getting Started with the E1437A

### Introduction

This chapter will help you to get your E1437A running and making simple measurements without programming. It shows you how to install the software libraries and how to run the Soft Front Panel program. It also introduces you to example programs.

Two versions of the Host Interface Library are available. One is the Windows 3.1, Windows 95, and Windows NT Library which communicates with the hardware using VISA (Virtual Instrument Software Architecture). VISA is the input-output standard upon which all the VIXplug&play software components are based. The second version is the HP-UX 9.x C-language Host Interface Library which uses SICL (the Standard Instrument Interface Library) to communicate with the E1437 hardware.

### To Install the Programmer's Libraries

#### **System Requirements (Microsoft Windows)**

- An IBM-compatible personal computer.

- Microsoft Windows ® 3.1, Microsoft Windows 95®, or Microsoft Windows NT®.

- The computer must have a 3 1/2 inch disk drive for the installation media.

### System Requirements (HP-UX)

- One of the following workstations

- An HP/Agilent V743 VXI-embedded workstation.

- A stand-alone HP/Agilent Series 700 workstation with an E1489 EISA-to-MXIbus card and an E1483B VXI-MXI Bus Extender.

- The workstation must have a DAT drive for the installation media.

- HP-UX (version 9.x)

- HP SICL for HP-UX (version C.03.08a or later). The SICL product number is HP E2091C.

# To install the Windows VXI*plug&play* drivers for the E1437A (for Windows 3.1, Windows 95 and Windows NT)

This procedure assumes that you have already installed a VISA (Virtual Instrument Software Architucture) library. If not, you can still install these drivers but you will receive an error message reminding you to install the VISA library.

- 1 Insert the disk labeled: "Agilent E1437A 20 MSample/sec A-to-D Converter"

- 2 Run the program: *drive*:\setup.exe

Where *drive* represents the drive containing the setup disk.

- 3 Insert the second disk when prompted

- 4 The setup program asks you to confirm or change the directory path. The default directory path is recommended.

- 5 A dialog box asks if you want to install startup icons

This creates a program group called "HPE1437" which includes:

An icon to run the Soft Front Panel

An icon for the E1437A Online Help file

An icon for the HPDSP Online Help file

An icon for UNINSTALL

Several icons for example programs

An icon for a readme file

6 A readme file may be displayed. If so, be sure to read it and follow the instructions.

# To install the HP-UX C-language drivers for the E1437A (for HP-UX systems):

- 1 Log in as root.

- 2 Insert the "Agilent E1437A 20 MSample/sec A-to-D Converter" tape into the tape drive

- 3 To run the software installation utility interactively type: /etc/update

See the HP-UX Reference manual for information on the update command.

Be sure to read the README file which contains important information on installation, viewing online help, and compiling example programs.

### The Resource Manager

The Resource Manager is a program from your hardware interface manufacturer. It looks at the VXI mainframe to determine what modules are installed. You need to run it every time you power up. If you get the message: "No HP E1437A can be found in the system." then run the Resource Manager.

Before running the E1437A software make sure that your hardware is configured correctly and that the Resource Manager runs successfully. Before using your measurement system, you must set up all of its devices, including setting their addresses and local bus locations. No two devices can have the same address. Usually addresses 0 and 1 are taken by the Resource Manager and are not available.

For more information about the Resource Manager, see the documentation with your hardware interface.

### NOTE

Most Resource Managers will recognize the manufacturer and model number of the E1437A but if your interface requires that you enter this information manually, use the following:

Manufacturer number: 4095 (Hex FFF)

Model number: 534 (Hex 216)

### To Use the Program Group (Windows)

If you chose to install the program group during the installation procedure you will have an icon for a program group similar to one of the two below, depending on which Windows platform you use.

This program group contains icons which access the Soft Front Panel program, online help, and example programs. The following pages provide an overview of these items.

If you did not choose to install the program group, executable files for each of the items represented by group icons are available in the drive:\vxipnp directory and its subdirectories.

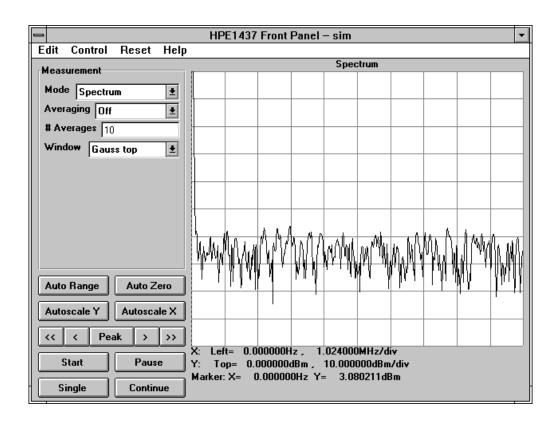

#### To Use the VXIplug&play Soft Front Panel (SPF)

The the best place to start to explore the capabilities of the E1437A is with the Soft Front Panel (SFP). The Soft Front Panel can be useful for checking your system to make sure that is is installed correctly and that all of its parts are working. It can also be used to make actual measurements, since it accesses most of the E1437A's functionality.

Select the E1437 Front Panel icon in your program group to start the SFP. This assumes you have already installed all required hardware and drivers (including VISA) and have run the configurator and Resource Manager required by your hardware interface.

When prompted for the resource descriptor, use the default "VXI::192" unless the logical address of the E1437 has been changed from its default setting of 192. If it has been changed then type the appropriate logical address instead of 192. Press OK.

You can also run the SFP in a simulation mode without an E1437 by typing "sim" in place of the resource descriptor.

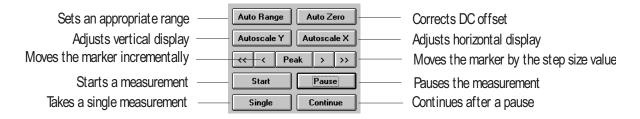

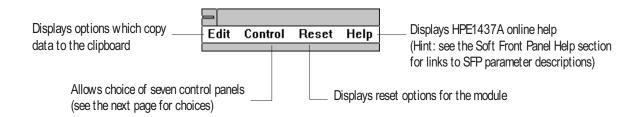

The buttons at the lower left of the SFP are always accessible and control various measurement and control functions.

The menu bar at the upper left of the SFP allows you to select pull-down menus.

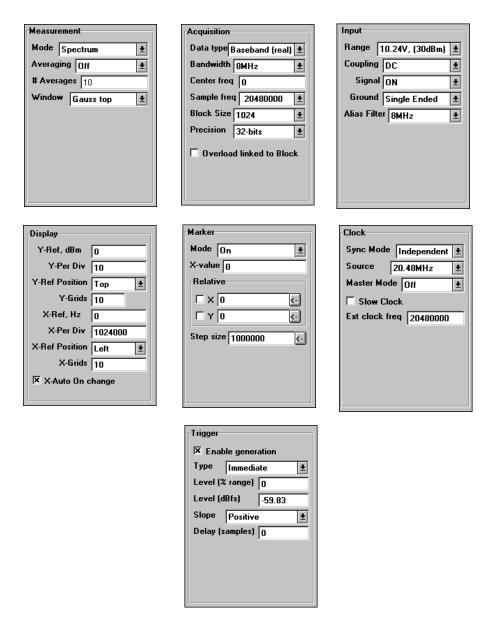

The left center section of the SFP is an area for which you may select various panels to control the measurement and display parameters. These panels are available as selections from the Control pull-down menu:

Hint: the E1437 online help, available from the SFP Help menu item or from the program group icon, describes these panels and has links to functions which control and define many of the parameters.

### To Use Online Help in Windows

The E1437 Help icon accesses the online help file for the E1437A. The online help includes the programming library as well as general information.

The DSP help icon accesses the online help file for the HPDSP library functions. These functions may be used to synthesize, resample, or perform special computations on data generated by the E1437A.

### To Use the Example Programs

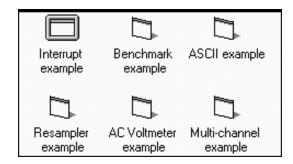

Several example programs are included to perform useful tasks for you and to serve as a basis for your own programs. When you installed your E1437A Windows or HP-UX libraries and drivers using the setup program or utility, you also installed executable and source code files for several useful example programs. The programs demonstrate programming the module with "C", Microsoft Visual Basic, and HP-VEE.

The executables for these examples require E1437A and, for Windows, VXIplug&play support; in other words they will not run in simulation mode like the E1437 Soft Front Panel program.

Icons for the executables appear in the E1437 Windows program group if you chose to add it during setup:

In Windows environments executable files and source code for the Microsoft Visual Basic examples are installed in the drive:\vxipnp\win[95|NT]\hpe1437\vb40 directory. The VEE examples are in the ...\hpe1437\wee directory, and "C" examples are in the ...\hpe1437\msc directory.

In the HP-UX environment executable files and source code for the C-language examples are installed in /opt/vxipnp/hpux/hpe1437/demo.

The group of programs described here may be supplemented with additional programs later which will be described in the online help or readme file.

#### acvolts.exe, acvolts\_32.exe, acvolts

This is about the simplest practical complete program using the E1437 and functions like an AC voltmeter. It is written in Visual Basic and can be run on Win 3.1 (acvolts.exe), Win95 or WinNT (acvolts\_32.exe). It is also available in C for HP-UX (acvolts).

#### ascii.exe, ascii\_32.exe, ascii

This example shows how to control the E1437 without using the C-function library. Since all I/O is performed with ASCII commands and the VXI message protocol, the speed is substantially reduced. This example still uses the VISA I/O library to send and receive ASCII commands, however any environment capable of ASCII I/O to VXI could be used. Users interested in controlling the E1437 via a command module should look at this example. The code is written in Visual Basic and can be run on Win 3.1, Win95, or WinNT.

#### resamp\_32.exe, resamp\_

This example shows how to use the resample function included in the HPDSP library shipped with the E1437. It is written in Visual Basic and runs on Win 3.1 (resamp.exe), Win95, or WinNT (resamp\_32.exe). It is also available in C for HP-UX (resamp).

### multchan.exe, multchan\_32.exe, multichan

This example shows how to synchronize two modules to achieve simultaneous sampling, filter decimation, and matched local oscillator phase. It is written in Visual Basic and runs on Win 3.1 (multchan.exe), Win95 or WinNT (multchan\_32.exe). It is also available in C for HP-UX (multichan).

#### bench.exe, bench\_32.exe, bench

This performance benchmarking program is really more of a utility than an example, although source code is provided. It allows users to measure data transfer rates and command processing times on their system without having to write new code. The utility is written in Visual Basic and runs on Win 3.1 (bench.exe), Win95 or WinNT (bench\_32.exe). It is also available in C for HP-UX (bench).

#### demo

This is a simple non-interactive oscilloscope display and is written in C for the HP-UX environment only.

#### interupt.exe

This example shows how to set up and trap a VXI interrupt to indicate an error condition in the E1437. It is written as a consol program in Microsoft Visual C++ and runs only on Win95 or WinNT. Source code is installed on Win 3.1, but no executable is provided.

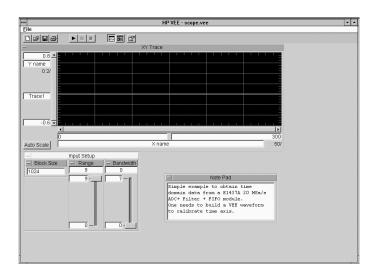

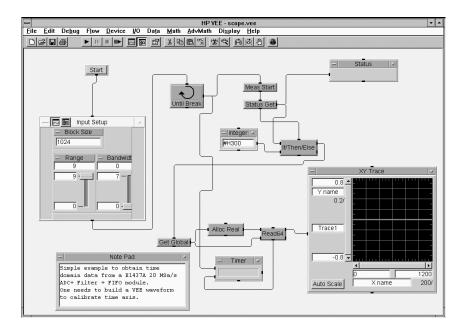

#### scope.vee

This is a simple one-channel example written in VEE. In order to view or execute it, the VEE programming environment must be installed on the system. It is not installed on Win 3.1 or HP-UX.

#### thruput.vee

This VEE example demonstrates how to set up a Local Bus data transfer from the E1437 to an E1562 data disk module. To use this example the VEE programming environment and the E1562 driver must be installed on the system. It is not installed on Win 3.1 or HP-UX.

The next few pages show the structure and some details of a few of the example programs

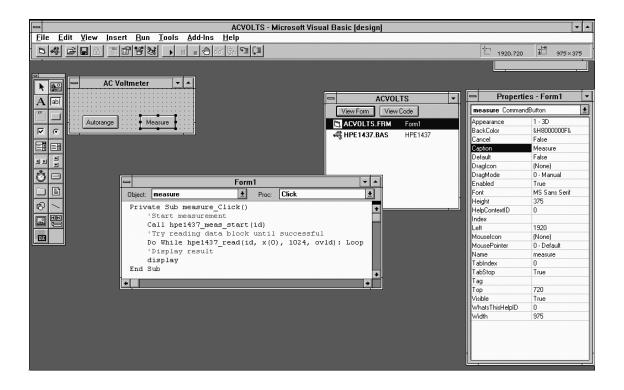

#### To View the Visual Basic Example Program

The acvolts.vbp project from which the acvolts.exe example program was created demonstrates how to communicate with the E1437A module in Visual Basic. The example below shows the open project with an open form and an open object.

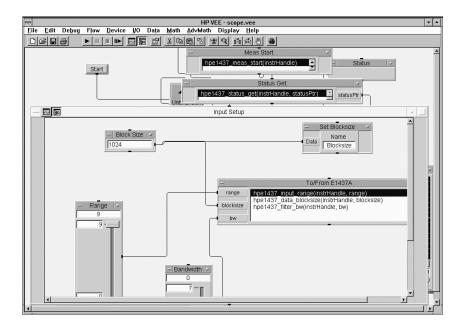

#### To Use the HP-VEE Example Program

The scope.vee program demonstrates a simple example of how to use the E1437A in a HP-VEE program. Load HP-VEE and the scope.vee. You may run the program to measure a signal and may select input parameter variables in the boxes provided.

You may also view the detail of the HP-VEE program to see how the program is structured:

The view below shows detail within the input setup, meas start and status get boxes. These are examples of how HP-VEE communicates with the E1437A module.

3

Using the E1437A

### Programming the E1437A

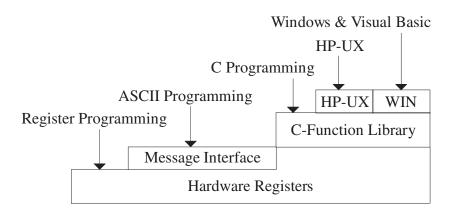

The E1437A is shipped with software and documentation to support a broad set of choices of controllers, I/O interfaces, programming languages, and operating systems. By virtue of its compliance to the VXI*plug&play* standard, the E1437A is most easily controlled in an environment conforming to one of the supported VXI*plug&play* frameworks. However, support is also supplied for other common hardware and software environments. The relationship among the various levels of programming the E1437A is shown in the diagram below.

#### WIN framework

The primary development environment supported by the E1437A is the VXI*plug&play* WIN, WIN95, and WinNT framework specifications. It requires the following resources prior to the installation of the E1437A:

- An embedded or a stand-alone IBM compatible PC

- Microsoft Windows 3.1 or higher

- VISA interface library

- VISA compatible hardware interface

- $\bullet \quad \text{Microsoft Visual C++ and/or Microsoft Visual Basic development system}.$

Additional details on the WIN framework can be found in the  $VXIplug\&play\ VPP-2$  System Frameworks Specification, Revision 2.0.

In addition to the C source code files, the E1437A includes compiled libraries, example programs, an interactive soft front panel program, online help files, and an installation program. The interactive soft front panel program allows the E1437A to be turned on, verified and used for simple tasks without writing any user programs.

Compliance with the VXI*plug&play* WIN framework allows users of the HP-VEE graphical programming system to control the E1437A from that environment. This is accomplished by the capability of HP-VEE to call functions in the C-library. Documentation and support for that capability is included with HP-VEE and is not addressed further in this document.

### **HP-UX**, Series 700 Environment

Although HP-UX will not support an official VXI*plug&play* framework before version 10.2, the HP-UX environment is supported for developers who prefer programming tools provided on the UNIX operating system. The system requirements include:

- HP/Agilent series 700 workstation

- HP-UX operating system 9.x

- Standard Instrument Control Library (SICL)

- SICL compatible VXI hardware interface

- C-language programming system.

In addition to the source code files, the E1437A includes compiled libraries, example programs, online help files, and an installation utility.

### **C** Programming

The E1437A is shipped with a source library of C-functions which can be called from user programs. This elevates the interface above the register level so the programmer no longer has to be concerned with such things as register addresses and packing or splitting parameters into 16-bit register lengths. The library includes ANSI compliant source code files with all machine dependent code constrained to a single source file. By re-writing selected portions of the *machine.h* file, the programmer can create and compile an E1437A library which is compatible with virtually any development environment using the C language. The most common reason for re-writing *machine.h* is to accommodate I/O libraries other than VISA or SICL. In some cases the library may need merely to be re-compiled to target a different processor type for the host computer.

Porting the E1437A library to a different computer environment is likely to be a fairly straight forward task. However, some of the higher level tools shipped with the E1437A may not be as easily ported. The interactive soft front panel and some example programs include human interfaces which depend on certain display and keyboard support which may be system dependent. Although source code is included for these applications, porting them to a different environment may present a greater problem than porting the library itself. The installation and online help utilities are specifically targeted to operate on the supported development environments and may not be available in other environments.

E1437A User's Guide Using the E1437A

### **ASCII Programming**

For programmers familiar with instrument control using ASCII string commands, the E1437A hardware implements a message based interface using ASCII commands compatible with the IEEE-488.2 standard. This standard defines the command syntax which is used by the Standard Commands for Programmable Instruments (SCPI) specification. For consistency with the new VXIplug&play function definitions, the E1437A ASCII command set does not use the SCPI commands.

Since the ASCII interpreter is built into the E1437A hardware, no host library is necessary for ASCII programming. Thus, there is no software to install. There is no need for a separate interpreter in the host computer (CSCPI or ISCPI). There is no need to download an interpreter to a separate command module. A key advantage of ASCII programming is that it can be done in virtually any VXI environment which supports message based I/O. A disadvantage of ASCII programming is the lack of host-based tools such as diagnostics and demonstration programs. An additional disadvantage is the reduction in I/O performance due to the character-based serial message interface and interpreter.

### **Register Programming**

The lowest level of programming supported by the E1437A allows direct writing and reading to the binary hardware registers. There is no user-level support for register programming.

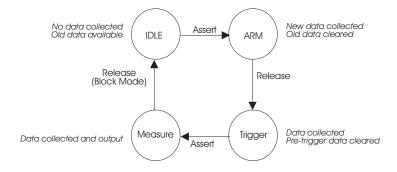

# The Measurement loop

The measurement loop progresses through four states. The transition from one state to the next is tied to the transition of the SYNC signal. The effect of the SYNC signal is summarized in the following diagram representing the four possible states of an E1437 module.

In the *Idle* state the E1437 places no new data into the FIFO output buffer memory although previously measured data is retained in the buffer memory and is available for output via the VME or local bus I/O ports. The module stays in the Idle state until the SYNC line is asserted.

Upon entering the Arm state the E1437 clears old data and starts saving new data into its FIFO. It remains in the Arm state until the SYNC signal is released. If an E1437 is programmed with a pre-trigger delay, it collects enough data samples to satisfy this pre-trigger delay, and then releases the SYNC line. If no pre-trigger delay has been programmed, the module releases the SYNC line immediately. When all E1437s in a system have released the SYNC line the module moves to the Trigger state.

Upon entering the *Trigger* state an E1437 continues collecting data into the FIFO, discarding any data prior to the pre-trigger delay. An E1437 remains in the Trigger state until the SYNC line is asserted. The SYNC line may be asserted by a direct command or by any E1437 which encounters a trigger condition and is programmed to assert the SYNC line. When the SYNC signal is asserted, all modules synchronously move to the *Measure* state.

In the *Measure* state the E1437 continues collecting data and sends the data saved in the FIFO memory to the selected I/O port, starting with the sample indicated by the trigger arrival, offset by the trigger delay. This data transfer continues until all data has been transferred or until the module meets the criteria for returning to the Idle state imposed by *block mode* or *continuous mode* operation constraints.

Modules programmed for *block mode* operation will assert the SYNC line until a complete block of data, including any pre-programmed pre- or post-trigger delay, has been collected and is available to the I/O port. The module then releases the SYNC line and returns to the Idle state.

E1437A User's Guide Using the E1437A

In *continuous mode* a module releases sync immediately but moves to the Idle state only if explicitly programmed to do so or if the FIFO data buffer overflows because data cannot be read from the I/O port fast enough.

#### The Measurement Loop in Multi-module systems

The following rules generally apply to transitions between states when multiple modules share a SYNC signal:

- If any one module *asserts* the SYNC line a synchronous state transition occurs for all modules in a system.

- All modules in a system must have *released* the SYNC line in order to bring about a synchronous transition to Trigger state.

- In block mode each module releases the SYNC line after its block of data has been collected. After each block mode module has released the SYNC line the individual module moves to the Idle state.

- Immediately upon entering the Measure state in continuous mode each module releases the SYNC line but does not move into the Idle state. It continues to collect and output data until it is programatically signaled to stop or until the FIFO overflows. With the SYNC line released it is then possible to change the center frequency for one or multiple modules without interrupting the measurement. See the section on Synchronizing Changes in Multi-Module Systems.

- A module may be programmed explicitly to inhibit its transition to the Arm state despite SYNC transitions.

- In addition to controlling the progression through the four module states, the SYNC signal is used to synchronize the decimation counters and local oscillators of multiple E1437 modules.

# Frequency and Filtering

The E1437's center frequency is normally set at zero (baseband measurement). However, you may set the center frequency to a non-zero value in order to examine a narrower span away from baseband (zoom measurement). The frequency band of interest, represented by digitized time data samples from the ADC, is mixed with the E1437 digital LO, a complex exponential, at the desired center frequency. As a result the frequency band of interest in the input signal is shifted to a complex signal centered around DC. See Synchronizing Changes in Multi-module Systems for special considerations with respect to changing the center frequency in multi-module systems.

The default filter for E1437 measurements is an analog anti-alias filter. However, you may further isolate the frequency band of interest for more detailed analysis by using digital filtering. A decimating digital filter simultaneously decreases the bandwidth of the signal and decreases the sample rate. The built-in digital filters conform to the Nyquist sampling theorem which guarantees that the output sample rate may be reduced by the same factor as the signal bandwidth reduction while still maintaining a complete representation of the underlying bandlimited signal.

For each octave step in bandwidth reduction (except for the first octave) the E1437 digital filters automatically reduce the data rate by discarding alternate output samples. This process, called decimation, results in an output sample rate which is nominally four times the signal bandwidth whenever sigBw>0. This is still double the theoretical rate necessary to fully characterize the band limited signal. However, because the digital filters do not have a perfectly abrupt cutoff, the sample rate cannot be reduced to the theoretical limit without some aliasing of signals in the transition frequency band of the filters. In many applications this limited aliasing potential is not important. For this reason you may optionally choose to apply a final factor-of-two decimation. See the Technical Specifications for detailed information on the digital filter shapes.

The decimation process used to reduce the output sample rate is driven from a "decimation counter" which keeps track of which samples to save and which ones to discard for each of the octave bandwidth reduction filter stages. In multi-module systems where synchronous sampling is required, the decimation counters in all the modules must be synchronous with each other. See Synchronizing Changes in Multi-module Systems.

# Managing multiple modules

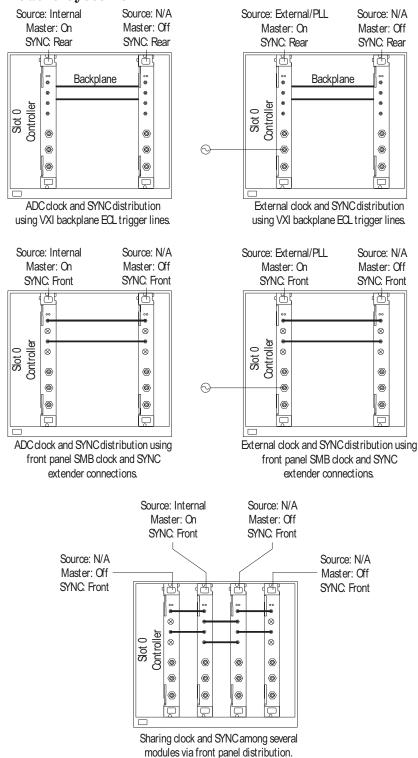

The E1437 supports synchronous operation among multiple E1437s by using a shared ADC clock and SYNC signal to drive all the modules in a system. The shared SYNC signal is used to synchronize critical operations including arming, triggering the beginning of data collection, setting a common phase of the local oscillator for down conversion, and forcing concurrent output sample times whenever decimation is used. The SYNC line transitions are constrained to not occur during the critical (setup and hold) regions of the shared ADC clock. Thus, all modules in the group can be assured of receiving the SYNC signal on exactly the same ADC clock cycle. The following topics provide details on sharing clock and SYNC signals:

#### **Clock distribution**

When shared, the ADC clock and SYNC lines are distributed among modules either on the VXI backplane using the ECL Trigger lines, or on the front panel using the SMB Clock/Sync extender connectors. When VXI backplane distribution is used with more than one VXI mainframe, the front panel Clock/Sync connectors can be used to buffer the ADC clock and SYNC lines from one mainframe to another.

Since the SYNC transition timing relative to the ADC clock edges is critical, the module driving the SYNC line should ideally be the same one identified as the master. However, when using backplane distribution, any E1437 in the same mainframe as the master can drive the SYNC line.

When using the multi-sync mode of operation, the selection of front panel or backplane distribution of ADC clock and SYNC signals involves the following considerations:

- Backplane distribution requires the use of the ECL Trigger lines on the backplane, which are then unavailable to other modules.

- The overall time skew between the arrival of ADC clock edges is smaller when using backplane distribution, particularly if the master (or buffer) module is physically located in the center of the mainframe.

- Backplane distribution is more susceptible to pickup of jitter on the ADC clock from other digital activity on the VXI backplane. The extent of this pickup depends on the mainframe and on the other modules in the mainframe. One important step in reducing this pickup is to disable, whenever possible, the 10 MHz VXI clock generated by the slot-0 controller.

- For backplane distribution make sure that all modules conform to VXI specification 1.4 or later with regard to their attachment to the ECL Trigger lines. See the Technical Specifications for the clock jitter (phase noise) specification degradation using backplane distribution.

- Front panel distribution requires the use of two short, relatively well matched cables with SMB connectors between modules. In addition, unused SMB connectors on modules being used for front panel distribution must be terminated in 50 ohms.

## **Managing Multi-module Systems**

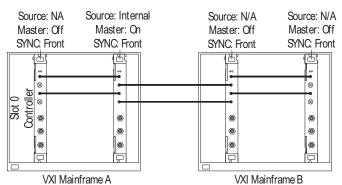

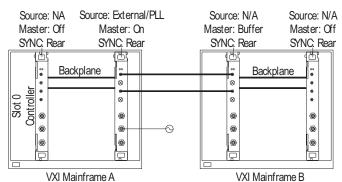

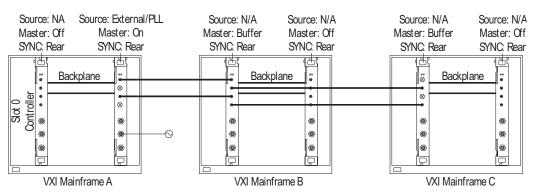

# **Managing Multi-Mainframe Systems**

Oock and SYNC distribution using front panel extender connections within and between mainframes.

Oock and SYNC distribution using VXI backplane lines within mainframes and using front panel extender connections between mainframes.

Three or more mainframes with clock and SYNC distribution using VXI backplane lines within mainframes and using front panel extender connections between mainframes.

#### **Synchronizing Changes in Multi-module Systems**

Multi-module systems require special treatment with respect to timing of frequency and filter changes. Center frequency changes may involve synchronizing the local oscillators of all modules in a system. Digital filters changes in multi-module systems require that the decimation counters be synchronized.

## **Synchronous Digital Filter Changes**

In multi-module systems where synchronous sampling is required, the decimation counters in all the modules must be synchronous with each other. This condition can be forced by preparing each module in the system in advance. Any measurement in progress is terminated at this time and the module is placed in the Idle state. After each module is prepared, the next SYNC line transition causes the digital decimation counter to be reset and started at the same time. Once this is done the decimation counters will stay synchronized as long as the same ADC clock is used.

If you also intend to change the center frequency along with the digital filters, you should synchronize the digital filters first. Otherwise the center frequency phase becomes unsynchronized when the digital filters are changed.

# **Synchronous Center Frequency Changes**

In multi-module systems you may prepare each module in advance of a frequency change, then perform the change synchronously by asserting the SYNC line. This preserves the phase relationship of the local oscillators for all modules in the system. Certain special considerations apply to multi-module frequency changes:

- If all modules in a system are in the Idle state when the SYNC line transition occurs, the LO frequency will be updated and the next measurement will be armed.

- If all modules are in the measurement state in continuous mode when the SYNC line transition occurs, the LO frequency will be synchronously updated, and the measurement will continue.

- In continuous mode care must be taken to assure that all modules are in the same state, either the Idle state or the Measure state, before the SYNC line transition occurs, otherwise some modules will re-arm while others will continue the current measurement.

- In block mode the SYNC line transition will be ignored unless all modules are currently in the Idle state.

- If you also intend to change the digital filters along with the center frequency, you should synchronize the digital filters first. Otherwise the center frequency phase becomes unsynchronized when the digital filters are changed.

# Transferring data

You can transfer data from the E1437 two different ways.

- The VMEbus is the universal data bus for VXI architecture. It provides flexibility and versatility in transferring data. Transfers over the VMEbus are 16 bits wide.

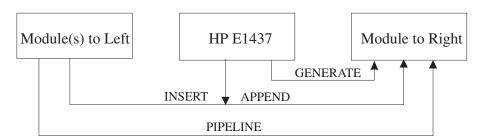

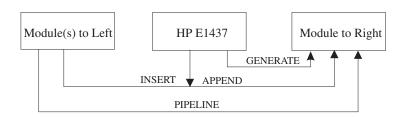

- The Local Bus supports faster transfer rates than the VMEbus. For example, if you are transferring data from the E1437 to the HP/Agilent E1485A/B, the Local Bus provides a direct pipeline to the HP/Agilent E1485's DSPs.

- Using the Local Bus, you can transfer data in the background while processing data in a signal-processing module. All Local Bus data transfers originate in the E1437 and move towards a signal processing module to the right of the E1437. If other modules generate data to the left of the input module, the E1437 will pass the data to its right and insert or append its own data at the beginning or end of the frame.

4

E1437A VXI*plug&play* Programmer's Reference

# Introduction

The programmer's reference is presented as a set of VXIplug&play functions since this is the primary targeted environment. However, when you performed the setup for the E1437A, drivers were installed to support various programming environments as described in the Programing Overview section in the "Using the E1437A" chapter.

The function descriptions in the programmer's reference are valid for all environments except ASCII, which is treated in a separate chapter. Be sure to follow the instructions in the "Getting Started" chapter to assure proper installation and to become aware of the capabilities of your E1437A software in various programming environments. You will find the example programs particularly helpful for programming in different environments.

Many of the function descriptions in the programming reference include several related functions. You may use the primary function to set all related parameters or you may use the other functions within the group to set or query a single parameter.

Parameter variables are presented as alphanumeric values which are descriptive and easy to remember. However, for faster programming you may use the numeric equivalents for the parameter variables listed at the end of this chapter. The numeric equivalents are available as popups in the online help, a good reason to use the online help, if it is available in your environment, rather than this printed document.

Unless noted otherwise, all functions in this library return 0 if they complete successfully and a non-zero integer if they fail. Always check the the return value and take appropriate action. The error descriptions are listed at the end of this chapter and in the online help.

# Functions Listed by Functional Group

The following pages have the programming functions grouped by related functions. The a brief description of each group follows:

## • Initializing the E1437:

You must first initialize the I/O driver and set up each module.

• Configuring the Analog Inputs:

The functions in this group determine how the analog input section is configured.

# • Formatting Data:

An E1437 can collect either real or complex data in 16-bit or 32-bit format. It can collect data into various blocksizes or in a continuous mode. This data can be transferred either on the VXI backplane of over the Local Bus. You can append status information to each block of data indicating ADC overloads or ADC errors during the block.

#### • Configuring Digital Processing:

The decimation filter provides bandpass filtering and decimation capabilities. You may also select limited frequency spans away from baseband.

• Controlling Measurements:

These functions initiate or terminate the measurement loop.

• Timing:

The clock signals for the ADC sample clock and DSP decimation and zoom can be set from a variety of sources. One E1437 can be enabled to drive the sample clock line on the VXI backplane or front panel to enable synchronization of multiple E1437s.

#### • Triggering:

These functions set all parameters associated with triggering the beginning of data collection.

#### • Controlling Multiple Modules:

These functions support synchronous operation among multiple E1437s by using a shared ADC clock and SYNC signal to drive all the modules in a system.

#### • Reading Data:

These functions read data from either the VME or the Local Bus data port. This data can optionally be scaled and converted to floating point.

#### • Programming Interrupts:

The E1437 can be programmed to interrupt via the VXI backplane whenever certain status conditions are present.

#### • Debugging your Program:

Error messages allow you to identify program problems.

### • Diagnostics:

Hardware diagnostic routines verify correct hardware operation of the E1437.

## **Analog Setup**

hpe1437\_input\_setup - sets all the analog input parameters

hpe1437\_input\_alias\_filter - include/bypasse the built-in analog anti-alias filter

hpe1437\_input\_alias\_filter\_get - gets the anti-alias filter state

hpe1437\_input\_autozero - nulls out the input DC offset

hpe1437\_input\_coupling - selects AC or DC input coupling

hpe1437\_input\_coupling\_get - get the input coupling type

hpe1437\_input\_float - enables/disables floating the input connector

hpe1437\_input\_float\_get - gets the input connector state

hpe1437\_input\_range - sets the full scale range

hpe1437\_input\_range\_auto - performs auto-ranging

hpe1437\_input\_range\_get - gets the input range

hpe1437\_input\_signal - include/bypass the input buffer amplifier

hpe1437\_input\_signal\_get - gets the input buffer amplifier state

#### **Data Format**

$hpe1437\_data\_-sets$  all format and data output flow parameters

$hpe 1437\_data\_append\_status - enables/disables \ appending \ status \ information \ to \ a \ datablock$

hpe1437\_data\_append\_status\_get - gets the append status state

hpe1437\_data\_blocksize - determines the size of the output data block

hpe1437\_data\_blocksize\_get - gets the output data block size

hpe1437\_data\_memsize\_get - returns module's memory size

hpe1437\_data\_mode - selects block mode or continuous mode

hpe1437\_data\_mode\_get - gets the data mode

hpe1437\_data\_port - selects VME bus or local bus transmission

hpe1437\_data\_port\_get - gets the output port designation

hpe1437\_data\_resolution - selects 16 or 32 bits data resolution

hpe1437\_data\_resolution\_get - gets the data resolution

hpe1437 data type - selects real or complex output data

hpe1437\_data\_type\_get - gets output data type

hpe1437 lbus mode - sets the transmission mode of the local bus

hpe1437\_lbus\_mode\_get - gets the local bus mode

hpe1437 lbus reset - resets local bus mode

hpe1437\_lbus\_reset\_get - gets the local bus mode reset state

## **Debugging**

hpe1437\_error\_message - returns error information obtained from function calls

hpe1437\_error\_query - queries the module for the most recent error

hpe1437\_revision\_query - returns strings that identify the date of the firmware revision.

hpe1437\_status\_get - retreives module's status register information

## **Digital Processing**

hpe1437\_filter\_setup - sets the digital filter bandwidth and decimation filter parameters

hpe1437\_filter\_bw - selects a signal filter bandwidth

hpe1437\_filter\_bw\_get - gets the signal filter bandwidth

hpe1437\_filter\_decimate - enables/disables and extra factor of 2 decimation

$hpe 1437\_filter\_decimate\_get-gets~current~state~of~extra~decimation$

$hpe 1437\_filter\_resp\_get-returns\ the\ module's\ complex\ frequency\ response.$

hpe1437\_filter\_sync - synchronizes the decimation filter counter

hpe1437\_frequency\_setup - sets all center frequency parameters

hpe1437\_frequency\_center - sets the center frequency

hpe1437\_frequency\_center\_get - gets the current center frequency

hpe1437\_frequency\_center\_raw - A fast way to set the center frequency

hpe1437\_frequency\_cmplxdc - selects a complex baseband measurement

hpe1437\_frequency\_cmplxdc\_get - gets the state of the baseband measurement mode

$hpe 1437\_frequency\_sync \text{ - prepares the module for a synchronous frequency change}$

hpe1437\_frequency\_sync\_get - gets the state of the synchronus change mode

## **Diagnostics**

hpe1437\_self\_test - performs a self-test on the module and returns the result

#### Initialization

hpe1437 init - initializes the I/O driver for a module

hpe1437\_close - closes the module's software connection

## **Interrupts**

hpe1437 attrib get - allows direct access to the I/O library functions

hpe1437\_interrupt\_setup - sets all interrupt parameters

hpe1437\_interrupt\_mask\_get - gets the interrupt event mask

hpe1437\_interrupt\_priority\_get - gets the VME interrupt line

$hpe1437\_interrupt\_restore$  - restores the interrupt masks to the most recent setting

#### Measurement

hpe1437 meas control - initiates and controls measurements in multi-module systems

hpe1437\_meas\_start - initiates measurements in single module systems

hpe1437\_reset - places the module in a known state

## Reading data

hpe1437\_data\_scale\_get - gets data scale factor

hpe1437\_read - reads scaled 32-bit float data from FIFO

hpe1437\_read64 - reads scaled 64-bit float data from FIFO, specifically for VEE applications

hpe1437\_read\_raw - - reads raw data from FIFO

#### **Timing**

hpe1437\_clock\_setup - sets all timing parameters

$hpe1437\_clock\_dsp$  - selects the clock used to drive the decimation/zoom section

hpe1437\_clock\_dsp\_get - gets the current decimation clock source

hpe1437\_clock\_fs - provides the frequency of an external sample clock

hpe1437\_clock\_fs\_get - gets the current external sample clock frequency

$\mbox{hpe}1437\_\mbox{clock}\_\mbox{master}$  - determines whether a module drives the VXI clock line with its ADC clock

$hpe1437\_clock\_master\_get-gets~the~module's~clock~master~state$

hpe1437\_clock\_multi\_sync - specifies whether the module uses a shared clock and sync

hpe1437\_clock\_multi\_sync\_get - gets the module's current shared clock and sync state

hpe1437\_clock\_source - selects the source of the ADC clock

hpe1437\_clock\_source\_get - gets the ADC clock source

## **Trigger**

$\mbox{hpe}1437\_\mbox{trigger}\_\mbox{setup}$  - sets all parameters associated with triggering the beginning of data collection

hpe1437\_trigger\_adclevel - specifies the threshold for the ADC trigger

hpe1437\_trigger\_adclevel\_get - gets the trigger threshold

hpe1437\_trigger\_delay - specifies a pre- or post-trigger delay time

hpe1437\_trigger\_delay\_get - gets the trigger delay time

$\mbox{hpe}1437\_\mbox{trigger\_delay\_actual\_get}$  - gets the actual delay time from the most recent trigger event

hpe1437 trigger gen - determines whether a module can generate a trigger

hpe1437\_trigger\_gen\_get - gets the trigger generation status

hpe1437 trigger maglevel - specifies the threshold for a magnitude trigger

hpe1437\_trigger\_maglevel\_get - gets magnitude trigger threshold

$\mbox{hpe}1437\_\mbox{trigger\_phase\_actual\_get}$  - gets the actual trigger phase from the most recent trigger event

hpe1437\_trigger\_phase\_capture - Allows LO phase capture in frequency-synchronized, multi-module zoom measurements.

hpe1437 trigger slope - selects a positive or negative trigger

hpe1437\_trigger\_slope\_get - gets trigger slope

hpe1437\_trigger\_type - determines the trigger type

hpe1437\_trigger\_type\_get - gets trigger type

# **Synchronization**

$\mbox{hpe}1437\_\mbox{clock}\_\mbox{master}$  - determines whether a module drives the VXI clock line with its ADC clock

hpe1437\_clock\_master\_get - gets the module's clock master state

hpe1437\_clock\_multi\_sync - specifies whether the module uses a shared clock and sync

hpe1437\_clock\_multi\_sync\_get - gets the module's current shared clock and sync state

hpe1437\_clock\_source - selects the source of the ADC clock

hpe1437\_clock\_source\_get - gets the ADC clock source

hpe1437\_filter\_sync - synchronizes the decimation filter counter

$\ensuremath{\mathsf{hpe}} 1437\_\ensuremath{\mathsf{frequency}}\xspace$  - prepares the module for a frequency change

hpe1437\_meas\_control - synchronizes arming and triggering in multi-module systems

hpe1437\_trigger\_gen - determines whether a module can generate a trigger

$hpe1437\_trigger\_gen\_get-gets\ the\ trigger\ generation\ status$

hpe1437\_wait - facilitates the synchronization and control of multi-module systems

# Functions Listed alphabetically

hpe1437\_attrib\_get - allows direct access to the I/O library functions

hpe1437\_clock\_dsp - selects the clock used to drive the decimation/zoom section

hpe1437\_clock\_dsp\_get - gets the current decimation clock source

hpe1437\_clock\_fs - provides the frequency of an external sample clock

hpe1437\_clock\_fs\_get - gets the current external sample clock frequency

hpe1437\_clock\_master - determines whether a module drives the VXI clock line with its ADC clock

hpe1437\_clock\_master\_get - gets the module's clock master state

hpe1437\_clock\_multi\_sync - specifies whether the module uses a shared clock and sync

hpe1437\_clock\_multi\_sync\_get - gets the module's current shared clock and sync state

hpe1437\_clock\_setup - sets all timing parameters

hpe1437\_clock\_source - selects the source of the ADC clock

hpe1437\_clock\_source\_get - gets the ADC clock source

hpe1437\_close - closes the module's software connection

hpe1437\_data\_append\_status - enables/disables appending status information to a data block

hpe1437\_data\_append\_status\_get - gets the append status state

hpe1437\_data\_blocksize - determines the size of the output data block

hpe1437\_data\_blocksize\_get - gets the output data block size

hpe1437\_data\_memsize\_get - returns module's memory size

hpe1437\_data\_mode - selects block mode or continuous mode

hpe1437\_data\_mode\_get - gets the data mode

hpe1437\_data\_port - selects VME bus or local bus transmission

hpe1437\_data\_port\_get - gets the output port designation

hpe1437\_data\_resolution - selects 16 or 32 bits data resolution

hpe1437\_data\_resolution\_get - gets the data resolution

hpe1437 data scale get - gets data scale factor

hpe1437\_data\_ -sets all format and data output flow parameters

hpe1437\_data\_type - selects real or complex output data

hpe1437\_data\_type\_get - gets output data type

hpe1437\_error\_message - returns error information obtained from function calls

hpe1437\_error\_query - queries the module for the most recent error

hpe1437\_filter\_bw - selects a signal filter bandwidth

hpe1437\_filter\_bw\_get - gets the signal filter bandwidth

hpe1437\_filter\_decimate - enables/disables and extra factor of 2 decimation

hpe1437\_filter\_decimate\_get - gets current state of extra decimation

hpe1437\_filter\_resp\_get - returns the module's complex frequency response.

hpe1437\_filter\_setup - sets the digital filter bandwidth and decimation filter parameters

hpe1437\_filter\_sync - synchronizes the decimation filter counter

hpe1437\_frequency\_center - sets the center frequency

hpe1437\_frequency\_center\_get - gets the current center frequency

hpe1437\_frequency\_center\_raw - A fast way to set the center frequency

hpe1437\_frequency\_cmplxdc - selects a complex baseband measurement

hpe1437\_frequency\_cmplxdc\_get - gets the state of the baseband measurement mode

hpe1437\_frequency\_setup - sets all center frequency parameters

hpe1437\_frequency\_sync - prepares the module for a synchronous frequency change

hpe1437\_frequency\_sync\_get - gets the state of the synchronus change mode

hpe1437\_init - initializes the I/O driver for a module

hpe1437 input alias filter - include/bypass the built-in analog anti-alias filter

$hpe1437\_input\_alias\_filter\_get$  - gets the anti-alias filter state

$hpe1437\_input\_$  - nulls out the input DC offset

hpe1437\_input\_coupling - selects AC or DC input coupling

hpe1437\_input\_coupling\_get - get the input coupling type

$hpe 1437\_input\_float-enables/disables\ floating\ the\ input\ connector$

$hpe1437\_input\_float\_get-gets\ the\ input\ connector\ state$

hpe1437\_input\_range - sets the full scale range

hpe1437\_input\_range\_auto - performs auto-ranging

hpe1437\_input\_range\_get - gets the input range

hpe1437\_input\_setup - sets all the analog input parameters

hpe1437\_input\_signal - include/bypass the input buffer amplifier

hpe1437 input signal get-gets the input buffer amplifier state

hpe1437\_interrupt\_mask\_get - gets the interrupt event mask

hpe1437\_interrupt\_priority\_get - gets the VME interrupt line

hpe1437\_interrupt\_restore - restores the interrupt masks to the most recent setting

hpe1437\_interrupt\_setup - sets all interrupt parameters

hpe1437 lbus mode - sets the transmission mode of the local bus

$hpe1437\_lbus\_mode\_get$  - gets the local bus mode

hpe1437 lbus reset - resets local bus

hpe1437\_lbus\_reset\_get - gets the current local bus reset state

hpe1437\_meas\_control - initiates and controls measurements in multi-module systems

hpe1437 meas start - initiates measurements in single module systems

hpe1437\_read - reads scaled 32-bit float data from FIFO

$\mbox{hpe}1437\_\mbox{read}64$  - reads scaled  $64\mbox{-bit}$  float data from FIFO, specifically for VEE applications

hpe1437\_read\_raw - - reads raw data from FIFO

hpe1437\_reset - places the module in a known state

hpe1437 revision query - returns strings that identify the date of the firmware revision

hpe1437\_self\_test - performs a self-test on the module and returns the result

hpe1437\_status\_get - retreives module's status register information

E1437A User's Guide

Functions Listed alphabetically

hpe1437\_trigger\_adclevel - specifies the threshold for the ADC trigger

hpe1437\_trigger\_adclevel\_get - gets the ADC trigger threshold

hpe1437\_trigger\_delay - specifies a pre- or post-trigger delay time

hpe1437\_trigger\_delay\_get - gets the trigger delay time

$hpe1437\_trigger\_delay\_actual\_get$  - gets a representation of the phase value of the LO at the trigger point

hpe1437\_trigger\_gen - determines whether a module can generate a trigger

hpe1437\_trigger\_gen\_get - gets the trigger generation status

$hpe1437\_trigger\_maglevel$  - specifies the threshold for a magnitude trigger

$hpe 1437\_trigger\_maglevel\_get-gets\ magnitude\ trigger\ threshold$

$\label{prop:linear} \verb| hpe1437_trigger_phase_actual_get - gets the actual trigger phase from the most recent trigger event$

hpe1437\_trigger\_phase\_capture - Allows LO phase capture in frequency-synchronized, multi-module zoom measurements.

$hpe 1437\_trigger\_setup - sets \ all \ parameters \ associated \ with \ triggering \ the \ beginning \ of \ data \ collection$

hpe1437\_trigger\_slope - selects a positive or negative trigger

hpe1437\_trigger\_slope\_get - gets trigger slope

hpe1437\_trigger\_type - determines the trigger type

hpe1437\_trigger\_type\_get - gets trigger type

hpe1437\_wait - facilitates the synchronization and control of multi-module systems

# VXI plug&play Programming Reference

# hpe1437\_attrib\_get

Allows direct access to the I/O library functions.

VXIplug&play Syntax

#include "hpe1437.h"

ViStatus hpe1437 attrib get(ViSession id, ViInt16 attrib, ViPint32 value);

**Description**

**hpe1437\_attrib\_get** is used primarily to manage the use of interrupts. Since interrupts are a shared resource across all modules using the VXI interface, it is not possible for the E1437 library, which governs single modules, to provide the functions to properly manage interrupts.

This function is used to access either the I/O library handle or the mapped I/O base address of the module. You should refer to the appropriate VISA or SICL documentation for descriptions of the I/O library functions.

**Parameters**

id is the VXI instrument session pointer returned by the hpe1437\_init function.

attrib designates the type of attribute to return. HPE1437\_IO\_HANDLE accesses the I/O library handle. HPE1437\_IO\_ADDRESS points to the mapped I/O base address of the module. HPE1437\_RM\_HANDLE accesses the I/O library handle of the default resource manager. HPE1437\_DATA\_REGISTER points to the mapped address of the E1437 data register. One or both of these parameters are used when calling I/O library functions directly.

${\it value}$  is the value of the requested attribute. For a VTL/VISA I/O library the value of the handle attribute corresponds to the vi parameter used by the majority of the I/O functions. For the SICL I/O library the handle is equivalent to the session parameter used by the majority of the I/O functions. In the case of SICL the long handle value should be cast to a short in order to be type compatible with the SICL session. The address attribute points to the base of the mapped I/O address space, regardless of which underlying I/O library is used.

Effect on Active Measurement This command does not abort any measurement in progress.

See Also

hpe1437 init, hpe1437 interrupt setup

# hpe1437\_clock\_setup

**hpe1437\_clock\_setup** sets all timing parameters. This description also includes information on the following functions which set or query the timing parameters individually:

hpe1437\_clock\_dsp selects the clock used to drive the decimation/zoom section.

hpe1437\_clock\_dsp\_get gets the current decimation clock source

hpe1437\_clock\_fs provides the frequency of an external sample clock.

hpe1437\_clock\_fs\_get gets the current external sample clock frequency

hpe1437\_clock\_master determines whether a module shares its ADC clock.

hpe1437\_clock\_master\_get gets the module's clock master state

hpe1437\_clock\_multi\_sync specifies whether the module uses a shared clock and sync

hpe1437\_clock\_multi\_sync\_get gets the module's current shared clock and sync state

**hpe1437 clock source** selects the source of the ADC clock

hpe1437\_clock\_source\_get gets the ADC clock source

#### VXIplug&play Syntax

#### #include "hpe1437.h"

ViStatus hpe1437\_clock\_setup(ViSession *id*, ViInt16 *sync*, ViInt16 *source*, ViInt16 *dsp*, ViInt16 *master*, ViReal64 *fs*);

ViStatus hpe1437\_clock\_dsp(ViSession id, ViInt16 dsp);

ViStatus hpe1437\_clock\_dsp\_get(ViSession id, ViPInt16 dspPtr);

ViStatus **hpe1437\_clock\_fs**(ViSession *id*, ViReal64*fs*);

ViStatus hpe1437 clock fs get(ViSession id, ViPReal64 fsPtr);

ViStatus hpe1437\_clock\_master(ViSession id, ViInt16 master);

ViStatus hpe1437\_clock\_master\_get(ViSession id, ViPInt16 masterPtr);

ViStatus hpe1437\_clock\_multi\_sync(ViSession id, ViInt16 sync);

ViStatus hpe1437\_clock\_multi\_sync\_get(ViSession id, ViPInt16 syncPtr);

ViStatus hpe1437\_clock\_source(ViSession id, ViInt16 source);

ViStatus hpe1437\_clock\_source\_get(ViSession id, ViPInt16 sourcePtr);

#### **Description**

hpe1437\_clock\_setup is used to configure all timing parameters used for sampling (ADC clock) and decimation/zoom (DSP clock). This function, as well as the other hpe1437\_clock\_ functions covered in this description, is used to select the source and distribution of clocking and synchronization signals used by the E1437 module. The primary clock signal used by the module is the ADC clock, for which the rising edges indicate the time for each sample of the analog-to-digital converter. Another clock signal is the DSP clock, which drives the digital signal processing and memory sections of the module. Normally the DSP clock is the same as the ADC clock, and data is transferred synchronously from the ADC to the DSP portion of the module. However, in certain situations the two clocks may be independent, requiring asynchronous data transfers from the ADC to the DSP. The remaining hpe1437\_clock\_ functions listed above set or query the parameters individually.

#### **Parameters**

id is the VXI instrument session pointer returned by the hpe1437 init function.

<code>sync</code> is used to specify whether the module uses a shared ADC clock and SYNC signal. If the <code>sync</code> parameter is set to <code>HPE1437\_OFF</code> the ADC clock and SYNC are generated locally. If <code>sync</code> is set to <code>HPE1437\_REAR</code> the module uses the shared ADC clock and SYNC signals which are distributed on the VXI backplane using the ECL trigger lines. If <code>sync</code> is set to <code>HPE1437\_FRONT</code> the module uses the shared clock and SYNC provided on the front panel distribution connectors. Modules in multi-module systems must all have the same <code>sync</code> parameter setting.

**syncPtr** contains the current value of the *sync* parameter.

**source** selects the clock source that is used to drive the analog to digital converter (ADC) for single module operation or when a module is used as the master ADC clock source for a multi-module system. When set to **HPE1437\_20000KHZ** the clock source is the internal 20 MHz oscillator. When set to **HPE1437\_20480KHZ** the clock source is the internal 20.48 MHz oscillator. **HPE1437\_EXTERNAL** selects the TTL, ECL, or sine signal on the external BNC front panel clock input connector. When using an external clock the *fs* parameter is used to provide the module with the frequency of the external clock. **HPE1437\_EXT\_PLL\_REF** takes a 10 MHz reference from another instrument on the external BNC front panel clock input connector and uses a PLL to convert it to a 20 MHz reference. In multi-module systems the *source* parameter is ignored for all but the master module.

**sourcePtr** contains the current value of the *source* parameter.

dsp selects the clock used to drive the decimation/zoom section within the E1437. Normally, the DSP clock should be coupled to the ADC clock whenever possible since the spurious performance specification is degraded when the clocks are independent. However, when a slow or intermittent ADC clock results in greater than 1 μs between clock edges, the DSP clock must be generated from the internal oscillator to avoid data loss in the dynamic RAM. Setting this parameter to HPE1437\_ADC forces the DSP clock to be driven by the ADC clock. HPE1437\_OSCILLATOR will cause the DSP clock to be the internally generated 20.48 MHz oscillator. Note that the computed results will be the same in either case.

**dspPtr** contains the current value of the dsp parameter.

master determines whether an E1437 makes its local ADC clock available to other modules as a shared clock. Multi-module synchronization requires one and only one of the modules to be identified as the master, that is, the source of the shared ADC clock. Setting this parameter to HPE1437\_ON when  $sync = HPE1437_FRONT$  causes the E1437 to drive the front panel ADC clock; or if  $sync = HPE1437_REAR$  causes the module to use its ADC clock to drive the VXI backplane in the mainframe in which it resides. HPE1437\_OFF means that the E1437 is driving neither the front panel nor the backplane and is the correct variable to use for all non-master modules in a multi-module system. Setting this parameter to HPE1437\_BUFFER allows the ADC clock and SYNC lines from the module's front panel connectors to drive the backplane of a mainframe not containing the master. Only one module per mainframe may be set to ON or to BUFFER. In multi-module and multi-mainframe systems only one module may be set to ON within the entire system. In multi-mainframe systems using backplane clock and sync distribution only one module per any mainframe not containing the master may be set to BUFFER.

*masterPtr* contains the current value of the *master* parameter.

fs provides the module with the frequency of an external sample clock (from >0 to 20600000) connected to the Ext Clk TTL connector. When using an external clock or when a module is a non-master in a multi-module group, the frequency of the ADC clock is unknown by the module. It is the responsibility of the programmer to provide the correct frequency so that library functions dependent on fs will operate properly. This value has no effect if the module is set up to use the internal ADC clock.

*fsPtr* contains the current value of the sample clock frequency. If the E1437 is set to the internal ADC clock, the value of that clock frequency is returned. If the E1437 is set to the external clock, the last value entered via the **hpe1437\_clock\_fs** function is returned.

#### **Comments**

For more details on the interaction among *source*, *master*, and *sync* with multiple modules and multiple mainframes see Managing multiple modules.

The *master*, *sync*, *source*, and *dsp* parameters are interdependent with legitimate combinations being as follows (along with the resultant DSP clock rates):

| MASTER       | SYNC    | SOURCE  | DSP     | DSP CLOCK RATE  |

|--------------|---------|---------|---------|-----------------|

|              | ======= |         | ======= |                 |

| N/A          | OFF     | 20.x    | N/A     | Internal Source |

| N/A          | OFF     | EXT     | ADC     | External Source |

| N/A          | OFF     | EXT     | OSC     | 20.48           |

| N/A          | OFF     | EXT_PLL | N/A     | 20              |

| OFF   BUFFER | FRONT   | N/A     | ADC     | Master ADC      |

| OFF   BUFFER | FRONT   | N/A     | OSC     | 20.48           |

| OFF          | REAR    | N/A     | ADC     | Master ADC      |

| OFF          | REAR    | N/A     | OSC     | 20.48           |

| ON           | FRONT   | 20.x    | N/A     | Internal Source |

| ON           | FRONT   | EXT     | ADC     | External Source |

| ON           | FRONT   | EXT     | OSC     | 20.48           |

| ON           | FRONT   | EXT_PLL | N/A     | 20              |

| ON           | REAR    | 20.x    | N/A     | Internal Source |

| ON           | REAR    | EXT     | ADC     | External Source |

| ON           | REAR    | EXT     | OSC     | 20.48           |

| ON           | REAR    | EXT_PLL | N/A     | 20              |

| BUFFER       | REAR    | N/A     | ADC     | Master ADC      |

| BUFFER       | REAR    | N/A     | OSC     | 20.48           |

|              |         |         |         |                 |

The maximum rate at which data may be transferred to memory is determined by the DSP clock rate: Max bytes/s =  $4 \times$  DSP clock rate. In continuous mode the maximum rate is limited to  $(4 \times$  DSP clock rate)  $\div$  2. However, you may successfully perform this type of measurement by adding a level of decimation to reduce the sample rate.

If fs>20480000 then dsp must=ADC.

#### Example

The program **multichan.exe** described in Example Programs provides an example of how to correctly set up a multi-module system with synchronous clocks.

## **Reset Values**

sync OFF source 20480KHZ dsp ADC master OFF fs 20.48 e6

# Effect on Active Measurement

Commands in this group, other than those ending in \_get and HPE1437\_clock\_fs, abort any measurement in progress.

See Also

hpe1437\_init, hpe1437\_filter\_setup, hpe1437\_data\_

# hpe1437\_close

Closes the module's software connection.

VXIplug&play Syntax #include "hpe1437.h"

ViStatus hpe1437\_close(ViSession id);

**Description** hpe1437 close terminates the software connection to the module, deallocates system

resources, and places the module in the IDLE state. After this function has been executed the specified id identifier is no longer a valid parameter for function calls.

**Parameters** *id* is the VXI instrument session pointer returned by the **hpe1437\_init** function.

Effect on Active Measurement

This command does not abort any measurement in progress.

See Also hpe1437\_init

# hpe1437\_data\_memsize\_get

Returns the module's memory size in megabytes.

VXIplug&play Syntax #include "hpe1437.h"

ViStatus hpe1437\_data\_memsize\_get(ViSession id, ViPInt16 memSizePtr);

**Description** This command allows you to determine whether your module contains standard

memory of 8 Mbytes or a larger memory option.

**Parameters** *id* is the VXI instrument session pointer returned by the **hpe1437\_init** function.

memSizePtr contains the memory size in number of Megabytes.

Effect on Active Measurement This command does not abort any measurement in progress.

See Also hpe1437\_init, hpe1437\_data\_blocksize

# hpe1437\_data\_scale\_get

Gets data scale factor.

VXIplug&play Syntax #include "hpe1437.h"

ViStatus hpe1437\_data\_scale\_get(ViSession id, ViPReal64 scalePtr);

**Description** hpe1437 data scale get calculates the correct scale factor for raw data using the

current data resolution and range. The factor returned by this function is used to

multiply raw data to get data in volts.

**Parameters** *id* is the VXI instrument session pointer returned by the **hpe1437\_init** function.

scalePtr contains the calculated scale factor with which to scale raw data to volts.

If hpe1437\_input\_range\_auto is pending or in progress this command returns an

error.

Effect on Active Measurement

NOTE

This command does not abort any measurement in progress.

See Also hpe1437\_-, hpe1437\_read\_raw -

# hpe1437\_data\_setup

**hpe1437\_data\_setup** sets all format and data output flow parameters. This description also includes information on the following functions which set or query the format and flow parameters individually:

**hpe1437\_data\_append\_status** appends status information to a data block.

hpe1437\_data\_append\_status\_get gets the append status state

hpe1437\_data\_blocksize determines the size of the output data block.

hpe1437\_data\_blocksize\_get gets the output data block size

hpe1437\_data\_mode selects block mode or continuous mode.

hpe1437\_data\_mode\_get gets the data mode

**hpe1437\_data\_port** selects VME bus or local bus output port.

hpe1437\_data\_port\_get gets the output port designation

hpe1437\_data\_resolution selects 16 or 32 bits data resolution.

hpe1437\_data\_resolution\_get gets the data resolution

hpe1437\_data\_type selects real or complex output data.

hpe1437\_data\_type\_get gets output data type

#### VXI*plug&play* Syntax

#### #include "hpe1437.h"

ViStatus hpe1437\_data\_setup(ViSession id, ViInt16 dType, ViInt16 resolution,

ViInt16 mode, ViInt32 blocksize, ViInt16 appendStatus, ViInt16 port);

ViStatus hpe1437\_data\_append\_status(ViSession id, ViInt16 appendStatus);

ViStatus hpe1437\_data\_append\_status\_get(ViSession id, ViPInt16 appendStatusPtr);

ViStatus hpe1437\_data\_blocksize(ViSession id, ViInt32 blocksize);

ViStatus hpe1437\_data\_blocksize\_get(ViSession id, ViPint32 blocksizePtr);

ViStatus hpe1437\_data\_mode(ViSession id, ViInt16 mode);

ViStatus hpe1437\_data\_mode\_get(ViSession id, ViPInt16 modePtr);

ViStatus hpe1437\_data\_port(ViSession id, ViInt16 port);

ViStatus hpe1437\_data\_port\_get(ViSession id, ViPInt16 portPtr);