# **Service Guide**

# Agilent Technologies 89410A Vector Signal Analyzer

Part Number: 89410-90103 Supersedes: 89410-90065

> Printed in USA March 2002

© Copyright 2001-2002 Agilent Technologies Inc.

The information contained in this document is subject to change without notice.

Agilent Technologies makes no warranty of any kind with regard to this material, including but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

# **Safety Information**

The following safety notes are used throughout this manual. Familiarize yourself with each of the notes and it's meaning before operating this instrument.

WARNING: Warning denotes a hazard. It calls attention to a procedure which, if not correctly performed or adhered to, could result in injury or loss of life. Do not proceed beyond a warning note until the indicated conditions are fully understood and met.

**CAUTION:** Caution denotes a hazard. It calls attention to a procedure that, if not correctly performed or adhered to, could result in damage to or destruction of the instrument. Do not proceed beyond a caution sign until the indicated conditions are fully understood and met.

WARNING: This is a Safety Class 1 Product (provided with a protective earthing ground incorporated in the power cord). The mains plug shall only be inserted in a socket outlet provided with a protected earth contact. Any interruption of the protective conductor inside or outside of the product is likely to make the product dangerous. Intentional interruption is prohibited.

**WARNING:** These servicing instructions are for use by qualified personnel only. To avoid electrical shock, do not perform any servicing unless you are qualified to do so.

WARNING: The power cord is connected to internal capacitors that may remain live for 5 seconds after disconnecting the plug from it's power supply.

# Warranty

This Agilent Technologies instrument product is warranted against defects in material and workmanship for a period of three years from date of shipment. During the warranty period, Agilent Technologies will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to a service facility designated by Agilent Technologies. Buyer shall prepay shipping charges to Agilent Technologies and Agilent Technologies shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Agilent Technologies from another country.

Agilent Technologies warrants that its software and firmware designated by Agilent Technologies for use with an instrument will execute its programming instructions when properly installed on that instrument. Agilent Technologies does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error-free.

### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. AGILENT TECHNOLOGIES SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. AGILENT TECHNOLOGIES SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### In this manual...

#### Chapter 1 Troubleshooting the Analyzer

Provides step-by-step instructions for isolating most failures to the faulty assembly

#### Chapter 2 Adjusting the Analyzer

Provides step-by-step instructions for adjusting the analyzer

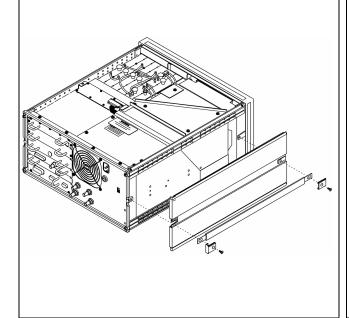

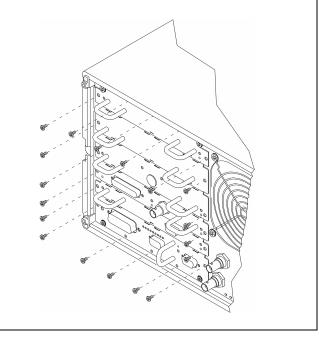

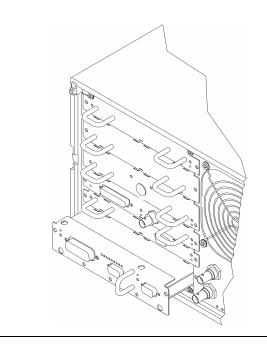

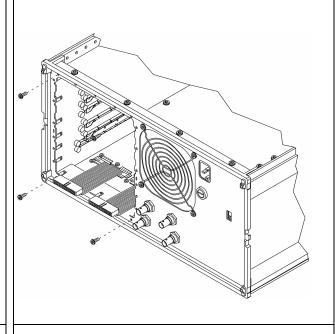

#### Chapter 3 Replacing Assemblies

Provides step-by-step instructions to follow before and after replacing an assembly. This chapter also provides step-by-step instructions for disassembling the analyzer

#### Chapter 4 Replaceable Parts

Provides ordering information and lists the replaceable parts

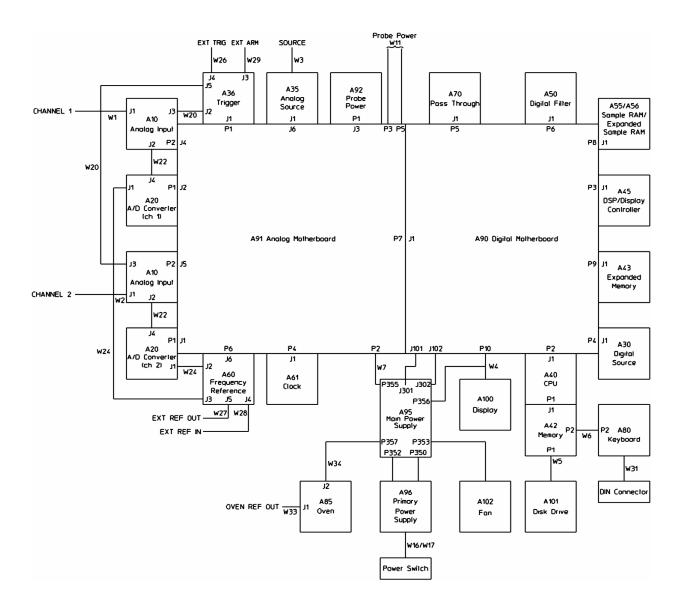

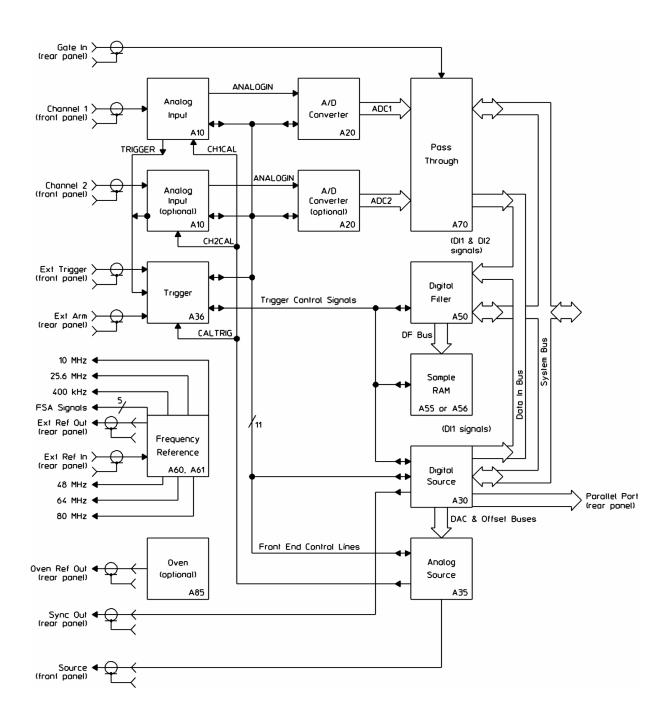

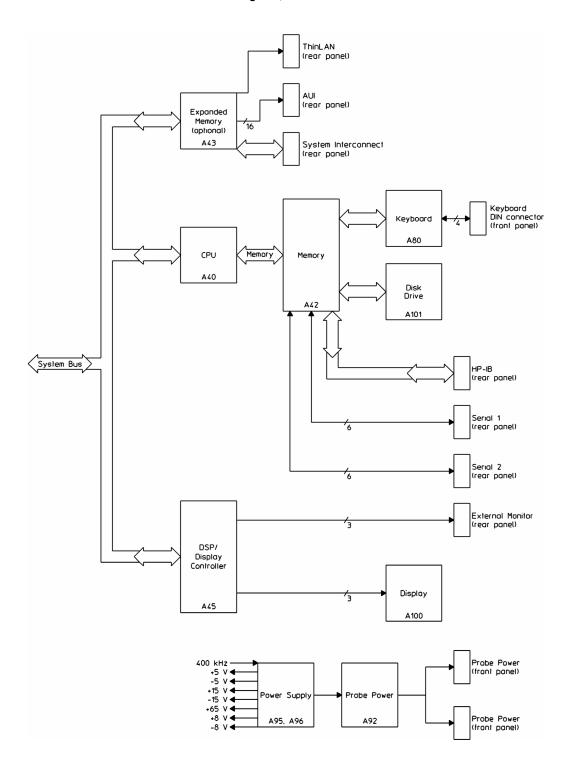

#### Chapter 5 Circuit Descriptions

Provides the overall instrument description and individual assembly description

### Chapter 6 Voltages and Signals

Shows where the signals and voltages are used in the analyzer and describes each signal

#### Chapter 7 Internal Test Descriptions

Describes the power-on test, calibration routine, fault log messages, and self tests

#### Chapter 8 Backdating

Provides information necessary to modify this manual for instruments that differ from those currently being produced

#### Chapter 9 Quick Reference

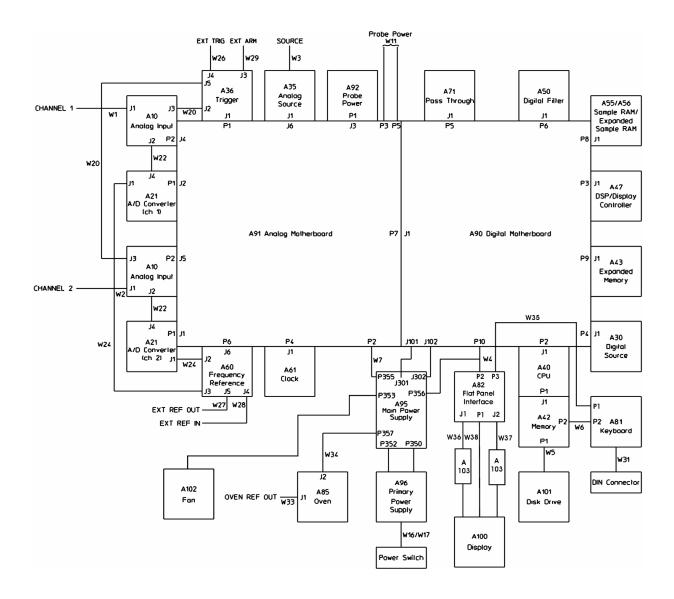

Provides all the block diagrams and the "A90/A91 Motherboard Voltages" table

### **Notation Conventions**

Before you use this book, it is important to understand the types of keys on the front panel of the analyzer and how they are denoted in this book.

#### **Hardkeys**

Hardkeys are front-panel buttons whose functions are always the same. Hardkeys have a label printed directly on the key. In this book, they are printed like this: [Hardkey].

#### Softkeys

• Softkeys are keys whose functions change with the analyzer's current menu selection. A softkey's function is indicated by a video label to the left of the key (at the edge of the analyzer's screen). In this book, softkeys are printed like this: [softkey].

#### **Toggle Softkeys**

Some softkeys toggle through multiple settings for a parameter. Toggle softkeys have a word highlighted (of a different color) in their label. Repeated presses of a toggle softkey changes which word is highlighted with each press of the softkey. In this book, toggle softkey presses are shown with the requested toggle state in bold type as follows:

"Press [key name on]" means "press the softkey [key name] until the selection on is active."

#### **Shift Functions**

• In addition to their normal labels, keys with blue lettering also have a shift function. This is similar to shift keys on a pocket calculator or the shift function on a typewriter or computer keyboard. Using a shift function is a two-step process. First, press the blue [Shift] key (at this point, the message "shift" appears on the display). Then press the key with the shift function you want to enable. Shift function are printed as two key presses, like this:

[Shift] [Shift Function]

#### **Numeric Entries**

Numeric values may be entered by using the numeric keys in the lower right hand ENTRY area of the analyzer front panel. In this book, values which are to be entered from these keys are indicted only as numerals in the text, like this:

Press 50, [enter]

#### **Ghosted Softkeys**

• A softkey label may be shown in the menu when it is inactive. This occurs when a softkey function is not appropriate for a particular measurement or not available with the current analyzer configuration. To show that a softkey function is not available, the analyzer "ghosts" the inactive softkey label. A ghosted softkey appears less bright than a normal softkey. Settings/values may be changed while they are inactive. If this occurs, the new settings are effective when the configuration changes such that the softkey function becomes active.

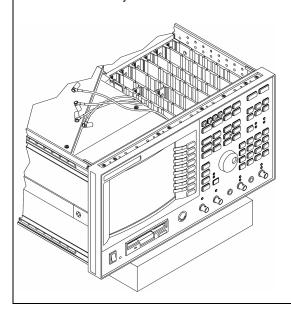

# The Agilent 89410A at a Glance

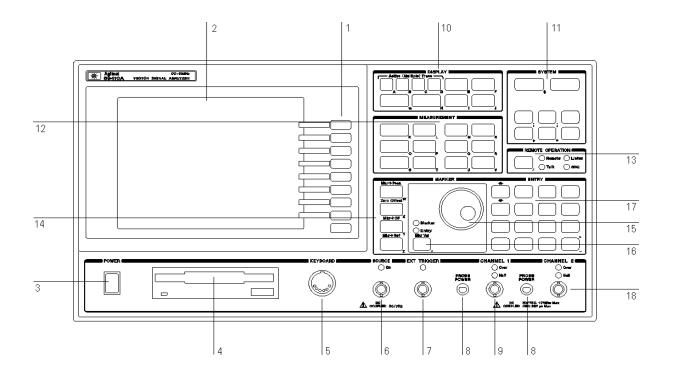

## **Agilent 89410A Front Panel**

- 1-A softkey's function changes as different menus are displayed. Its current function is determined by the video label to its left, on the analyzer's screen.

- **2-**The analyzer's screen is divided into two main areas. The menu area, a narrow column at the screen's right edge, displays softkey labels. The data area, the remaining portion of the screen, displays traces and other data

- **3**-The POWER switch turns the analyzer on and off.

- **4**-Use a 3.5-inch flexible disk (DS,HD) in this disk drive to save your work.

- **5**-The KEYBOARD connector allows you to attach an optional keyboard to the analyzer. The keyboard is most useful for writing and editing Instrument BASIC programs.

- **6-** The SOURCE connector routes the analyzer's source output to your DUT. Output impedance is selectable: 50 ohms or 75 ohms.

- 7-The EXT TRIGGER connector lets you provide an external trigger for the analyzer.

- **8-**The PROBE POWER connectors provide power for various Agilent active probes.

- **9-**The CHANNEL 1 input connector routes your test signal or DUT output to the analyzer's receiver. Input impedance is selectable: 50 ohms, 75 ohms, or 1 megohm.

- 10-Use the DISPLAY hardkeys and their menus to select and manipulate trace data and to select display options for that data.

- 11-Use the SYSTEM hardkeys and their menus to control various system functions (online help, plotting, presetting, and so on).

- 12-Use the MEASUREMENT hardkeys and their menus to control the analyzer's receiver and source, and to specify other measurement parameters.

- **13**-The REMOTE OPERATION hardkey and LED indicators allow you to set up and monitor the activity of remote devices.

- **14-**Use the MARKER hardkeys and their menus to control marker positioning and marker functions.

- **15**-The knob's primary purpose is to move a marker along the trace. But you can also use it to change values during numeric entry, move a cursor during text entry, or select a hypertext link in help topics.

**16-**Use the Marker/Entry key to determine the knob's function. With the Marker indicator illuminated, the knob moves a marker along the trace. With the Entry indicator illuminated, the knob changes numeric entry values.

17-Use the ENTRY hardkeys to change the value of numeric parameters or to enter numeric characters in text strings.

**18**-The optional CHANNEL 2 input connector routes your test signal or DUT output to the analyzer's receiver. Input impedance is selectable: 50 ohms, 75 ohms, or 1 megohm. For easy of upgrading, the CHANNEL 2 BNC connector is installed even if option AY7 (second input channel) is not installed.

For more details on the Agilent 89410A front panel, display the online help topic "Front Panel."

### Before applying power

Verify that the product is set to match the available line voltage, the correct fuse is installed, and all safety precautions are taken. Note the instrument's external markings described in "Safety symbols and instrument markings" on page x.

#### Ground the instrument

To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

#### **Fuses**

Use only fuses with the required rated current, voltage, and specified type (normal blow, time delay). Do not use repaired fuses or short-circuited fuse holders. To do so could cause a shock or fire hazard.

## Safety symbols and instrument markings

Symbols and markings in manuals and on instruments alert you to potential risks, provide information about conditions, and comply with international regulations. Table 1 defines the symbols and markings you may find in a manual or on an instrument.

Table 1

Safety symbols and instrument markings

# Safety symbols Warning: risk of electric shock. Warning: hot surface Caution: refer to accompanying documents. Laser radiation symbol: marked on products that have a laser output. Alternating current. Both direct and alternating current. Three-phase alternating current. Earth (ground) terminal Protective earth (ground) terminal Frame or chassis terminal Terminal is at earth potential. Used for measurement and control circuits designed to be operated with one terminal at earth potential. Terminal for neutral conductor on permanently installed equipment. Terminal for line conductor on permanently installed equipment. Standby (supply); units with this symbol are not completely disconnected from ac mains when this switch is off. To completely disconnect the unit from ac mains, either disconnect the power cord, or have a qualified electrician install an external switch. Instrument markings The CE mark is a registered trademark of the European Community. If it is Œ accompanied by a year, it indicates the year the design was proven.

Table 1

Safety symbols and instrument markings (continued)

#### Safety symbols

The CSA mark is a registered trademark of the Canadian Standards Association.

The C-tick mark is a registered trademark of the Spectrum Management Agency of Australia. This signifies compliance with the Australian EMC Framework regulations under the terms of the Radio Communications Act of 1992.

1SM 1-A

This text indicates that the instrument is an Industrial Scientific and Medical Group 1 Class A product (CISPER 11, Clause 4).

# **Service and Support**

Any adjustment, maintenance, or repair of this product must be performed by qualified personnel. Contact your customer engineer through your local Agilent Technologies Service Center. You can find a list of local service representatives on the Web at:

http://www.agilent.com/ services/English/index.html

If you do not have access to the Internet, one of these centers can direct you to your nearest representative.

Table 2

Telephone numbers for Agilent Call Centers

| United States:          | Test and Measurement Call Center |  |  |

|-------------------------|----------------------------------|--|--|

|                         | (800) 452 4844 (toll-free in US) |  |  |

| Canada:                 | (905) 206 4725                   |  |  |

| Europe:                 | (31 20) 547 9900                 |  |  |

| Japan:                  | Measurement Assistance Center    |  |  |

|                         | (81) 426 56 7832                 |  |  |

|                         | (81) 426 56 7840 (FAX)           |  |  |

| Latin America:          | (305) 267 4245                   |  |  |

|                         | (305) 267 4288 (FAX)             |  |  |

| Australia/ New Zealand: | 1 800 629 485 (Australia)        |  |  |

|                         | 0800 738 378 (New Zealand))      |  |  |

| Asia-Pacific:           | (852) 2599 7777                  |  |  |

|                         | (852) 2506 9285 (FAX)            |  |  |

# Contents

| 1. | Troubleshooting the Analyzer                              |       |

|----|-----------------------------------------------------------|-------|

|    | How to troubleshoot the analyzer                          | 1-8   |

|    | To perform initial verification                           | .1-10 |

|    | To troubleshoot the power supply                          | .1-15 |

|    | To troubleshoot display failures                          |       |

|    | To perform self tests                                     |       |

|    | To troubleshoot self-test lockup failures                 | .1-48 |

|    | To troubleshoot intermittent failures                     |       |

|    | To troubleshoot performance test failures                 |       |

|    | To troubleshoot front-end control failures                |       |

|    | To troubleshoot source and calibrator out failures        |       |

|    | To troubleshoot input and ADC failures                    |       |

|    | To troubleshoot two channel analyzer failures             |       |

|    | To troubleshoot auto-range failures                       |       |

|    | To troubleshoot trigger failures.                         |       |

|    | To troubleshoot disk drive failures                       |       |

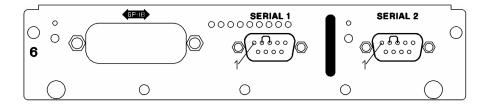

|    | To troubleshoot serial port failures                      |       |

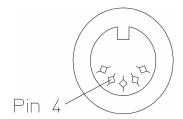

|    | To troubleshoot DIN connector failures                    |       |

|    | To troubleshoot memory battery failures                   |       |

|    | To troubleshoot sync out and parallel port failures       |       |

|    | To troubleshoot system interconnect and LAN port failures |       |

|    | To broubleshoot system interconnect and Lanv portrainales | .1 50 |

| 2. | Adjusting the Analyzer                                    |       |

| 4. | To adjust oven shutdown                                   | 9.7   |

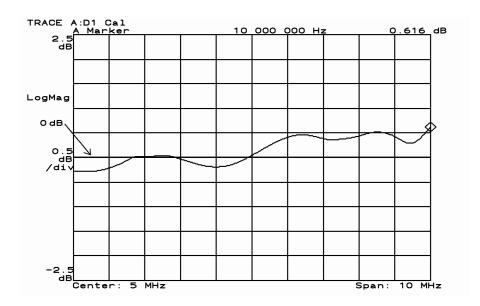

|    | To adjust oven shutdown  To adjust input flatness         |       |

|    | To adjust input capacitance                               |       |

|    | To adjust input capacitance.                              |       |

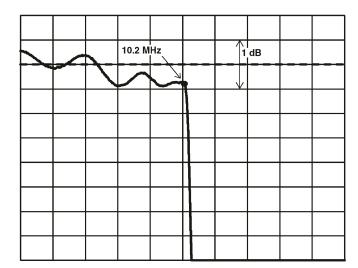

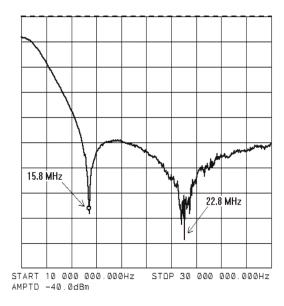

|    | To adjust anti-alias filter                               |       |

|    | To adjust ADC.                                            |       |

|    | ·                                                         |       |

|    | To adjust 10 MHz low pass filter                          |       |

|    | To adjust auto-range detect level                         |       |

|    | To adjust reference oscillator                            |       |

|    | To adjust oven frequency                                  |       |

|    | To adjust calibrator                                      | .2-37 |

| _  |                                                           |       |

| 3. |                                                           |       |

|    | What to do before replacing the analog source             |       |

|    | What to do after replacing an assembly                    |       |

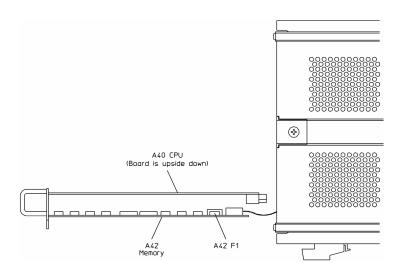

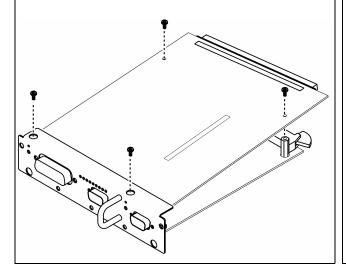

|    | To remove CPU and memory                                  |       |

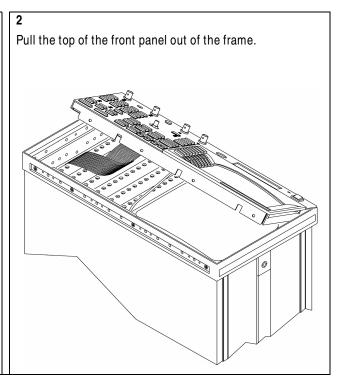

|    | To remove front panel                                     |       |

|    | To remove the Flat Panel Display                          |       |

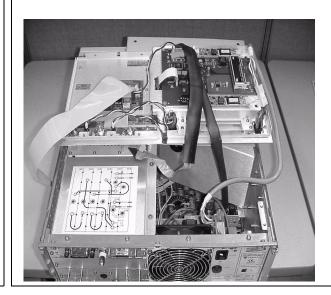

|    | To place the A82 in the test position                     |       |

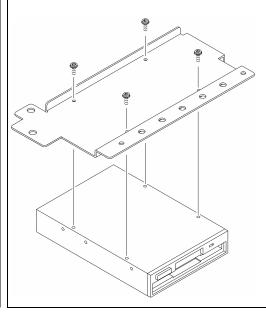

|    | To remove disk drive                                      |       |

|    | To remove main power supply                               |       |

|    | To remove analog motherboard                              |       |

|    | To remove rear panel                                      |       |

|    | To remove digital motherboard                             |       |

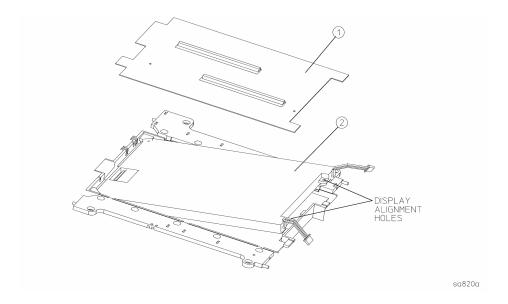

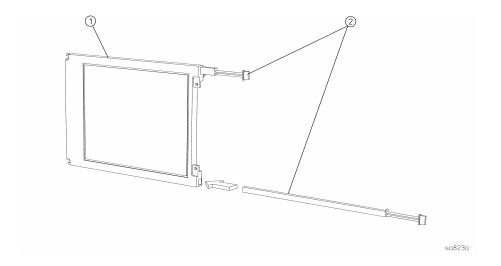

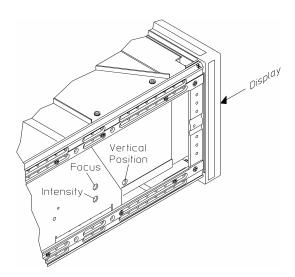

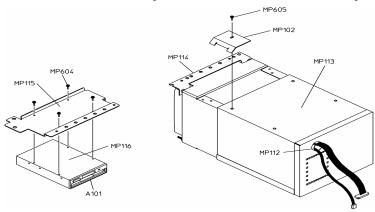

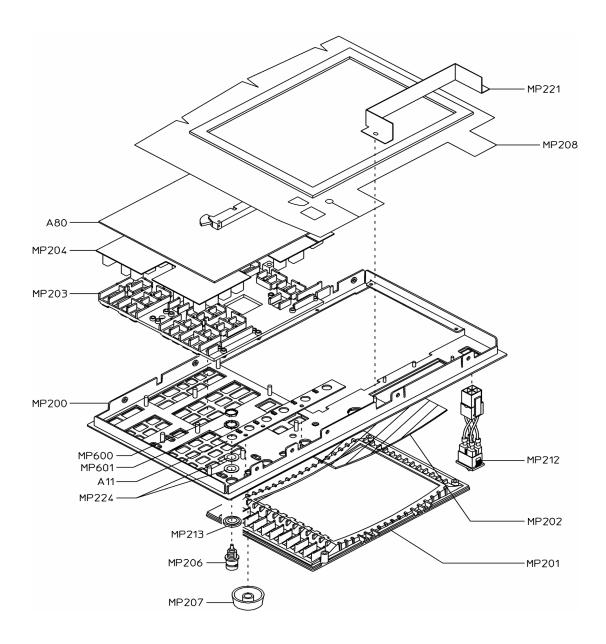

|    | A100 Display, Backlights, and Filter                      | 3-26  |

# **Contents**

| <b>4.</b> | Replaceable Parts                      |                |

|-----------|----------------------------------------|----------------|

|           | Ordering Information                   | 4-4            |

|           | Assemblies                             | 4-7            |

|           | Cables                                 |                |

|           | Instrument Covers and Handles.         |                |

|           | Front Panel Parts                      |                |

|           | Rear Panel Parts                       |                |

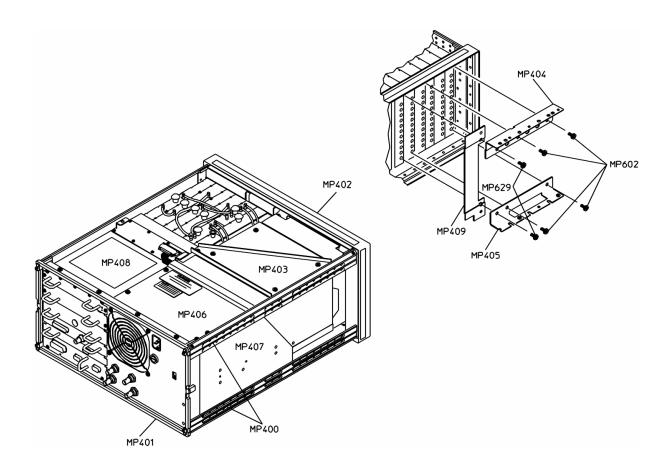

|           | Chassis Parts                          |                |

|           | Card Nest Parts                        |                |

|           | Screws, Washers, and Nuts.             |                |

|           | Miscellaneous Parts.                   |                |

|           |                                        |                |

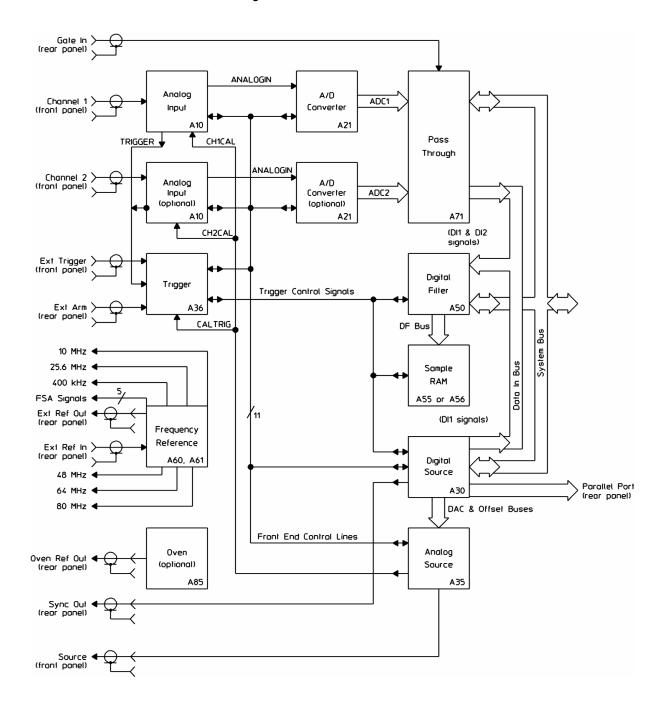

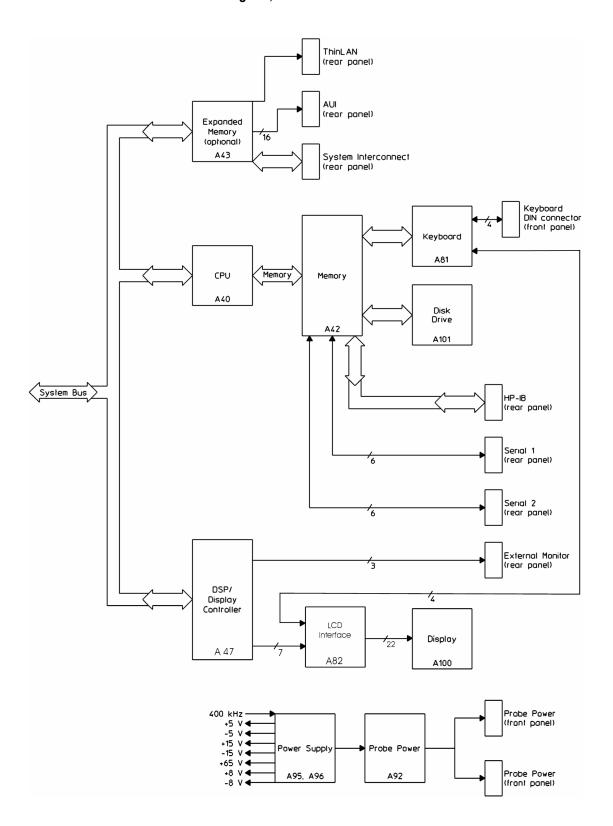

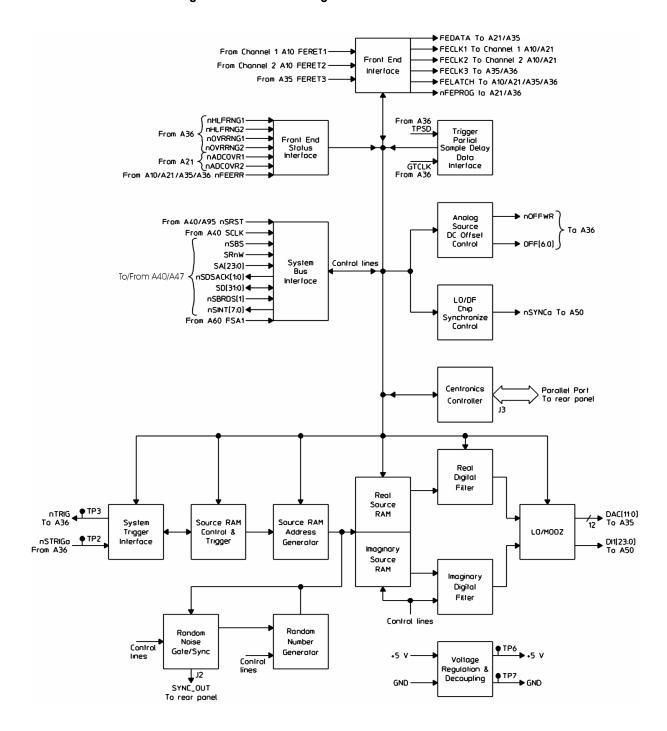

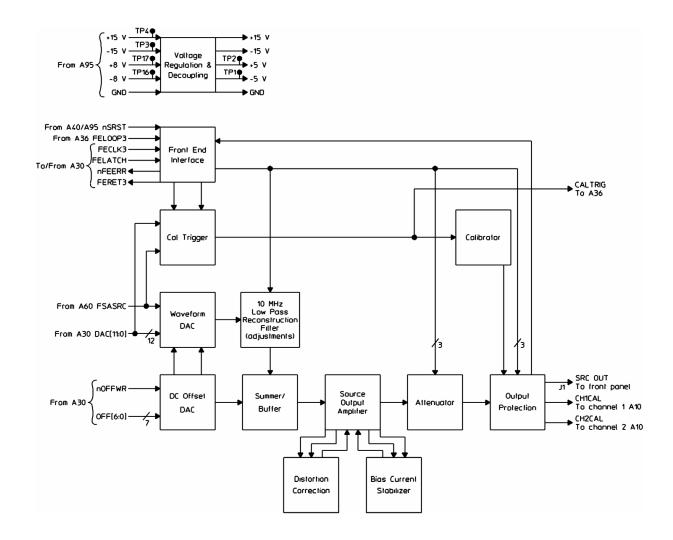

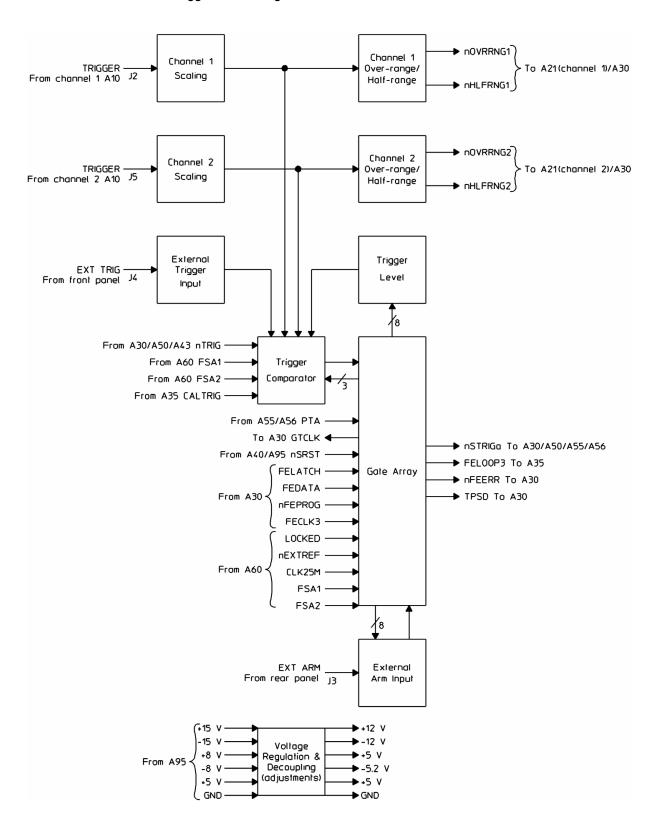

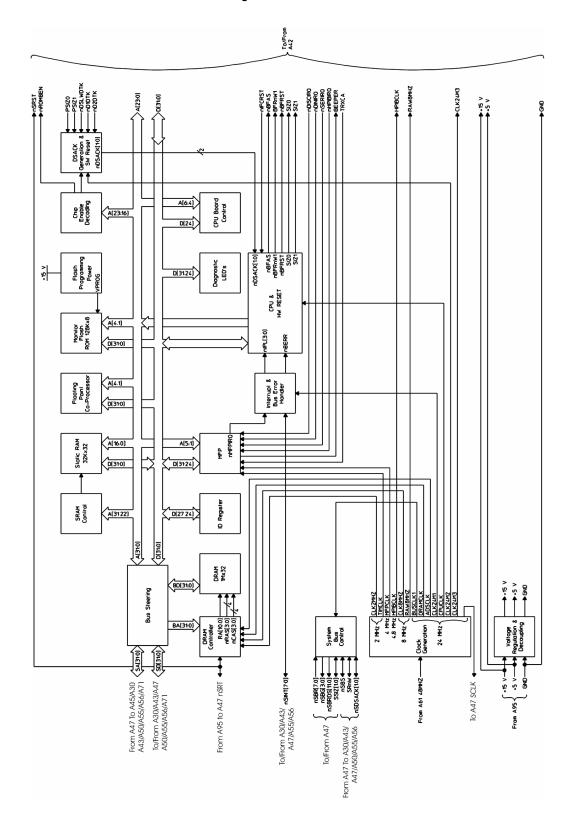

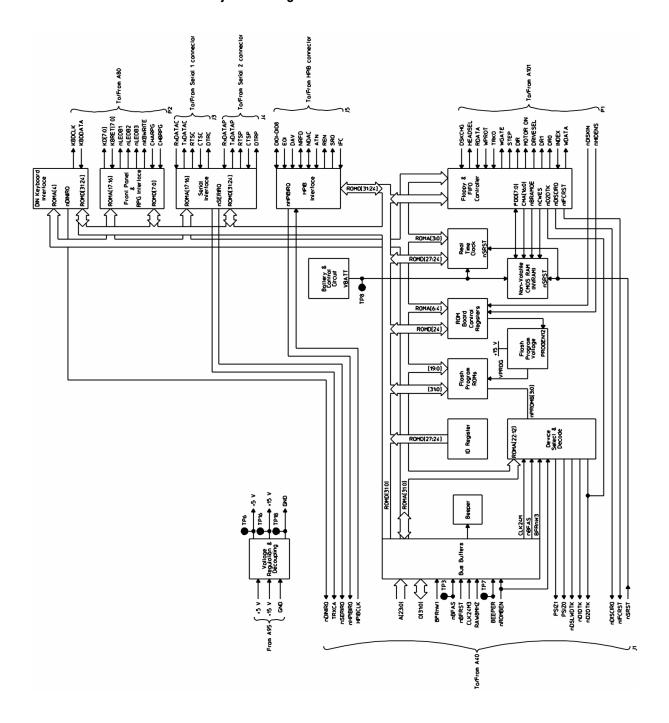

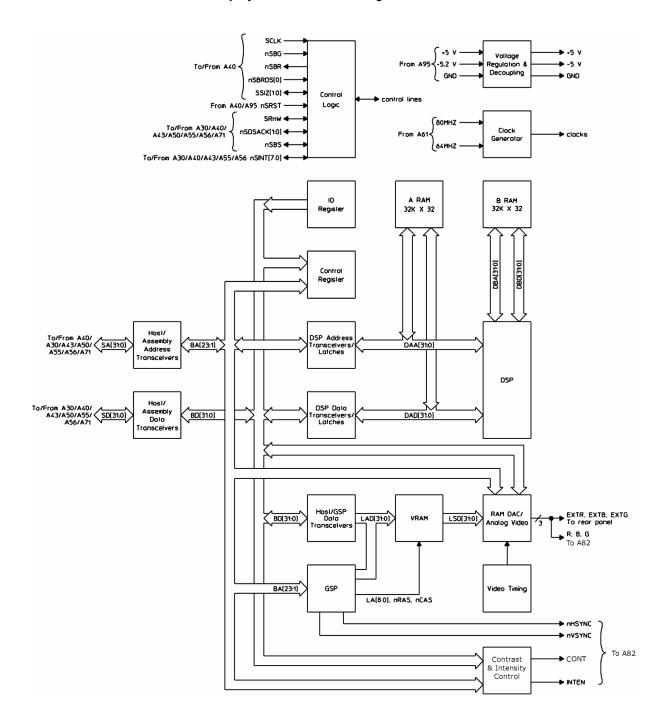

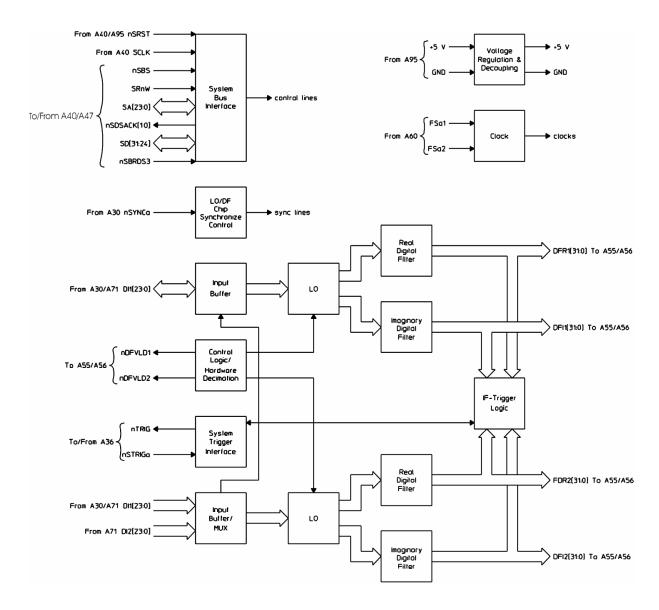

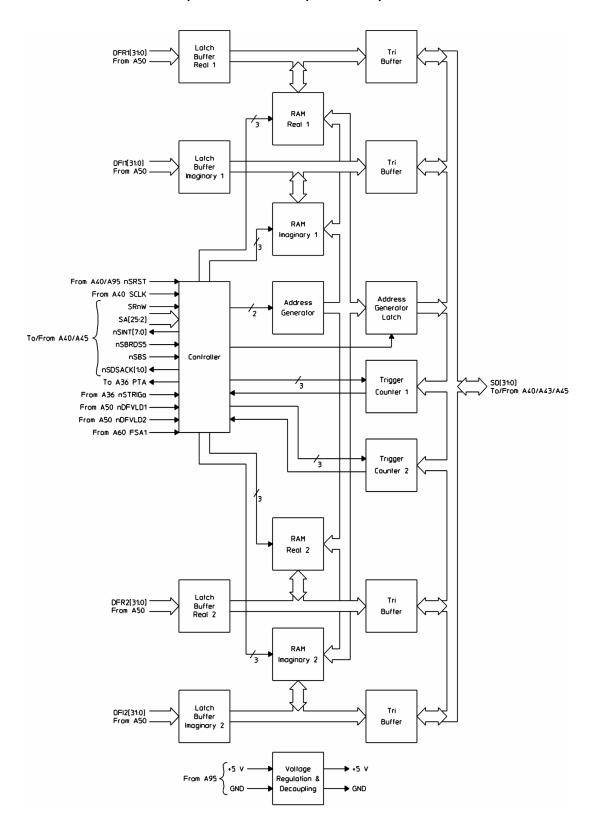

| <b>5.</b> | Circuit Descriptions                   |                |

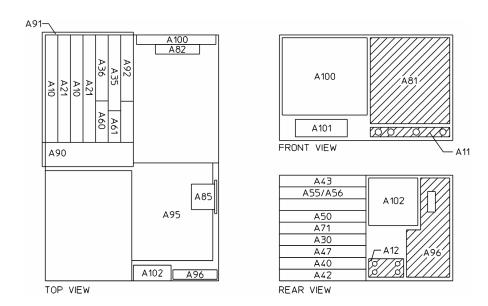

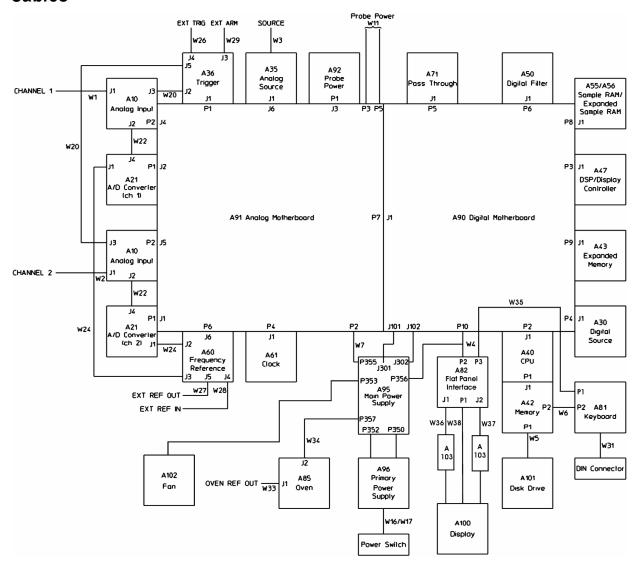

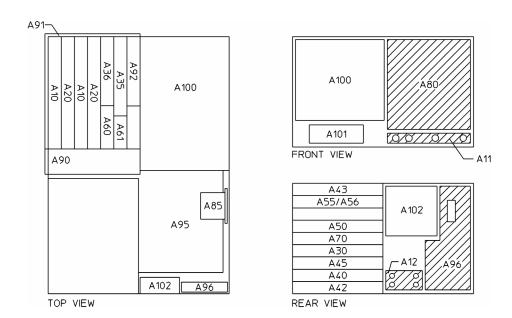

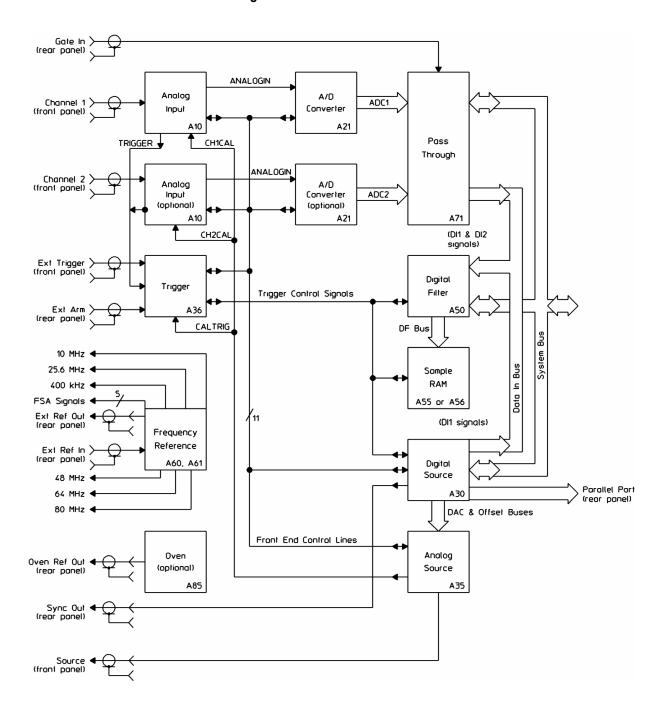

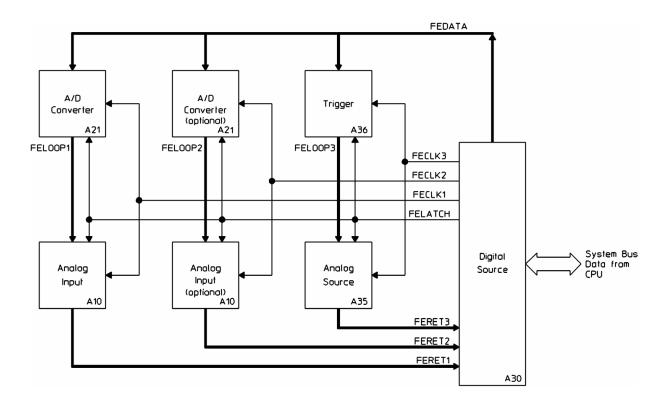

|           | Overall Instrument Description         | 5-4            |

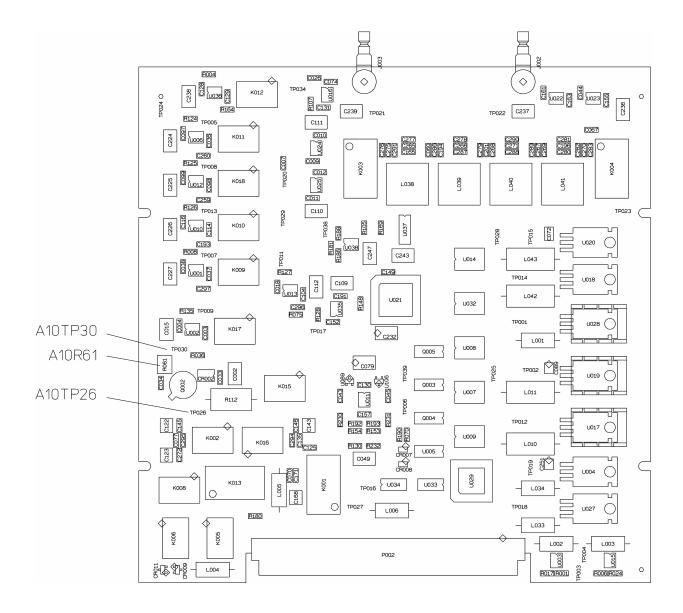

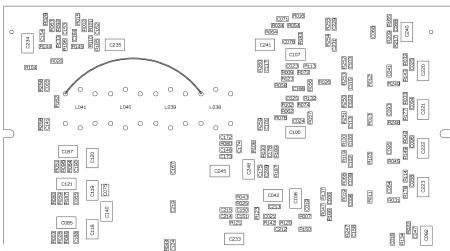

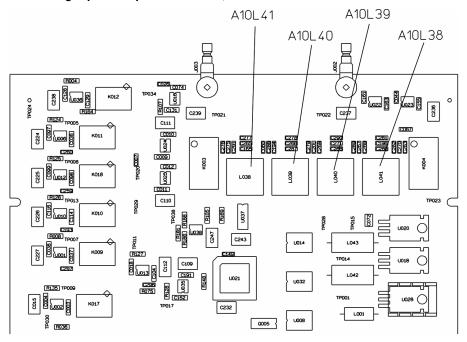

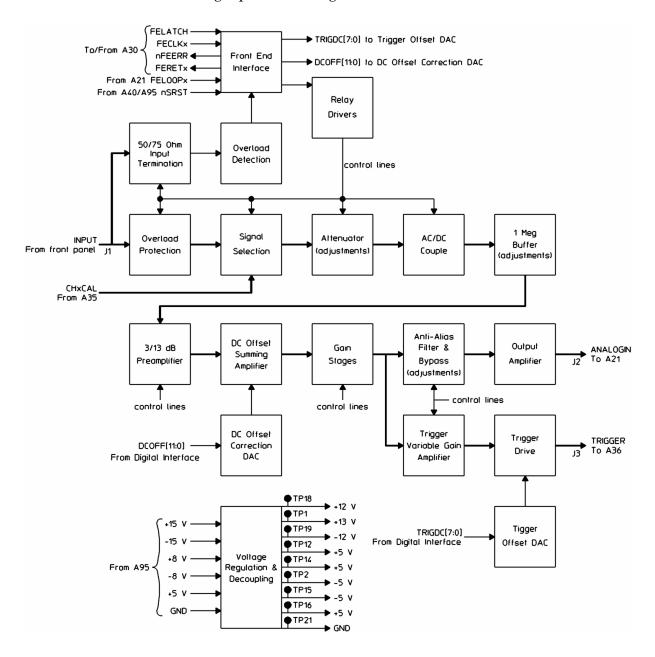

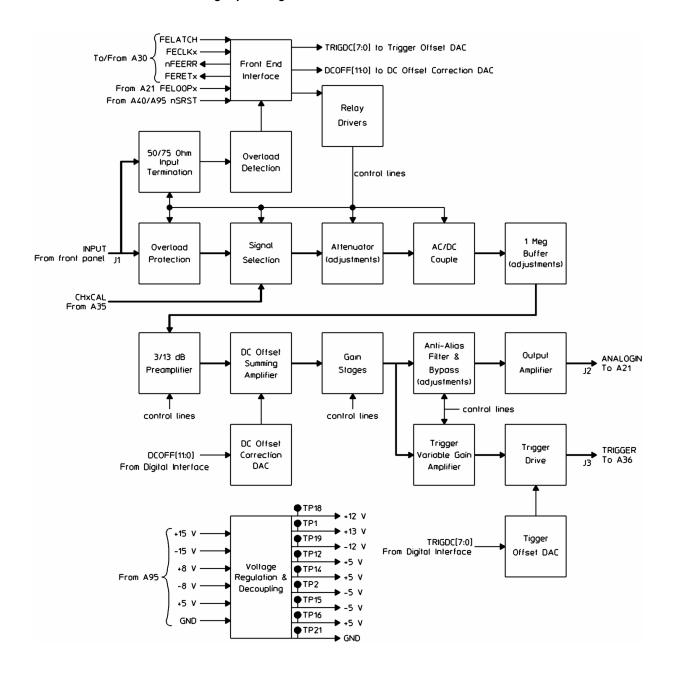

|           | A10 Analog Input.                      |                |

|           | A11 Front Panel Connector              |                |

|           | A12 Rear Panel Connector               |                |

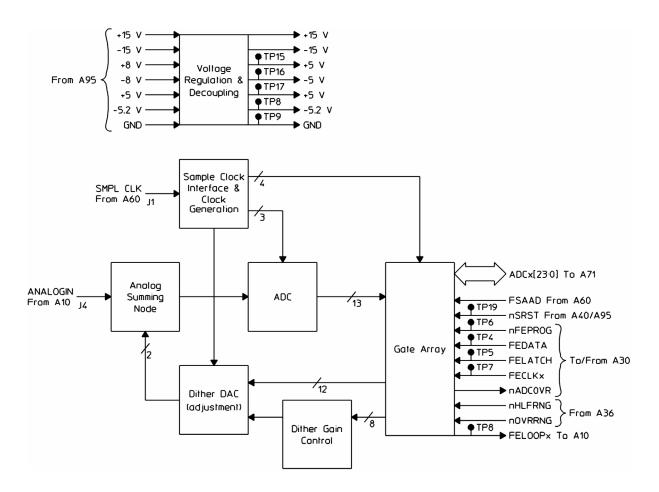

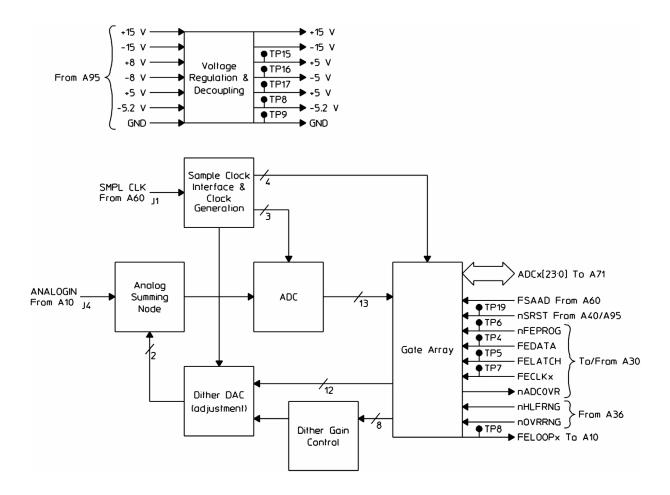

|           | A21 A/D Converter                      |                |

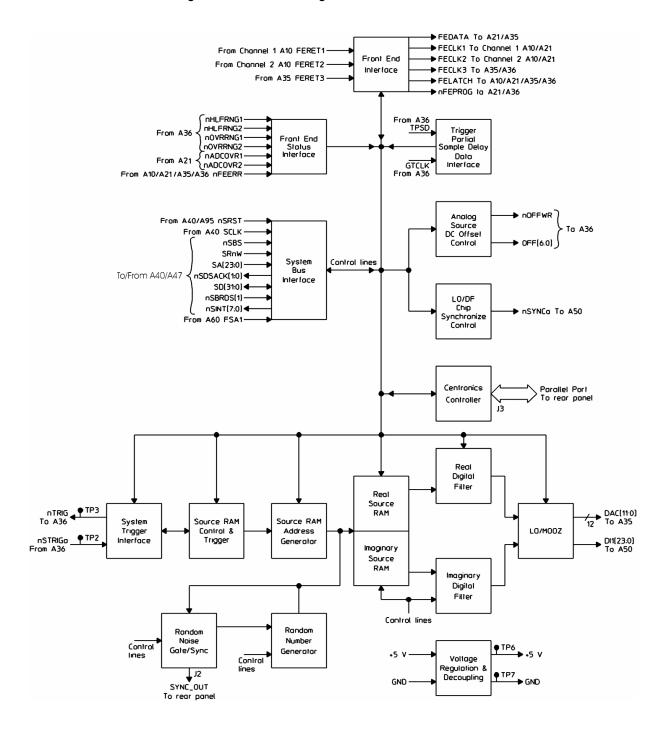

|           | A30 Digital Source.                    |                |

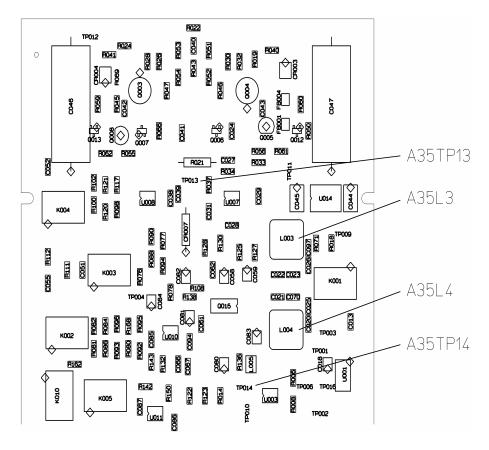

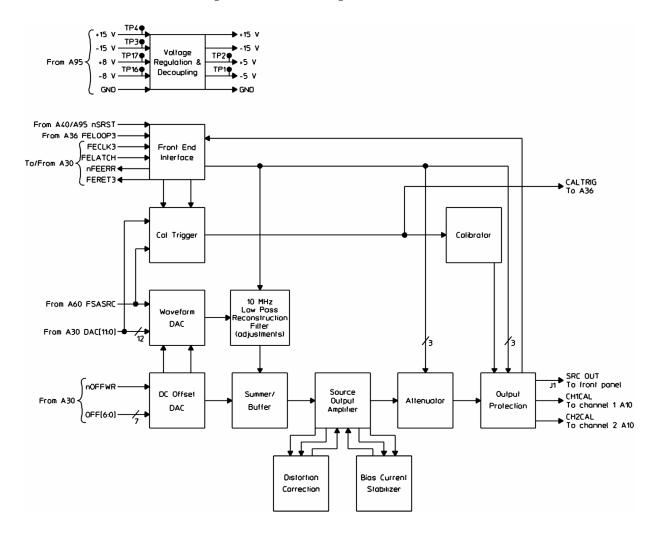

|           | A35 Analog Source.                     |                |

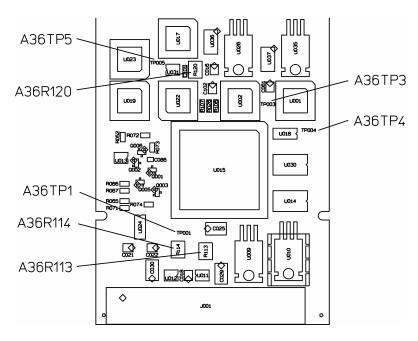

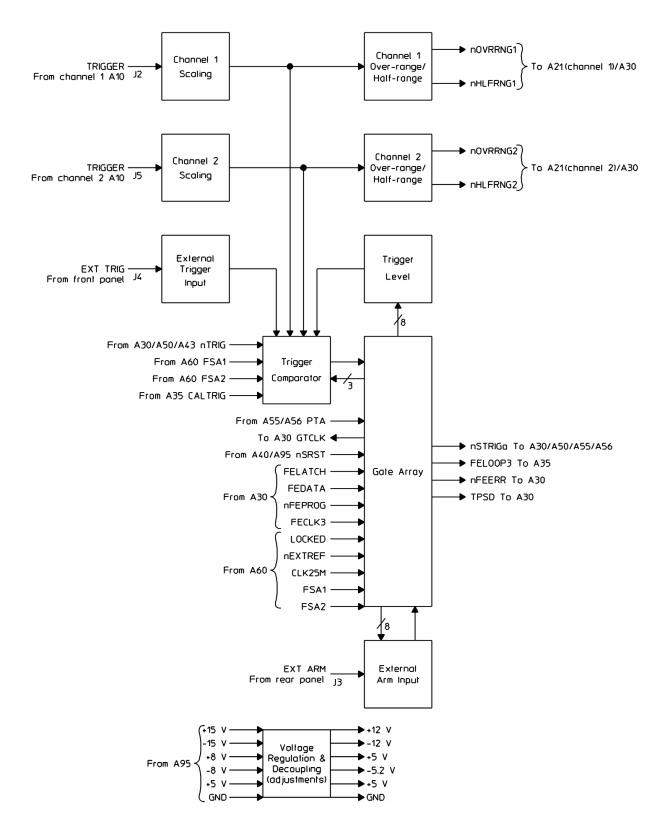

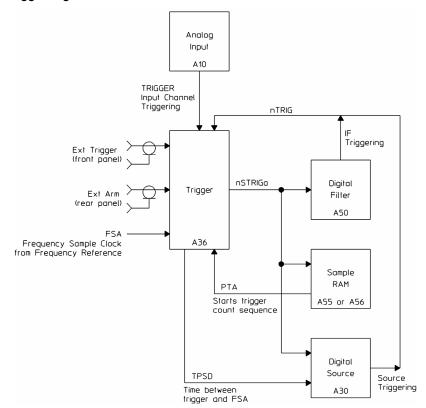

|           | A36 Trigger                            |                |

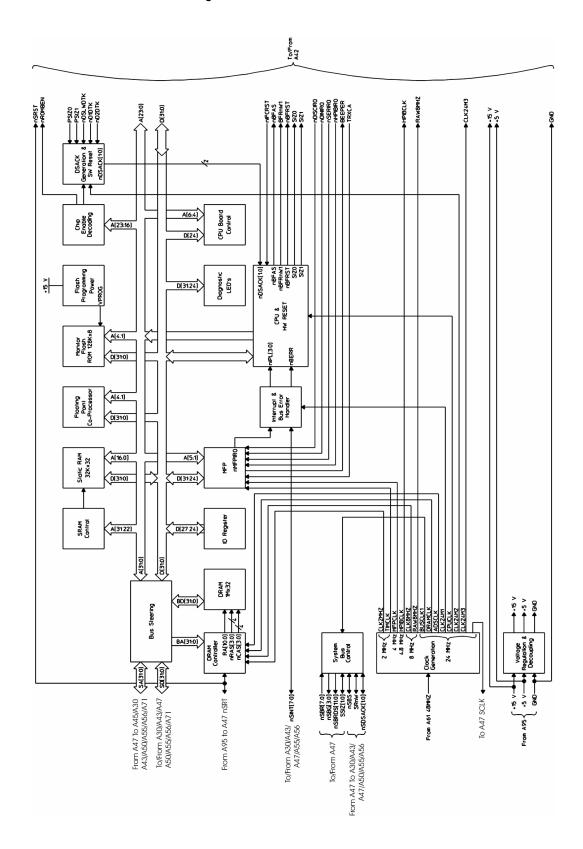

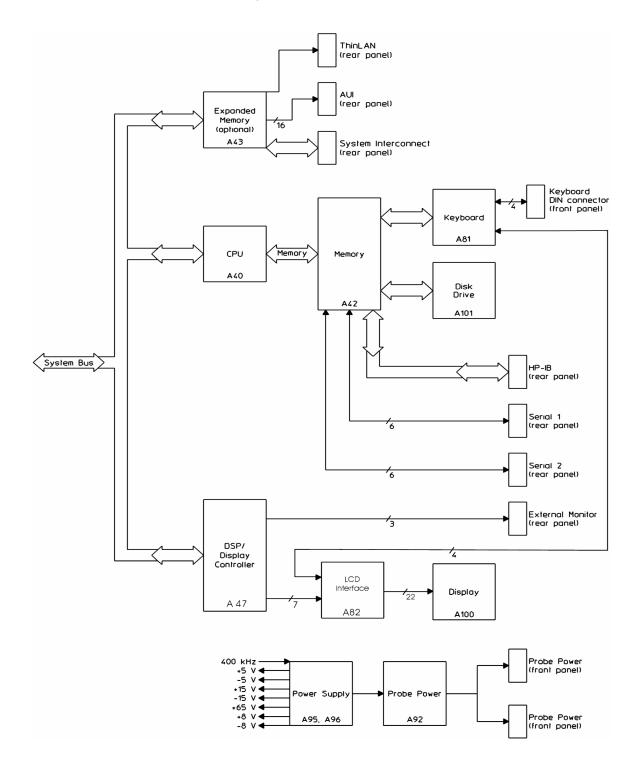

|           | A40 CPU.                               |                |

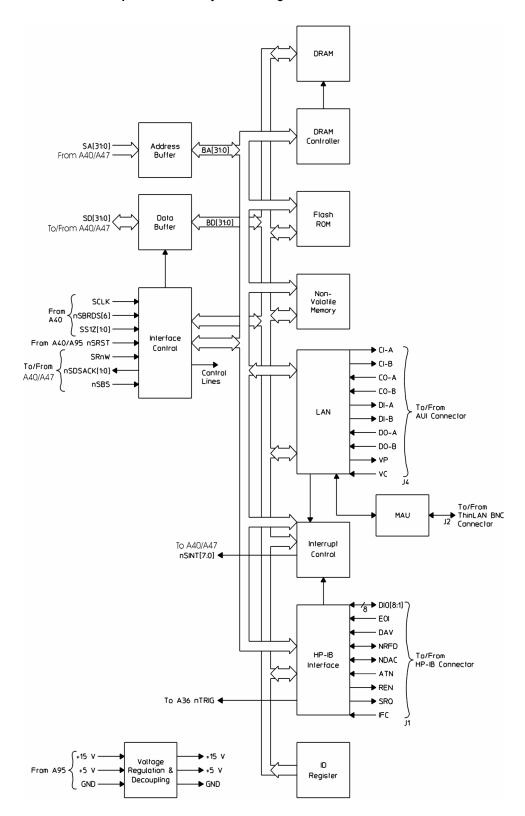

|           | A42 Memory.                            |                |

|           | A43 Expanded Memory.                   |                |

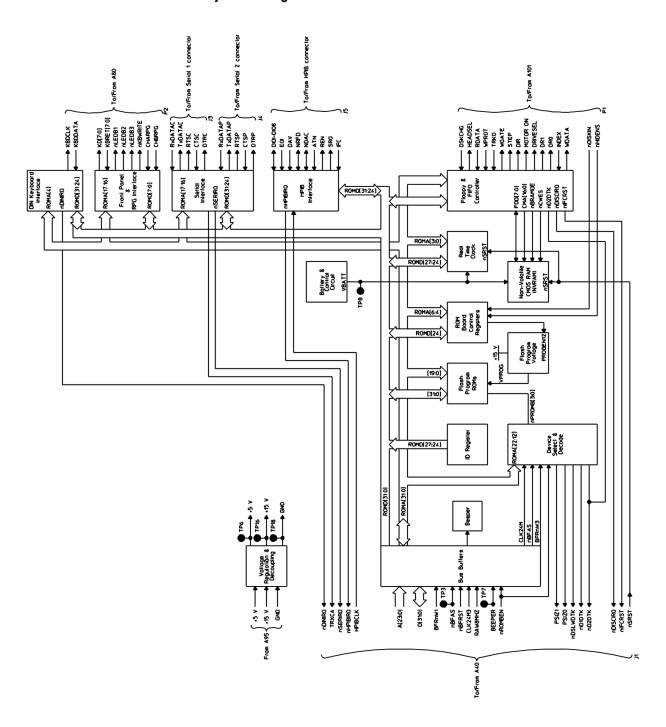

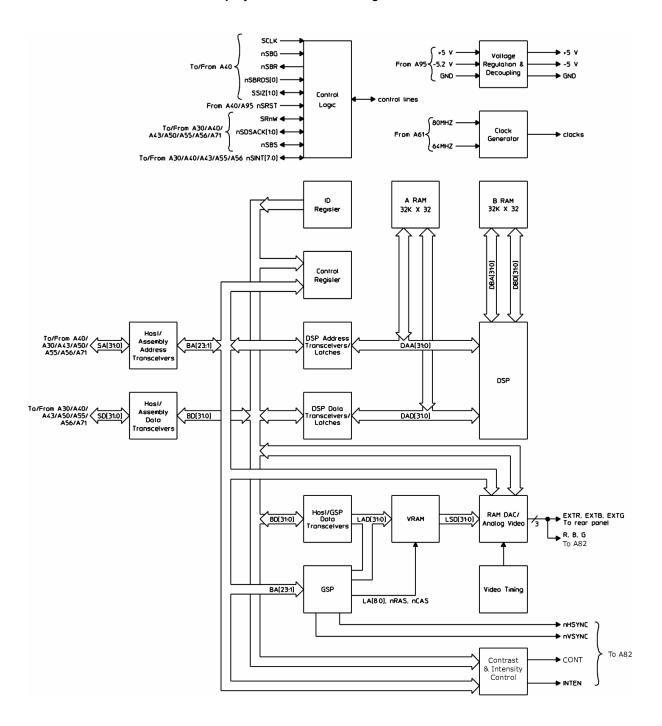

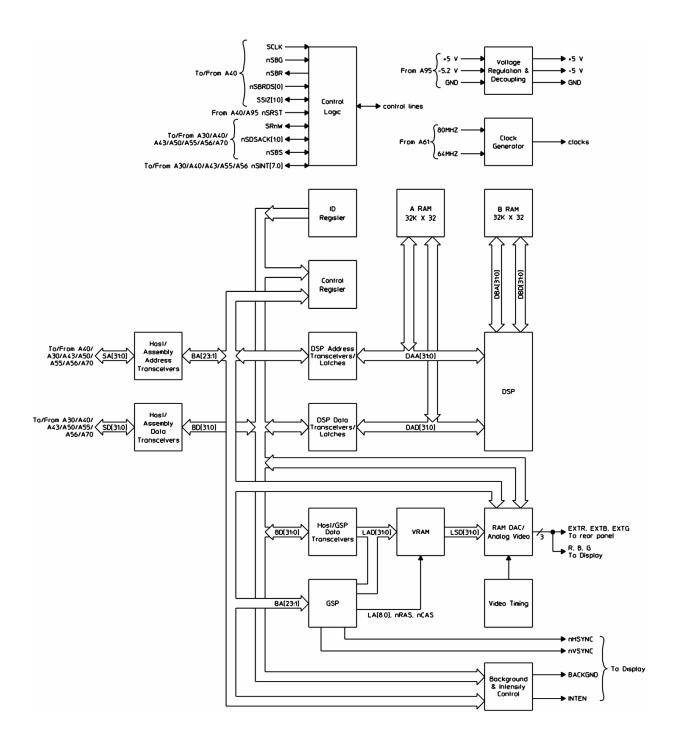

|           | A47 DSP/Display Controller             |                |

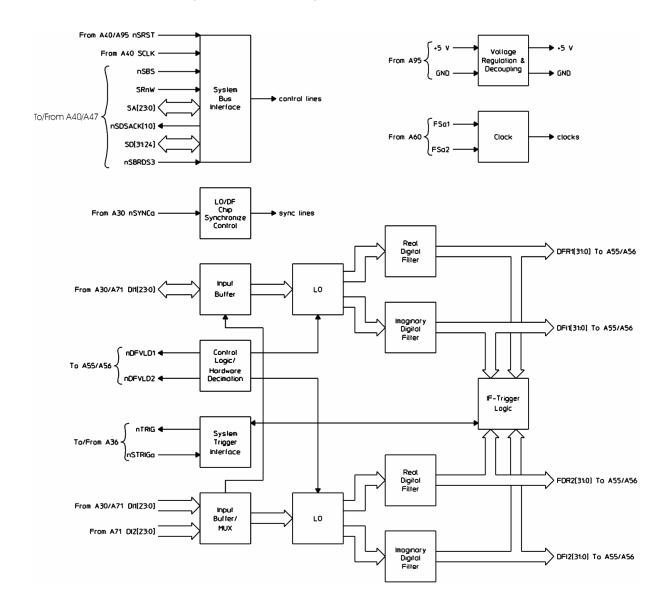

|           | A50 Digital Filter                     |                |

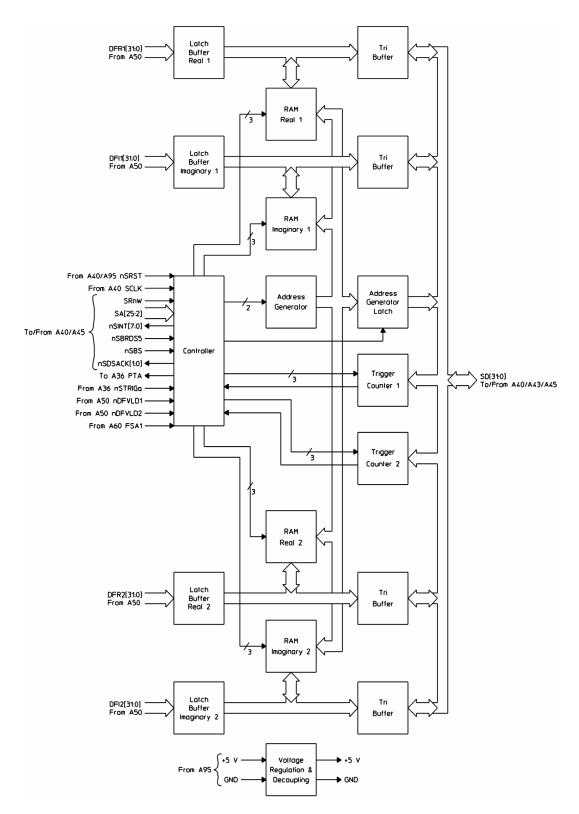

|           | A55 Sample RAM/A56 Expanded Sample RAM |                |

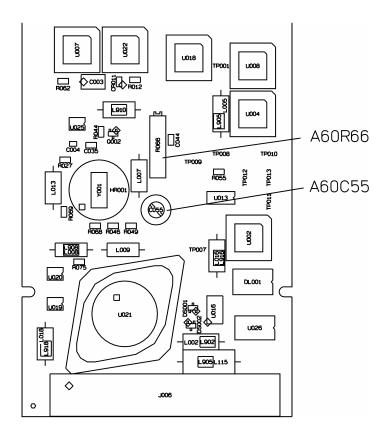

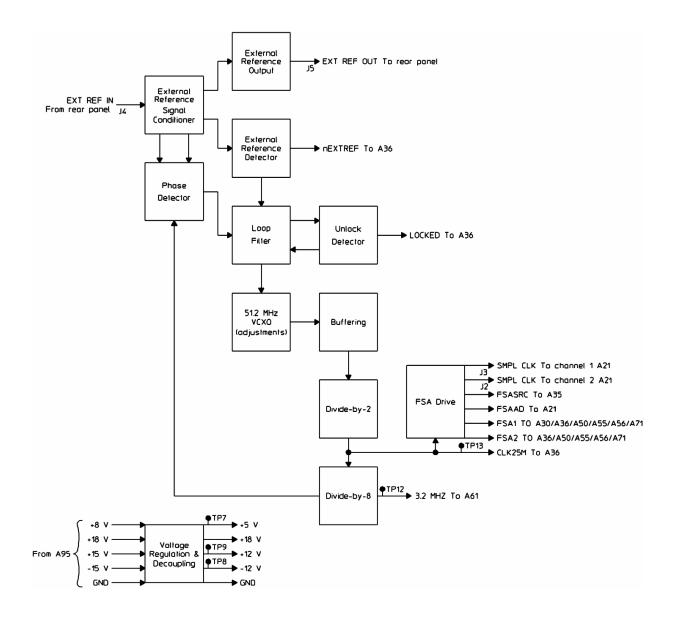

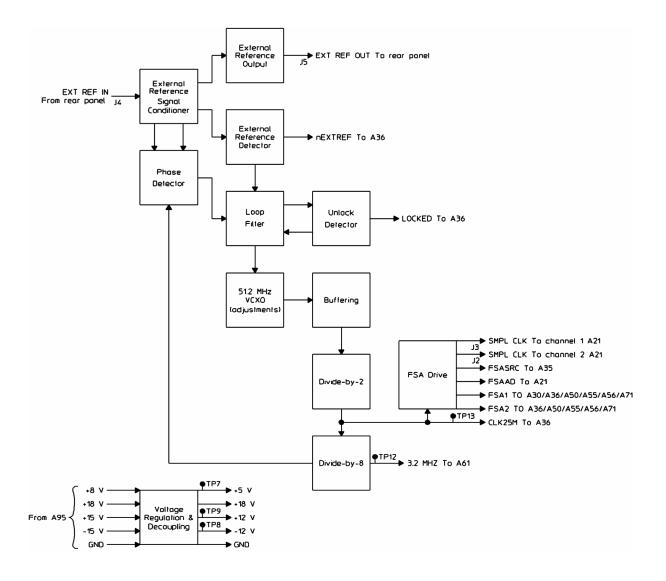

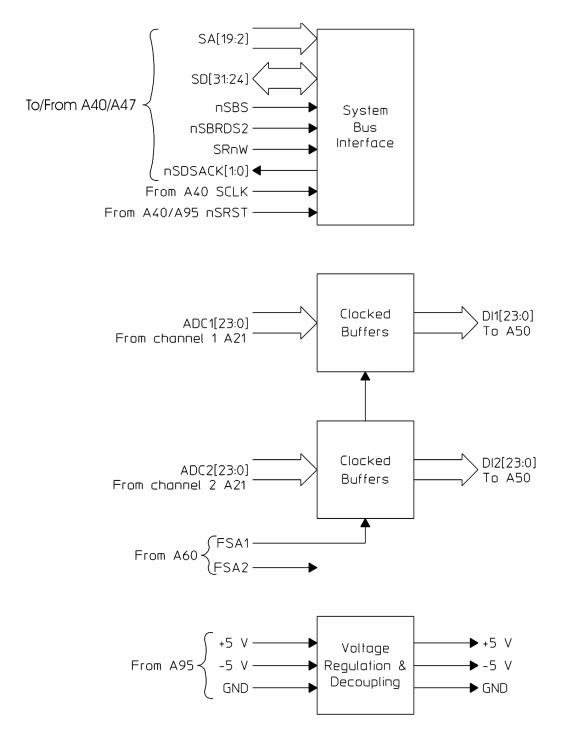

|           | A60 Frequency Reference                |                |

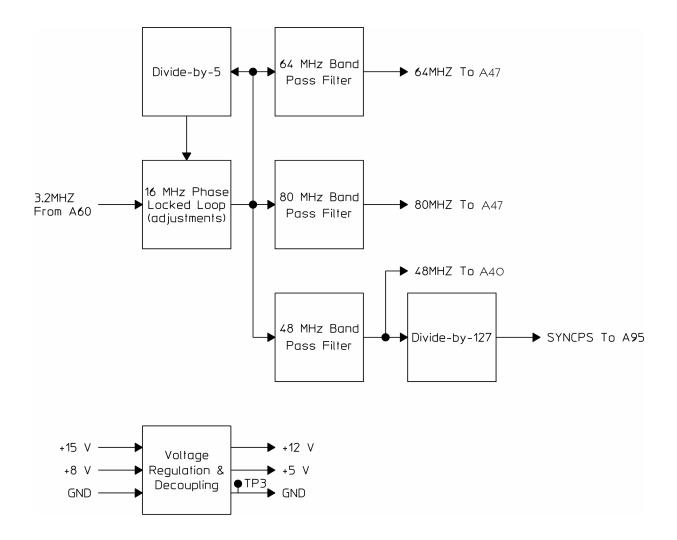

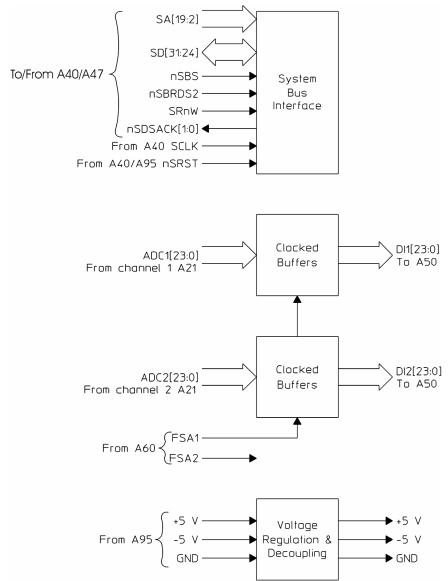

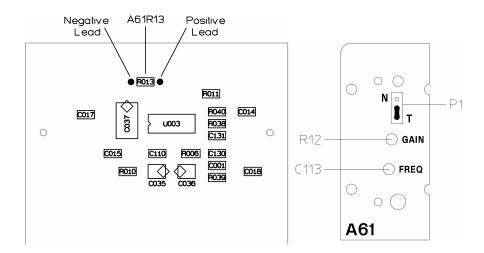

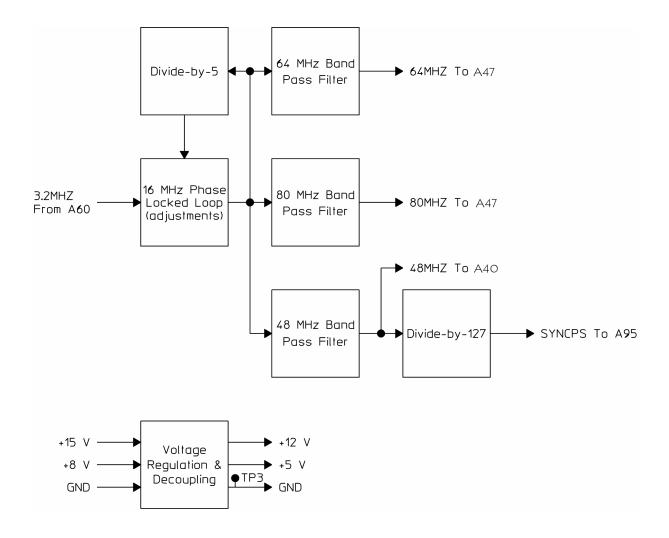

|           | A61 Clock                              |                |

|           | A71 Pass Through                       |                |

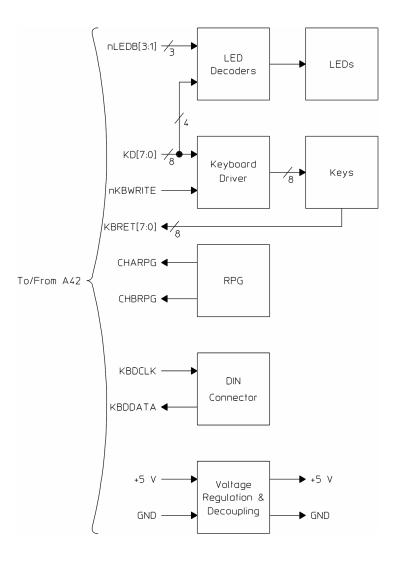

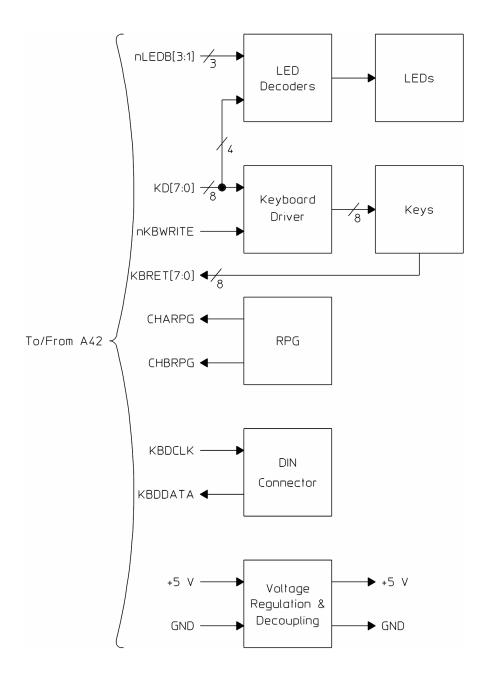

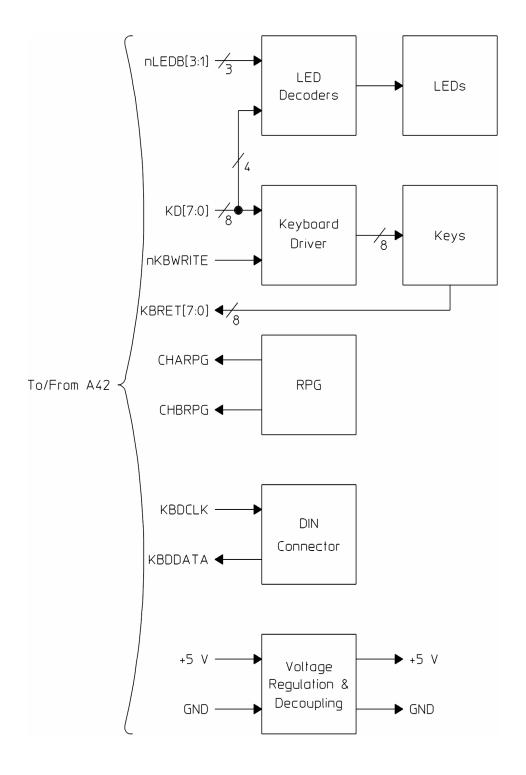

|           | A81 Keyboard.                          |                |

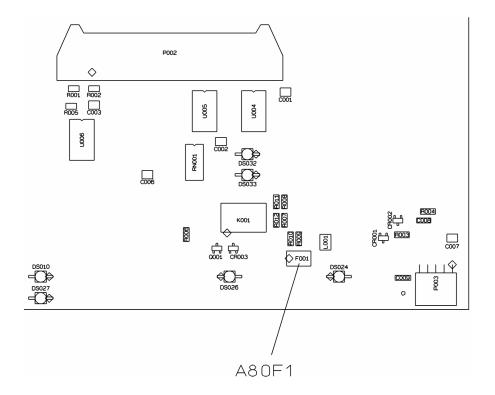

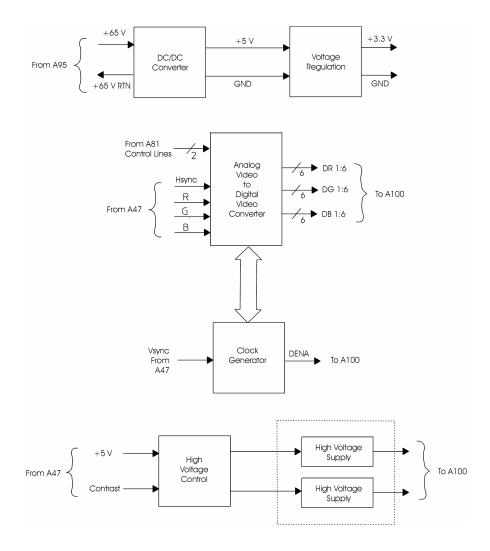

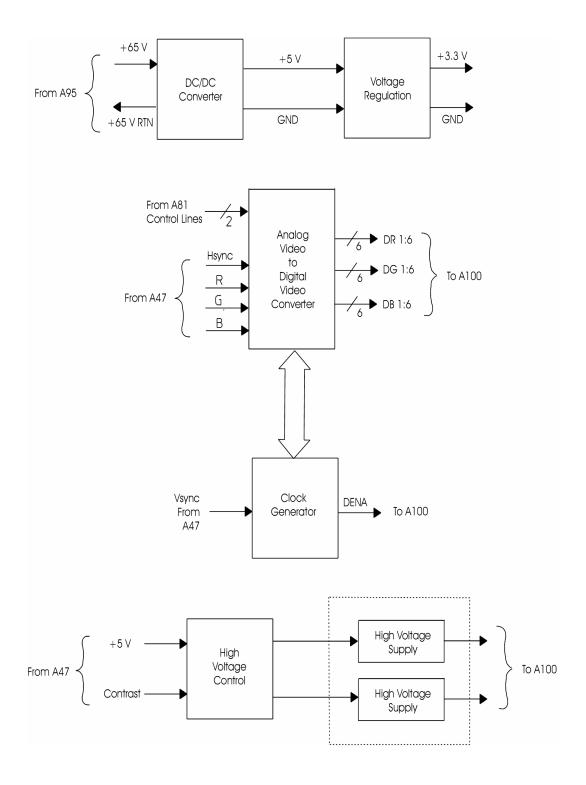

|           | A82 LCD Interface Circuit Descriptions |                |

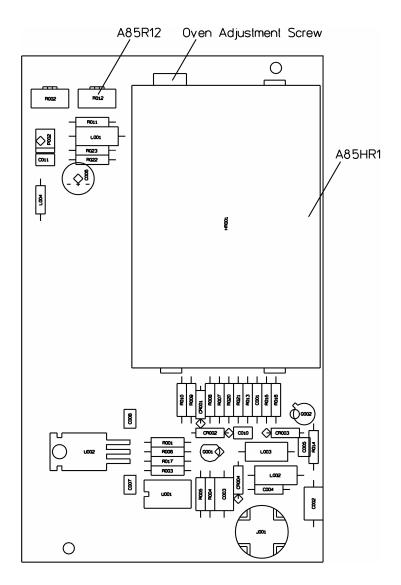

|           | A85 Oven                               |                |

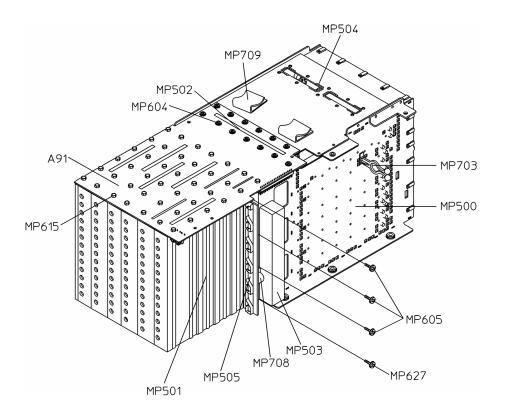

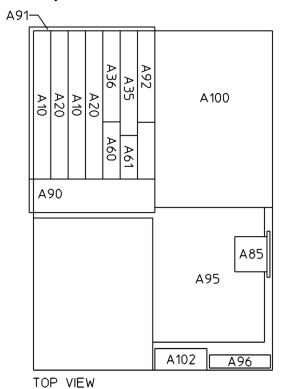

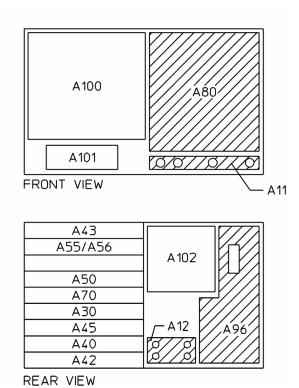

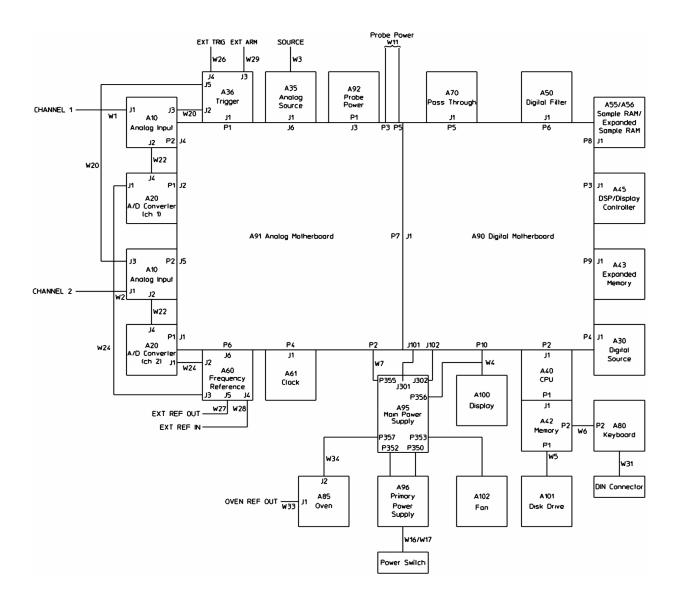

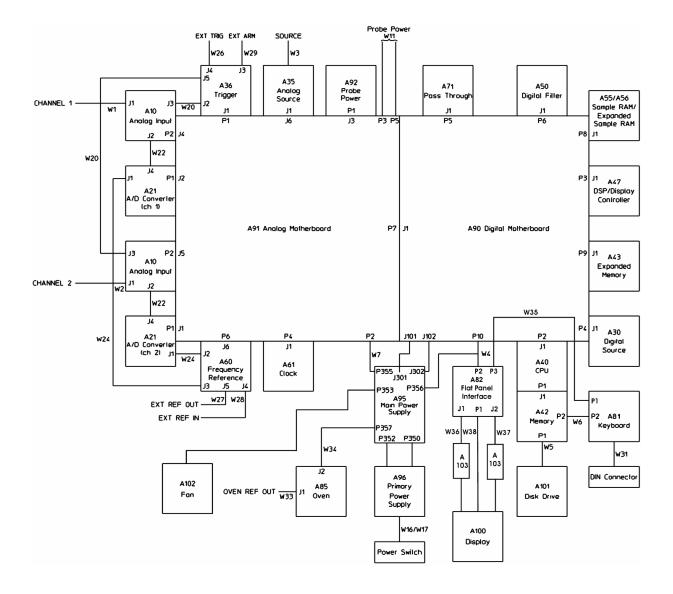

|           | A90 Digital Motherboard                |                |

|           | A91 Analog Motherboard                 |                |

|           | A92 Probe Power                        |                |

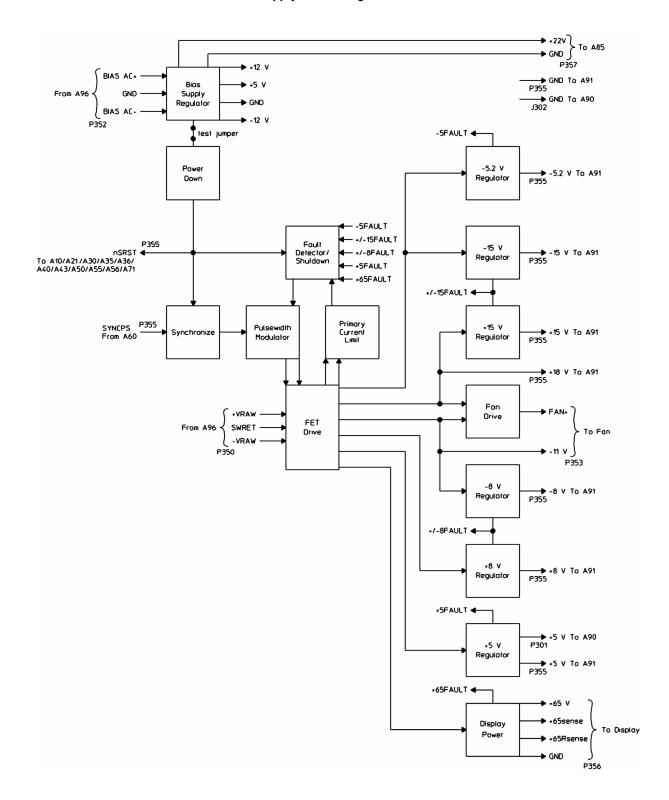

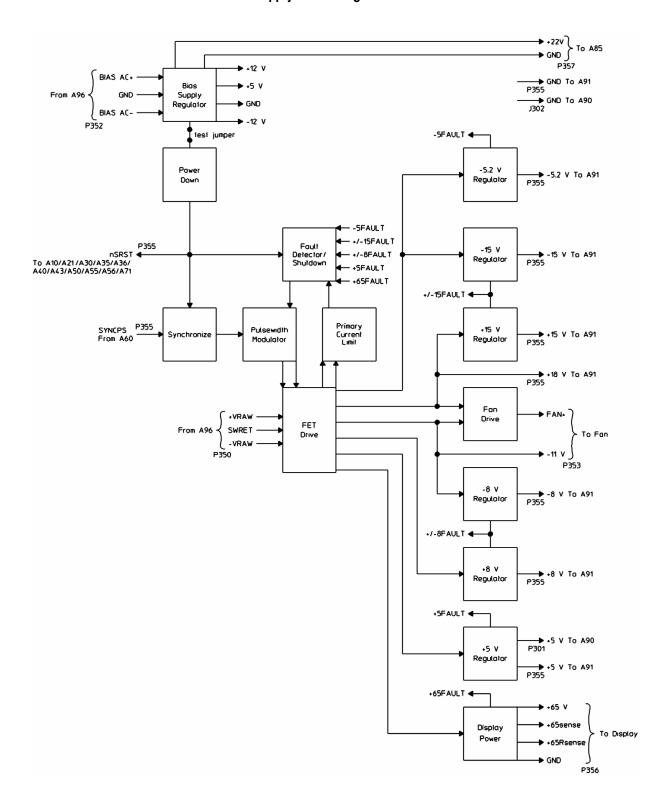

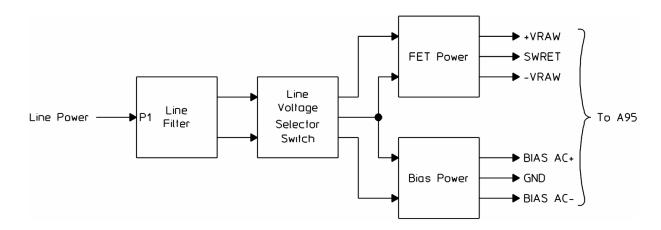

|           | A95 Main Power Supply                  |                |

|           |                                        |                |

|           | A100 Diamless                          |                |

|           | A101 Dish Drive                        |                |

|           | A101 Disk Drive                        |                |

|           | A102 Fan                               | . อ-๒อ         |

| 6.        | Voltages and Signals                   |                |

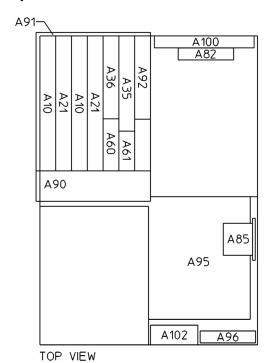

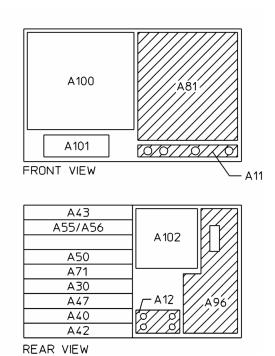

| •         | Assembly Locations and Connections     | 6-4            |

|           | Power Supply Voltage Distribution      |                |

|           | RF Cables.                             |                |

|           | A42 Memory.                            |                |

|           |                                        | . 0-10<br>6 14 |

# **Contents**

|           | A90 and A91 Motherboards                 | 6-16 |

|-----------|------------------------------------------|------|

|           | A101 Disk Drive                          | 6-33 |

|           | Interface Connectors                     |      |

| <b>7.</b> | Internal Test Descriptions               |      |

|           | Power-on Test Descriptions               | 7-4  |

|           | Calibration Routine                      |      |

|           | Fault Log Messages                       |      |

|           | Self-Test Descriptions                   |      |

|           | Individual Self-Test Descriptions        |      |

|           | Self-Test Menu Map and HPIB Commands     |      |

| 8.        | Backdating                               |      |

|           | To adjust clock                          | 8-5  |

|           | To adjust display                        |      |

|           | To remove display                        |      |

|           | Assemblies                               |      |

|           | Cables                                   |      |

|           | Assembly Covers and Brackets             |      |

|           | Front Panel Parts                        |      |

|           | Overall Block Diagram                    |      |

|           | A45 DSP/Display Controller Block Diagram |      |

|           | A80 Keyboard Block Diagram               |      |

|           | Assembly Locations and Connections       |      |

# 9. Quick Reference

**Troubleshooting the Analyzer**

#### Troubleshooting the Analyzer

- How to troubleshoot the analyzer, page 1-8

- To perform initial verification, page 1-10

- To troubleshoot the power supply, page 1-15

- To troubleshoot display failures, page 1-25

- To perform self tests, page 1-32

- To troubleshoot self-test lockup failures, page 1-48

- To troubleshoot intermittent failures, page 1-52

- To troubleshoot performance test failures, page 1-58

- To troubleshoot front-end control failures, page 1-60

- To troubleshoot source and calibrator out failures, page 1-62

- To troubleshoot input and ADC failures, page 1-71

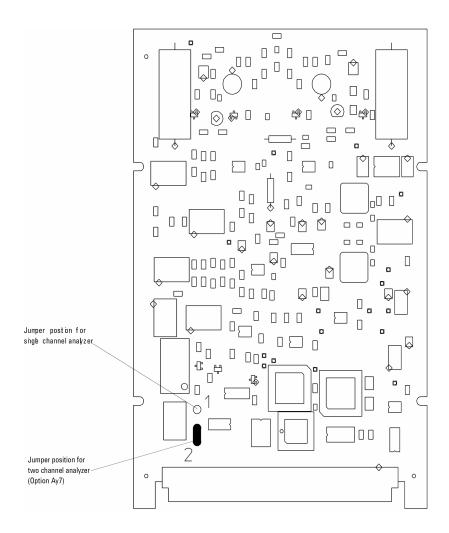

- To troubleshoot two channel analyzer failures, page 1-75

- To troubleshoot auto-range failures, page 1-80

- To troubleshoot trigger failures, page 1-83

- To troubleshoot disk drive failures, page 1-88

- To troubleshoot serial port failures, page 1-91

- To troubleshoot DIN connector failures, page 1-92

- To troubleshoot memory battery failures, page 1-93

- To troubleshoot sync out and parallel port failures, page 1-95

- To troubleshoot system interconnect and LAN port failures, page 1-96

# **Troubleshooting the Analyzer**

This chapter contains troubleshooting tests that can isolate most failures to the faulty assembly. The section "How to troubleshoot the analyzer" tells you which test to start with based on the failure. The test you start with will either isolate the faulty assembly or send you to another test to continue troubleshooting.

#### **Safety Considerations**

The Agilent 89410A DC-10 MHz Vector Signal Analyzer is a Safety Class 1 instrument (provided with a protective earth terminal). Although the instrument has been designed in accordance with international safety standards, this manual contains information, cautions, and warnings that must be followed to ensure safe operation and retain the instrument in safe operating condition. Service must be performed by trained service personnel who are aware of the hazards involved (such as fire and electrical shock).

WARNING: Any interruption of the protective (grounding) conductor inside or outside the analyzer, or disconnection of the protective earth terminal can expose operators to potentially dangerous voltages.

An operator should not remove any covers, screws, shields or in any other way access the interior of the Agilent 89410A DC-10 M Hz Vector Signal Analyzer unless instructed by an option installation note. There are no operator controls inside the analyzer.

Only fuses with the required current rating and of the specified type should be used for replacement. The use of repaired fuses or short circuiting the fuse holder is not permitted. Whenever it is likely that the protection offered by the fuse has been impaired, the analyzer must be made inoperative and secured against any unintended operation.

When power is removed from the Agilent 89410A DC-10 MHz Vector Signal Analyzer, + 11000 volts are present in the CRT for approximately 3 seconds. Be extremely careful when working in proximity to this area during this time. The high voltage can cause serious personal injury if contacted.

**CAUTION:** Do not connect or disconnect ribbon cables with the power switch set to on (1). Power transients caused by connecting or disconnecting a cable can damage circuit assemblies.

#### **Equipment Required**

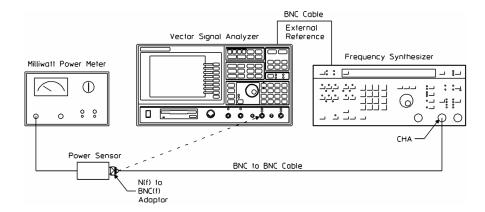

The following table lists the recommended equipment needed to adjust and troubleshoot the analyzer. Other equipment may be substituted for the recommended model if it meets or exceeds the listed critical specifications. When substitutions are made, you may have to modify the procedures to accommodate the different operating characteristics.

#### **Recommended Test Equipment**

| Instrument            | Critical Specifications                                                                                                                                                             | Recommended M odel                                                                  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Frequency Standard    | Accuracy ±0.5 ppm                                                                                                                                                                   | Agilent 5061B                                                                       |  |

| Frequency Synthesizer | Frequency range 3 Hz to 10 MHz Amplitude range —36 to +20 dBm Amplitude resolution 0.01 Hz Impedance 50 Ω Harmonic distortion <—30 dBc Spurious <—70 dBc External reference input   | Agilent 3326A<br>Alternate<br>Agilent 3325A<br>Agilent 3325B                        |  |

| Milliwatt Power Meter | Range ±0.2 dBm<br>Accuracy ±0.0625 dB                                                                                                                                               | W&G EPM-1†                                                                          |  |

| Spectrum Analyzer     | Frequency range 100 Hz to 40 MHz Amplitude range $-60$ to $+15$ dBm Dynamic range $<-67$ dBc Tracking Source @ 0 dBm Impedance 50 $\Omega$ and 75 $\Omega$ External reference input | Agilent 3585B<br>Alternate<br>Agilent 3585A<br>Agilent 3588A<br>Agilent 3589A       |  |

| Digital Multimeter    | Accuracy 25 ppm<br>Maximum volts range ≥400 Vdc                                                                                                                                     | Agilent 3458A<br>Alternate<br>Agilent 3456A                                         |  |

| Frequency Counter     | Frequency range 3 to 30 M Hz Resolution <1 Hz Frequency accuracy $\pm 0.25$ Hz Impedance 1 M $\Omega$                                                                               | Agilent 5334B opt 010                                                               |  |

| Network Analyzer      | Range 10 kHz to 60 MHz Resolution 10 Hz Input impedance 50 Ω Amplitude range -42 dBm to +10 dBm resolution 0.25 dB dynamic accuracy 0.3 dBp-p from 10 kHz to 16 MHz                 | Agilent 3577B<br>Alternate<br>Agilent 4195A<br>Agilent 3589A with<br>Agilent 35689A |  |

†Wandel & Goltermann Inc., 1800 Wyatt Drive, Suite 2, Santa Clara, CA 95054 U.S.A (408)988-7622

### **Recommended Test Equipment (continued)**

| Logic Probe                                         | TTL/ CM OS                                                                                                                                                                                                                                               | Agilent 545A<br>Alternate<br>Agilent 5006A<br>Agilent 5005A/ B                                                                                                                                                                            |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oscilloscope                                        | Bandwidth $\geq$ 150 M Hz<br>Vertical sensitivity 10 mV/ div<br>Input coupling AC, DC, 50 $\Omega$ , 1 M $\Omega$<br>Trigger Ext, Int                                                                                                                    | Agilent 54111D                                                                                                                                                                                                                            |

| Oscilloscope Probe                                  | Input R $\geq$ 1 M $\Omega$<br>Division Ratio 1:1                                                                                                                                                                                                        | Agilent 10438A                                                                                                                                                                                                                            |

| Oscilloscope Probe                                  | Input R ≥1 M Ω<br>Division Ratio 10:1                                                                                                                                                                                                                    | Agilent 10431A                                                                                                                                                                                                                            |

| $50~\Omega$ Feedthrough Termination (2 for opt AY7) | Accuracy ±0.2%                                                                                                                                                                                                                                           | Agilent 11048C                                                                                                                                                                                                                            |

| (2) 50 Ω Termination                                | ±2% at dc                                                                                                                                                                                                                                                | Pomona Model 3840-50 †<br>Alternate<br>Agilent 11048C with<br>Agilent 1250-0774                                                                                                                                                           |

| ThinLAN Transceiver                                 | AUI to ThinLAN adapter                                                                                                                                                                                                                                   | Agilent 28641B                                                                                                                                                                                                                            |

| Cables                                              | (4) 50 $\Omega$ BNC Test clips-to-double banana plug                                                                                                                                                                                                     | Agilent 8120-1840<br>Agilent 11002A                                                                                                                                                                                                       |

| Adapters                                            | BNC(f)-to-Dual Banana Plug<br>N(m)-to-BNC(f) (2)<br>Test Clips-to-BNC(f)<br>BNC Tee<br>N(f)-to-BNC(f)<br>BNC(f)-to-Dual Banana Plug(m)<br>BNC(f)-to-BNC(f)                                                                                               | Agilent 1251-2816<br>Agilent 1250-0780<br>Pomona Model 2631 †<br>Agilent 1250-0781<br>Agilent 1250-1536<br>Agilent 1251-2277<br>Agilent 1250-0080                                                                                         |

| Service Kit  10 kW Series Resistor ††               | Includes A10/ A35 extender board A36/ A60 extender board A61 extender board Motherboard cable extraction tool Plastic screw driver Flat-edge adjustment tool SMB extender cable (2) BNC(m)-to-SMB(f) cable (2) SMB(m)-to-SMB(m) adapter (2) Value: 10 kΩ | Agilent 89410-84401<br>Includes<br>Agilent 89410-B1001‡<br>Agilent 89410-B1002‡<br>Agilent 89410-B1008‡<br>Agilent 8710-2050<br>Agilent 8710-2056<br>Agilent 8710-1928<br>Agilent 03585-61601<br>Agilent 03585-61616<br>Agilent 1250-0669 |

|                                                     | Accuracy: 1% Power: 0.125 $\Omega$                                                                                                                                                                                                                       | Ţ                                                                                                                                                                                                                                         |

| CPU/ Memory Service Utility<br>Disk                 |                                                                                                                                                                                                                                                          | Agilent 89410-19463                                                                                                                                                                                                                       |

$\dagger$ ITT Pomona Electronics, 1500 East Ninth Street, Pomona, CA 91769 U.S.A. (714) 469-2900 FAX (714) 629-3317  $\dagger$ Individual extender boards cannot be ordered. To order all three extender boards in this kit, order Agilent 89410-66515.

$\dagger\dagger See$  the following for assembly.

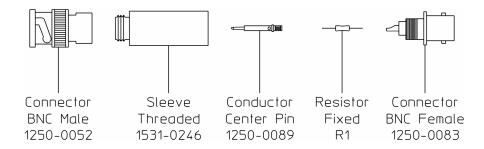

#### **Suggested Assembly for Series Resistor**

The following is a suggested assembly for the 10 kW series resistor. The 10 k $\Omega$  series resistor is required for the Input Offset adjustment.

- 1 Cut resistor leads to 12 mm on each end.

- 2 Solder one resistor lead to the center conductor of the BNC female connector.

- 3 Solder the conductor center pin to the other lead of the resistor.

- 4 Screw the sleeve and the BNC male connector into place. Tighten securely.

#### **Troubleshooting Hints**

- Check that the analyzer has the latest firmware before starting the troubleshooting procedures.

- Incorrect bias supply voltages can cause false diagnostic messages. Most troubleshooting procedures do not check the power supply voltages through the motherboard. If you suspect incorrect supply voltages to an assembly, use the "A90/A91 Motherboard Voltages" table on page 6-24 and an extender board to check the voltages at the assembly.

- The troubleshooting procedures do not isolate failures to cables or connectors. If you suspect a cable or connector failure, check the device for continuity.

- Cables can cause intermittent hardware failures.

- Noise or spikes in the power supply can cause the analyzer to fail.

- Measurements in this chapter are only approximate (usually ±1 dB or 10%) unless stated otherwise.

- Use chassis ground for all measurements in this chapter unless stated otherwise.

- Logic levels in this chapter are either TTL level high or TTL level low unless stated otherwise. Toggling signal levels continually change from one TTL level to the other.

- Configure a logic probe with an external bias supply for testing digital signals. This analyzer does not have easily accessible +5 V supplies.

- If you abort a self test before the self test is finished, the analyzer may fail its calibration routine. To prevent this from happening press [Preset] or cycle power after you abort the self test.

- The troubleshooting tests in this chapter assume only one independent failure. Multiple failures can cause false results.

# How to troubleshoot the analyzer

1 Review "Safety Considerations" and "Troubleshooting Hints."

WARNING: Service must be performed by trained service personnel who are aware of the hazards involved (such as fire and electrical shock).

- **2** See Replacing Assemblies in chapter 3 to determine how to disassemble and assemble the analyzer.

- **3** Determine which test to start with by comparing the analyzer's symptoms to the symptoms in the following table.

| Symptom                                                                                                                                                                                                                                                                          | Troubleshooting Test               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Screen blank Screen grid is distorted or not displayed After power up, >3 minutes before keys active No response when key is pressed Incorrect response when key is pressed Fatal System Error Please Cycle Power message displayed Fan not turning                              | Initial verification,<br>page 1-10 |

| Keys are active and screen grid is displayed but screen is defective                                                                                                                                                                                                             | Display, page 1-25                 |

| Error messages Calibration fails Performance test fails Intermittent failure HPIB fails Serial port fails External monitor port fails Parallel port fails Sync out fails System interconnect port fails ThinLAN port fails AUI port fails Probe power fails Oven reference fails | Self tests, page 1-32              |

| HPIB trigger fails<br>External trigger fails                                                                                                                                                                                                                                     | Trigger, page 1-83                 |

| External keyboard does not work                 | DIN connector,<br>page 1-92 |

|-------------------------------------------------|-----------------------------|

| NVRAM or Battery failure message displayed      | Memory battery,             |

| Nonvolatile states not saved after power cycled | page 1-93                   |

- **4** Follow the recommended troubleshooting test until you locate the faulty assembly.

- **5** Replace the faulty assembly and follow the directions in "What to do after replacing an assembly" in chapter 3, "Replacing Assemblies page 3-5."

# To perform initial verification

Use this test to check signals that are vital to the operation of the analyzer.

- 1 Check voltage selector switch and fuse.

- **a** Check that the voltage selector switch on the rear of the analyzer is set for the local line voltage.

- **b** Check that the correct line fuse is installed in the rear panel fuse holder.

For information on the voltage selector switch and line fuse, see "To change the line-voltage selector switch" and "To change the fuse" in chapter 1 of the *Agilent 89410A Installation and Verification Guide*.

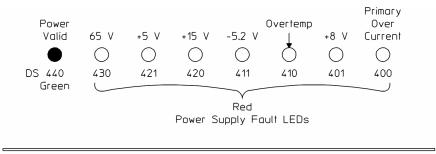

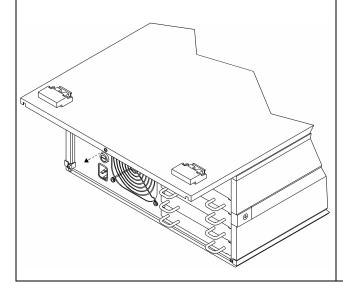

- 2 Check power supply LEDs and fan.

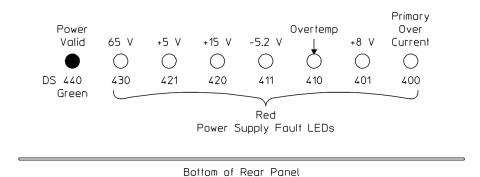

- **a** Check that no power supply fault LEDs are lit and that DS 440 (green) is lit.

- **b** If any fault LEDs are lit or if the green power valid LED (DS 440) is not lit, go to page 1-15, "To troubleshoot the power supply."

Bottom of Rear Panel

- **c** Check that the fan is turning at a moderate speed for normal room temperature.

- The fan speed increases as the analyzer's internal temperature increases. If the fan is turning too fast, check that the air flow around the analyzer is not constricted and that the ambient temperature is between 0 and 55  $^{\circ}$ C.

- **d** If the fan is not turning, go to page 1-15, "To troubleshoot the power supply."

- This quick check does not completely check the power supply. If a power supply failure is still suspected, go to page 1-15 "To troubleshoot the power supply."

- **3** If the grid appears after power up, check that the calibration routine is not locking up the analyzer.

- **a** Set the power switch to off (O).

- $\label{eq:below_softkeys} \textbf{b} \quad \text{Press and hold [Return] (below softkeys)} \ \, \text{while setting the power} \\ \quad \text{switch to on (1)}.$

- Pressing [Return] while setting the power switch to on (1) causes the analyzer to bypass the calibration routine.

- **c** If the keys are now active, go to page page 1-48, "To troubleshoot self-test lockup failures."

- 4 If the analyzer powers up normally with no error messages (see illustration below), the screen is continually updating, but the analyzer does not respond to key presses, the A80 Keyboard assembly is probably faulty.

# Troubleshooting the Analyzer To perform initial verification

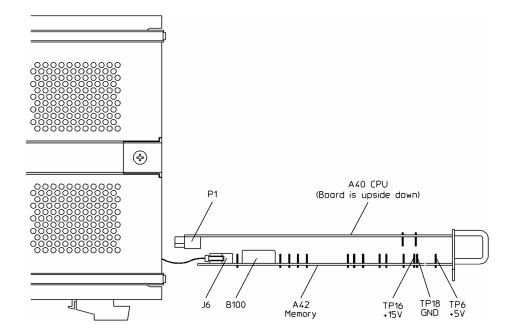

- 5 Check frequency reference signals.

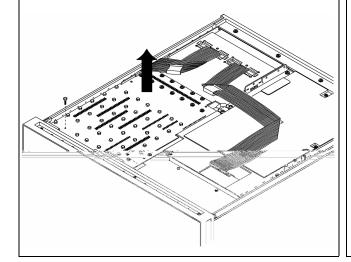

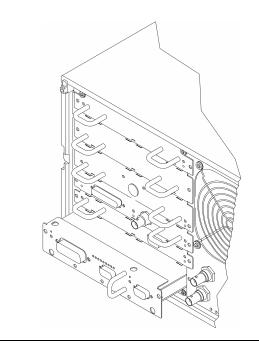

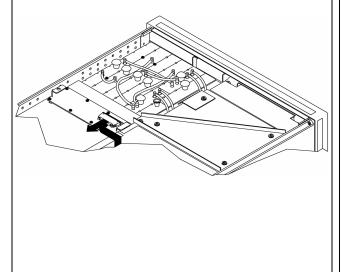

- a Turn the analyzer upside down.

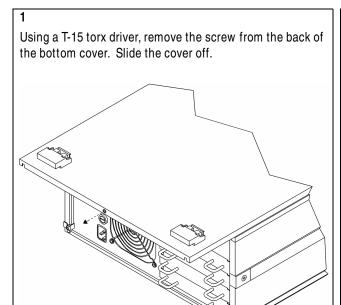

- **b** Remove the bottom cover.

- c Press [Preset].

- d Using an oscilloscope and a 1 M $\Omega$  10:1 probe with a grounding spanner, check the TTL signals in the following table. The probe may load the 64 MHz, 48 MHz, and 80 MHz signals causing their amplitude level to be low.

| Test Location | <b>Ground Connection</b> | Frequency | Probable Faulty Assembly |

|---------------|--------------------------|-----------|--------------------------|

| A91 P6 pin 16 | A91 P6 pin 15            | 25.6 MHz  | A60 Frequency Reference  |

| A91 P6 pin 11 | A91 P6 pin 12            | 25.6 MHz  | A60 Frequency Reference  |

| A91 P6 pin 18 | A91 P6 pin 19            | 3.2 M Hz  | A60 Frequency Reference  |

| A91 P4 pin 5  | A91 P4 pin 6             | 378 kHz   | A61 Clock                |

| A91 P4 pin 21 | A91 P4 pin 22            | 64 M Hz   | A61 Clock                |

| A91 P4 pin 24 | A91 P4 pin 23            | 48 M Hz   | A61 Clock                |

| A91 P4 pin 25 | A91 P4 pin 26            | 80 M Hz   | A61 Clock                |

**e** If a signal is incorrect, replace the probable faulty assembly. Before replacing the A60 Frequency Reference assembly, go to page 1-15, "To troubleshoot the power supply," and do Step 7 to check the power supply voltages.

- 6 Step 6. Check signals required for power up.

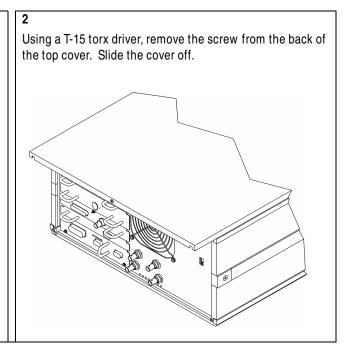

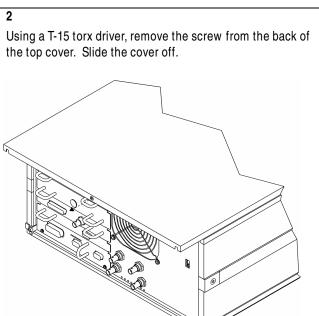

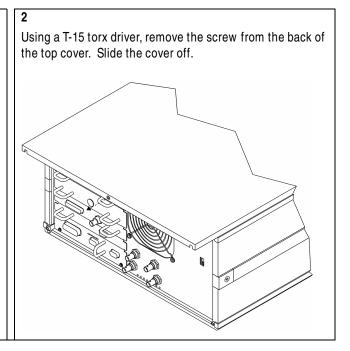

- a Remove the top cover.

- **b** Connect a logic probe to A90 TP4 and its ground clip to A90 TP12.

- **c** Set the power switch off (O) then on (I) and check that A90 TP4 is a TTL high 10 seconds after power up.

- **d** If TP4 remains low, the A40 CPU assembly is probably faulty. Before replacing the assembly, go to page 1-15 "To troubleshoot the power supply," and do Step 7 to check power supply voltages.

- $\boldsymbol{e}$  Set the power switch to off ( O ) and disconnect the ribbon cable from A90 P10.

- **f** Set the power switch to on (1).

**g** Using an oscilloscope and 1 M $\Omega$  10:1 probes, check the following system clock signals.

| ΔΩ                                                                  |                                                                                         |                                                     |                                                     |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| ns/ div<br>g'd Sweep <u>o vdc</u><br>an1                            |                                                                                         |                                                     |                                                     |

| 0 pin 12 Duty Cycle                                                 | onship                                                                                  |                                                     |                                                     |

| $M\Omega$ // div $M\Omega$ petitive $O Vdc$ $O Vdc$ $O Vdc$ $O Vdc$ |                                                                                         |                                                     |                                                     |

|                                                                     | SCLK 0 pin 10 Time 0 pin 12 Duty Cycle Time Relation V/ div M Ω V/ div M Ω O V/ div M Ω | Pepetitive  Ons/ div g'd Sweep nan1  SCLK  O pin 10 | epetitive  O ns/ div g'd Sweep nan1  SCLK  O pin 10 |

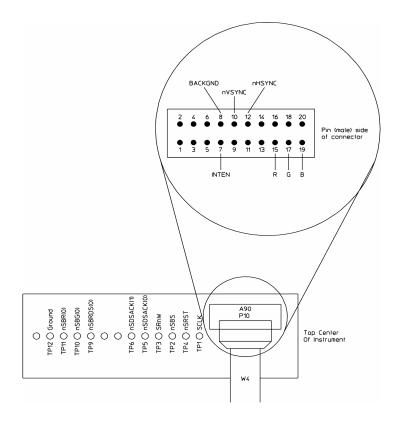

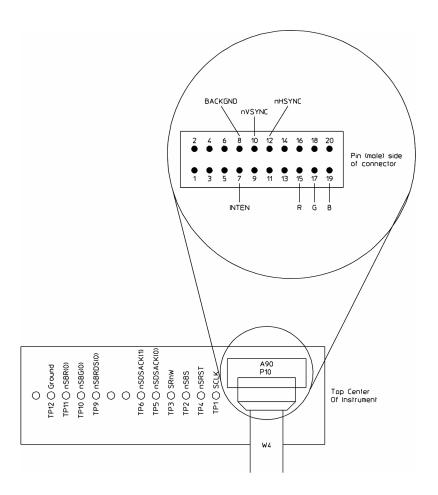

**nVSYNC** and nHSYNC

- h If SCLK is incorrect, the A40 CPU assembly is probably faulty. Before replacing the assembly, go to page 1-15, "To troubleshoot the power supply," and do Step 7 to check power supply voltages.

- i If nVSYNC or nHSYNC is incorrect, the A47 DSP/Display Controller assembly is probably faulty.

- j If the signals are correct, go to page 1-36 "To troubleshoot power-up failures."

Chan1

Trig Src

# To troubleshoot the power supply

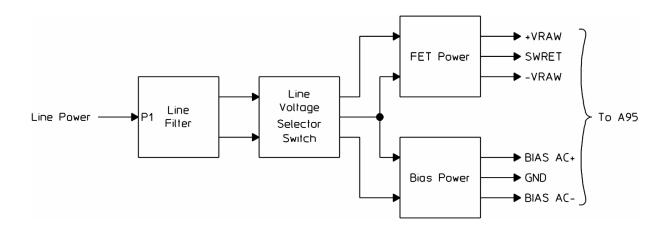

Use this test to do a complete check of the power supply and to isolate the failure between the A95 Main Power Supply assembly and A96 Primary Power Supply assembly.

**WARNING:** This procedure is performed with protective covers removed and power applied. Energy available at may points can, if contacted, result in personal injury.

Even with power removed, there can be sufficient stored energy in some circuits to cause personal injury. These voltages will discharge to a relatively safe level approximately five minutes after the power cord is disconnected.

1 Determine the next step by comparing the power supply LEDs to the following table.

Power Supply LED

DS400 Primary Over Current is lit

All LEDs are off

All fault LEDs are off and DS440 is lit but a power supply problem is suspected

DS410 Overtemp is lit

DS440 Power Valid is lit but fan is not turning

DS430, 421,420, 411, or 401 secondary supply is lit

Step 7

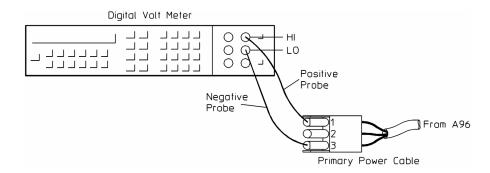

- 2 Check the A96 Primary Power Supply assembly's voltages.

- **a** Set the power switch to off (O) and disconnect the power cord from the rear panel.

- **b** Remove the top cover.

- **c** Wait five minutes to allow time for the power supply capacitors to discharge.

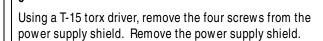

- **d** Remove the power supply shield located on top of the analyzer behind the display.

- **e** Remove the primary power cable connected to A95 P350.

f Connect a digital voltmeter to the primary power cable as shown below.

- **g** Connect the power cord to the rear panel.

- **h** Calculate the differential voltage for the local line voltage using the following table.

| Line Selector Switch | Differential Voltage ± 30 Vdc |  |

|----------------------|-------------------------------|--|

| 115 V                | Line Voltage (Vrms) x2.83     |  |

| 230 V                | Line Voltage (Vrms) x1.414    |  |

For example, if the local line voltage is 110 Vrms, then the calculated differential voltage is  $311 \pm 30$  Vdc.

- i If the measured voltage is not within ±30 Vdc of the calculated differential voltage, the A96 Primary Power Supply assembly is probably faulty.

- j Disconnect the power cord from the rear panel.

- **k** Wait five minutes to allow time for the power supply capacitors to discharge.

- I Disconnect the probes from the primary power cable and reconnect the cable to A95 P350.

#### To troubleshoot the power supply

- **3** Check the A96 Primary Power Supply assembly's ac bias voltages.

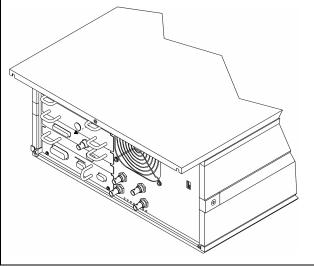

- **a** Place the analyzer on the side closest to the keypad.

- **b** Remove the bottom cover.

- **c** Wait five minutes to allow time for the power supply capacitors to discharge.

- **d** Remove the black power supply shield.

- **e** Connect the power cord and set the power switch to on (1).

- f Using an oscilloscope and two 1 M $\Omega$  10:1 probes, check the following ac bias supplies. See page 1-19 for component location.

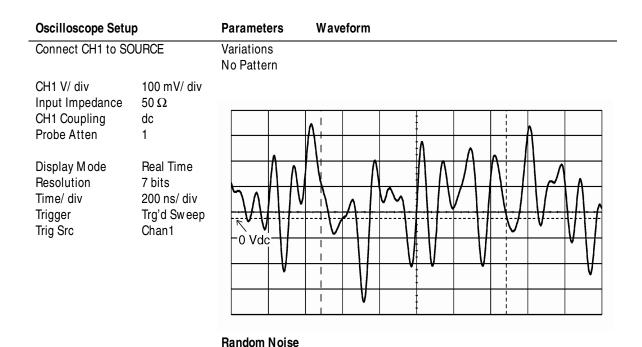

| Oscilloscope Setup                                                             | )                                                                 | Parameters                       | Waveform |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|----------|--|

| Connect CH1 to A99<br>Connect CH2 to A99                                       |                                                                   | Pulse Shape<br>Time Relationship |          |  |

| CH1 V/ div<br>Input Impedance<br>CH1 Coupling<br>Probe Atten                   | 20 V/ div<br>1 M Ω<br>dc<br>10                                    |                                  |          |  |

| Input Impedance<br>CH2 Coupling<br>Probe Atten                                 | $1 \text{ M}\Omega$ dc 10                                         |                                  |          |  |

| Display Mode<br>Averaging<br>Time/ div<br>Trigger<br>Trigger Level<br>Trig Src | Repetitive<br>8<br>5 ms/ div<br>Trg'd<br>Sweep<br>-1.8 V<br>Chan1 |                                  | ACBIAS   |  |

**g** If the waveforms are incorrect, the A96 Primary Power Supply assembly is probably faulty.

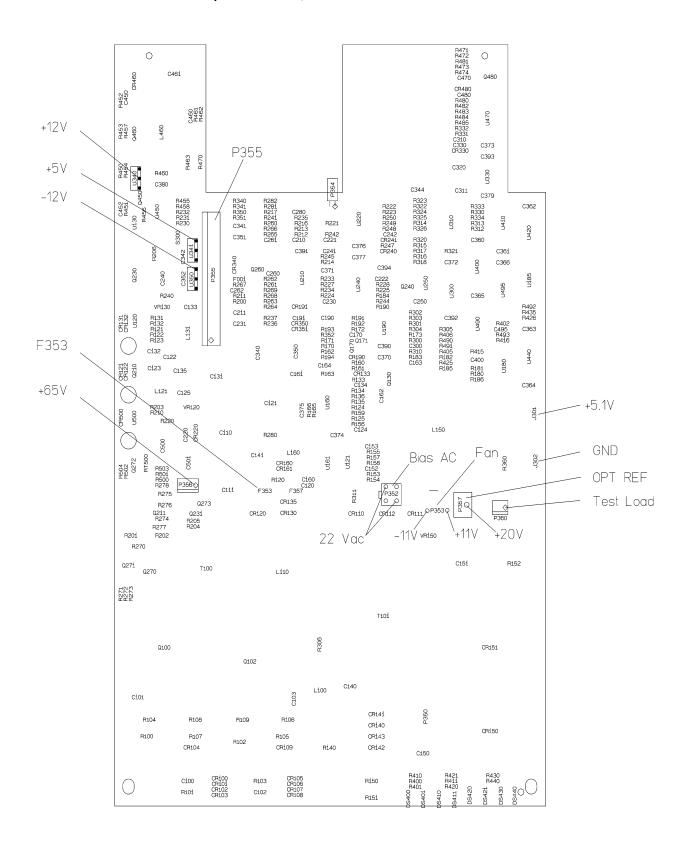

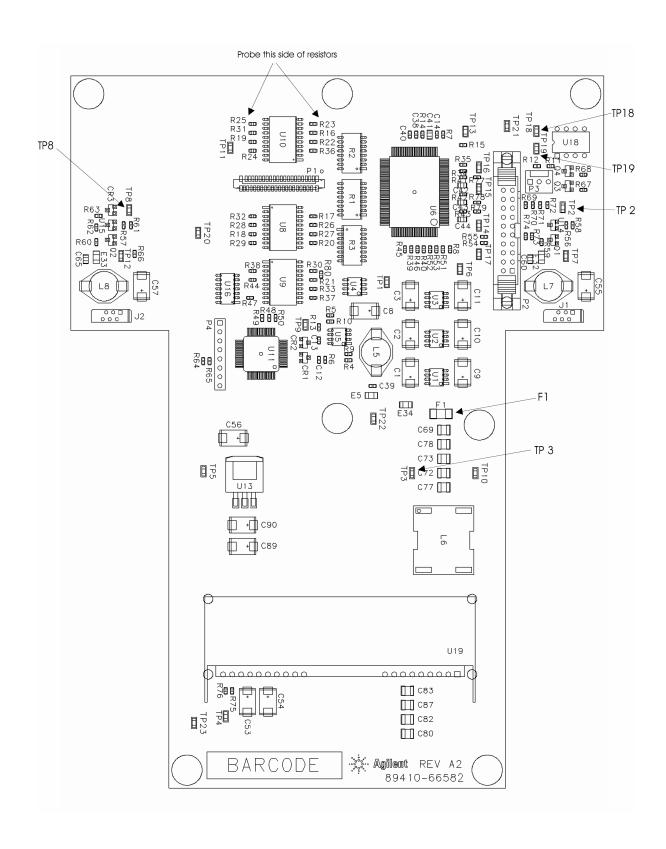

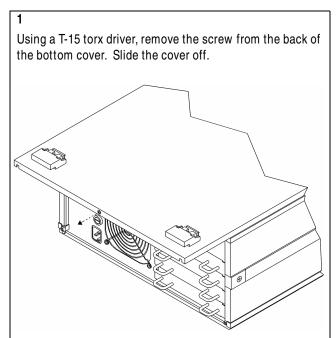

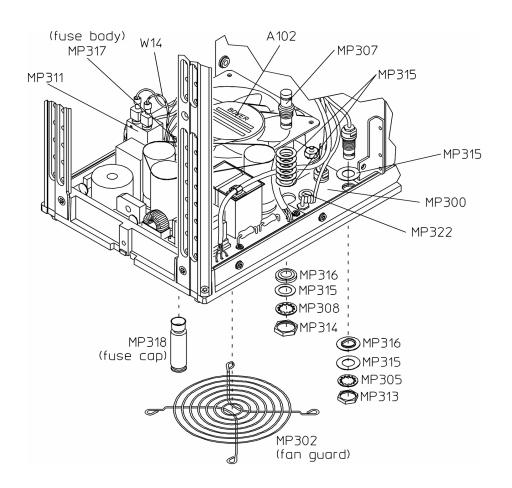

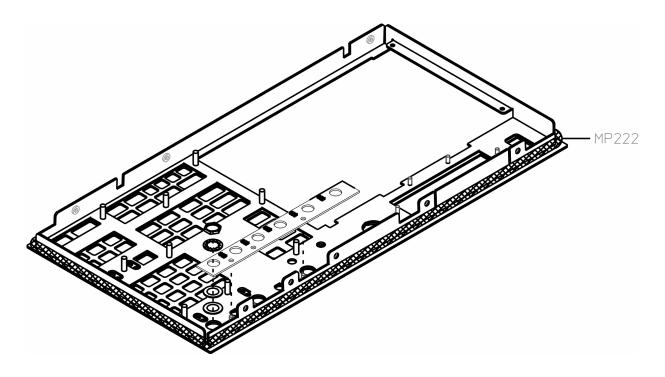

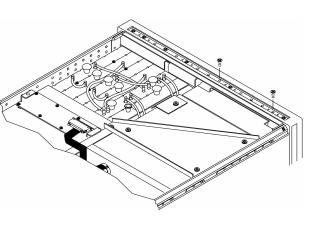

## A95 Component Locator, Bottom View

- 4 Check the A95 Main Power Supply assembly's bias supply voltages.

- a Check the bias supply voltages in the following table. The ripple should be no more than 50 mVp-p. Do not include high frequency line noise when measuring ripple.

| Test<br>Location | Nominal<br>Voltage | M inimum<br>Voltage | Maximum<br>Voltage | Ripple<br>Tolerance |

|------------------|--------------------|---------------------|--------------------|---------------------|

| U341, pin 3      | +5 V               | +4.5 V              | +5.5 V             | 50 mVp-p            |

| U340, pin 2      | +12 V              | +11.4 V             | +12.6 V            | 50 mVp-p            |

| U350, pin 3      | -12 V              | -12.6 V             | -11.4 V            | 50 mVp-p            |

- **b** If any of the voltages are incorrect, the A95 Main Power Supply is probably faulty.

- The A95 Main Power Supply assembly has no adjustments. Therefore if a voltage is incorrect, replace the assembly.

- **c** If the voltages are correct and the fan is turning, go to Step 7.

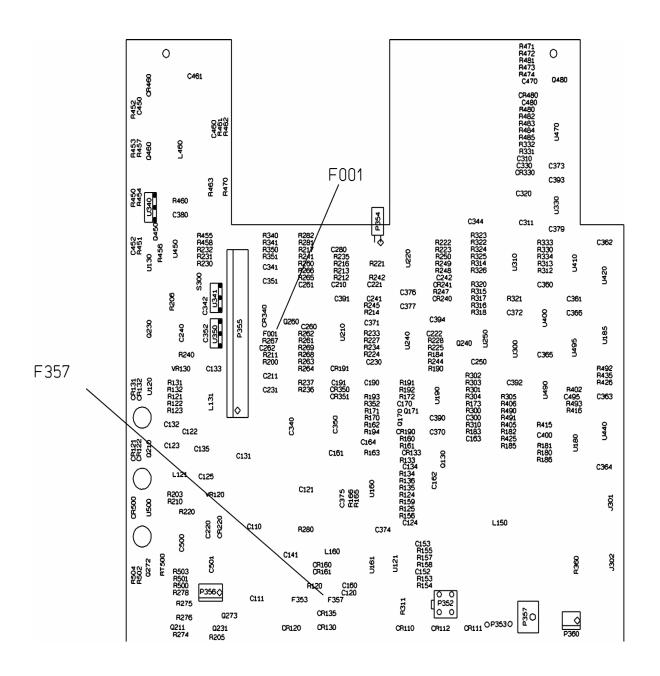

- **5** Check the supply voltage fuse for the A102 Fan assembly.

- **a** Set the power switch to off (O).

- **b** Wait five minutes to allow time for the power supply capacitors to discharge.

- **c** Measure the resistance across A95 F353.

- **d** If the resistance is greater than  $0\Omega$ , replace the fuse.

- 6 Check A102 Fan assembly.

- $\boldsymbol{a}$   $\;$  Set the power switch to off ( O ) and disconnect the power cord from the rear panel.

- **b** Remove the top cover.

- **c** Wait five minutes to allow time for the power supply capacitors to discharge.

- **d** Remove the power supply shield located on top of the analyzer behind the display.

- **e** Disconnect the fan power cable from A95 P353 (red and black cable).

- f Connect 10 Vdc to the fan cable. The fan should be turning slowly.

- **g** Increase the voltage to 24 Vdc. The fan should turn faster as the voltage increases.

- The power to the A102 Fan assembly is controlled by a thermistor which varies the fan voltage between +8 V when the analyzer is cold and +28 V when the analyzer is hot. The thermistor is on the A95 Main Power Supply assembly.

- **h** If the fan did not respond correctly, the Fan assembly is probably faulty.

- 7 Check A95 Main Power Supply assembly voltages.

- **a** Set the power switch to off (O) and disconnect the power cord from the rear panel.

- **b** Place the analyzer on the side closest to the keypad.

- **c** Remove the bottom cover.

- **d** Wait five minutes to allow time for the power supply capacitors to discharge.

- e Remove the black power supply shield.

- f Connect the power cord and set the power switch to on (1).

- g Check the voltages in following table.

The ripple should be no more than 50 mVp-p. Do not include high frequency line noise when measuring ripple. See page 1-19 for test locations.

| Test<br>Location | Nominal<br>Voltage ±10% | M inimum<br>Voltage | M aximum<br>Voltage |

|------------------|-------------------------|---------------------|---------------------|

| P353, pin 1      | +11 V                   | +8 V                | +28 V               |

| P353, pin 2      | –11 V                   | −11.6 V             | −10.5 V             |

| P357, pin 2      | +20 V                   | +17.0 V             | +23.0 V             |

| J301             | +5.1 V                  | +4.8 V              | +5.2 V              |

| P356, pin 1      | +65 V                   | +64.7 V             | +65.3 V             |

| P355, pin 1      | +8 V                    | +7.8 V              | +8.2 V              |

| P355, pin 3      | −8 V                    | −8.2 V              | −7.8 V              |

| P355, pin 5      | +15 V                   | +14.6 V             | +15.5 V             |

| P355, pin 7      | –15 V                   | −15.5 V             | −14.6 V             |

| P355, pin 14     | -5.2 V                  | −5.4 V              | -5.0 V              |

If the above voltages are correct, the fan is turning, and the power supply fault LEDs are off, the power supply is operating correctly.

- 8 Check for power supply loading.

- $\boldsymbol{a}$   $\;$  Set the power switch to off ( O ) and disconnect the power cord from the rear panel.

- **b** Place the analyzer on the side closest to the display.

- **c** Wait five minutes to allow time for the power supply capacitors to discharge.

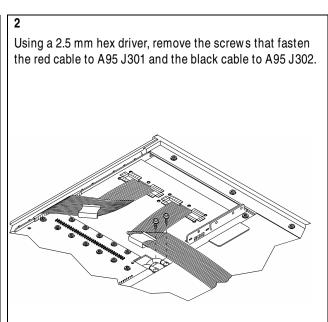

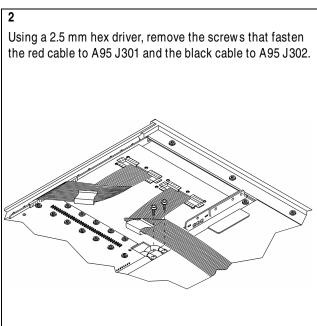

- **d** Disconnect the +5V (red) and GND (black) cables from J301 and J302.

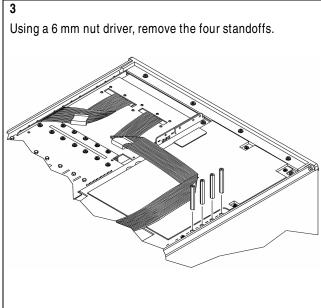

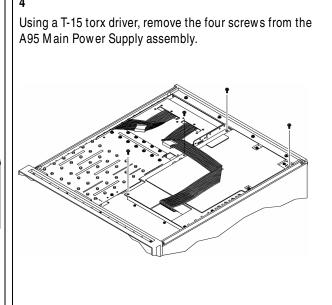

- **e** Remove the screws and standoffs holding the A95 Main Power Supply assembly in the chassis. See "To remove main power supply" on page 3-16

- f Disconnect the motherboard cable from A95 P355, the display power cable from A95 P356, and the optional oven cable from A95 P357.

- **g** Connect A95 J302 to the chassis.

- h Connect A95 P360 pins 2 and 3 together. This provides a test load for the power supply.

- i Place the A95 Main Power Supply assembly on its side. The assembly should not be touching the analyzer and it should still be connected to the A96 Primary Power Supply.

- **j** Connect the power cord and set the power switch to on (1).

- **k** Check the voltages in the table on page 1-21.

- I If the voltages are still incorrect, the A95 Main Power Supply assembly is probably faulty.

The voltages may vary slightly from the power supply nominal values due to the change in load.

- **9** Isolate assembly loading power supply.

- **a** Set the power switch to off (O) and disconnect the power cord from the rear panel.

- **b** Wait five minutes to allow time for the power supply capacitors to discharge.

- c Disconnect A95 P360 pins 2 and 3.

- **d** Reconnect all the cables to the A95 Main Power Supply assembly.

- e Reinstall the A95 Main Power Supply assembly in the analyzer.

- f Replace the black power supply shield and bottom cover.

- g Repeat the following steps for each assembly suspected of loading the power supply.

Use the Power Supply Voltage Distribution table on page 6- and the A90/A91 Motherboard Voltages table on page 6- to help isolate the failing assembly.

- **h** Set the power switch to off (O).

- i Remove the suspected assembly or the power cable to the assembly.

- j Set the power switch to on (1).

- **k** Check the voltages in the table on page 1-21.

## To troubleshoot display failures

Use this test to separate A100 Display assembly failures from A47 DSP/Display Controller assembly failures. If the screen is blank or the grid is not displayed, do initial verification on page 1-10 to determine if the A40 CPU assembly is faulty.

- 1 Check the display controller signals.

- **a** Set the power switch to off (O).

- **b** Remove the top cover.

- **c** Disconnect the ribbon cable from A90 P10.

## To troubleshoot display failures

- **d** Set the power switch to on (1).

- **e** Check the following display signals using a voltmeter.

| Test Location  | Signal Name | Amplitude (±10%) |

|----------------|-------------|------------------|

| A90 P10 pin 7  | 490 mVdc    | INTEN            |

| A90 P10 pin 15 | R           | 25 to 45 mVdc    |

| A90 P10 pin 17 | G           | 25 to 45 mVdc    |

| A90 P10 pin 19 | В           | 25 to 45 mVdc    |

- f If any of the signals are incorrect, the A47 DSP/Display Controller assembly is probably faulty.

- **2** Determine the probable faulty assembly by comparing the analyzer's symptoms to the following table.

| Symptom                                                                                                                                                                                                                                                       | Probable Faulty Assembly    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Vertical and horizontal scanning is occurring. Part of information is missing, for example only half letters. Blocks of information are missing. Information on the screen is scrambled or mixed up. Vertical or horizontal stripes appear across the screen. | A47 DSP/ Display Controller |

| Screen is blank. Screen is tilted, compressed, or distorted. Line across the screen.                                                                                                                                                                          | A100 Display †              |

$<sup>\</sup>dagger$  Before replacing the A100 Display assembly, go to page 1-15''To troubleshoot the power supply,'' and do Step 7 to check the +65 V power supply voltage.

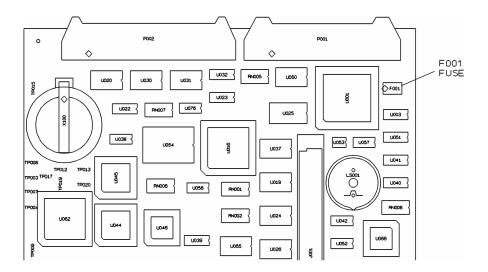

- 3 Check the +65 Vdc power supply.

- **a** Set the power switch to off (O).

- b Place the front panel in the A82 test position. (see Chapter 3, "To place the A82 in the test position", on page 3-12.)

- **c** Set the power switch to on (1).

- d Check for +65 Vdc ± 10% at TP3 using a Voltmeter.

- **e** If the voltage is correct, continue with step 4.

- f Check for +65 Vdc on both sides of F1.

- **g** If the voltage is correct on one side of F1 and incorrect on the other replace F1.

- h If the voltage is incorrect on both sides of F1, then the A95 Main Power Supply is probably faulty.

- 4 Check the programming signals from A81 to A82.

- **a** Using a logic probe verify that TTL logic pulses are present at TP 18 and TP19 within 30 seconds of power up. These test points will remain high after programming is complete.

- **b** If the signals are incorrect at TP18 or TP19 the A81 Keyboard Assembly is probably faulty.

- 5 Check the digital output signals to the LCD display.

- **a** Using a logic probe verify that TTL logic pulses are present at the following locations:

| Signal Line | Probe Location |

|-------------|----------------|

| В0          | R31            |

| B1          | R19            |

| B2          | R24            |

| B3          | R23            |

| B4          | R16            |

| B5          | R22            |

| G0          | R32            |

| G1          | R20            |

| G2          | R27            |

| G3          | R26            |

| G4          | R17            |

| G5          | R25            |

| R0          | R33            |

| R1          | R21            |

| R2          | R30            |

| R3          | R29            |

| R4          | R18            |

| R5          | R28            |

| DENA        | R36            |

| VSYNC       | R38            |

| HSYNC       | R37            |

| CLK         | R44            |

- **b** If any of the signals are incorrect, the A82 LCD Interface assembly is probably faulty

- **c** Verify the back lights and inverter boards. When the display is in the test position the back lights are visible from the side of the display. Use this procedure if one or both are not lit.

- **a** Press Display, more display setup, color setup, brightness, 100%. The brightness level controls the voltage applied to the back lights.

- **b** Check for +4.5 Vdc ± 0.2 V at A82 TP2 using a voltmeter.

- **c** If this voltage is incorrect then the A47 assembly is probably faulty.

- **d** Check for +1.2 Vdc ± 0.2 V at A82 TP8 using a voltmeter.

- **e** If this voltage is incorrect then the A82 assembly is probably faulty.

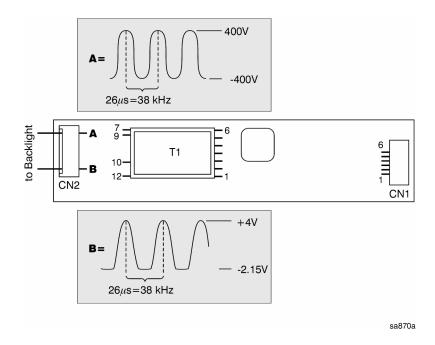

- f Check the input and output signals of the inverter board as listed below.

| Test Point | Signal or Voltage                                |

|------------|--------------------------------------------------|

| CN 1 pin 1 | + 4.9 Vdc                                        |

| CN 1 pin 2 | + 4.9 Vdc                                        |

| CN 1 pin 6 | + 1.2 Vdc                                        |

| CN 2 A     | - 400 V to + 400 V sinewave @ 38kHz (see figure) |

| CN 2 B     | - 2.15 V to + 4 V sinewave @ 38 kHz (see figure) |

- **g** If the inputs to the inverter are incorrect the cable is probably faulty.

- **h** If the outputs of the inverter are incorrect then the inverter is probably faulty.

- i If the outputs of the inverter are correct then the back light is probably faulty.

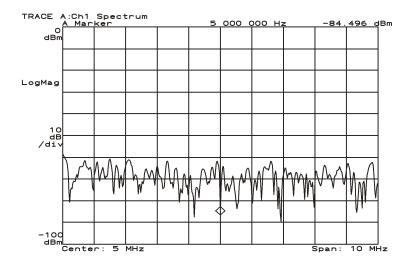

# To perform self tests

Use this test when the keyboard is active and one of the following occurs:

- An error message is displayed

- Calibration fails

- Performance test fails

- Failure is intermittent

- Interface port fails

- Probe power fails

- Sync out fails

- 1 Check sample clocks.

- **a** Remove the top cover.

- **b** Set the power switch to on (1).

- **c** Using an oscilloscope and 2 BNC(m)-to-SMB(f) cables, check the following signals.

| Oscilloscope Setup                                                     | Parameters                                     | Waveform |

|------------------------------------------------------------------------|------------------------------------------------|----------|

| Connect CH1 to A60 J3<br>Connect CH2 to A60 J2                         | Time<br>Duty Cycle<br>Time Relationsh          | nip      |

| Input Impedance 50<br>CH1 Coupling do<br>Probe Atten 1<br>CH2 V/ div 1 | V/ div                                         |          |

| Averaging 8 Time/ div 10 Trigger Tr                                    | epetitive Ons/ div g'd Sweep han1 Sample Clock |          |

- **d** If either signal is incorrect, the A60 Frequency Reference assembly is probably faulty.

- e Reconnect the cables to A60 J3 and A60 J2.

- **2** Check for failing power-up results.

- **a** Press the following keys:

### [System Utility]

[auto cal off]

[more cal setup]

[auto zero cal off]

[Return]

[more]

[diagnostics]

[service functions]

1125

[enter]

[test log]

During the additional hardware power-up test, the A40 CPU assembly requests the hardware revision numbers from the following assemblies:

A30 Digital Source

A35 Analog Source

A36 Trigger

A55/A56 Sample RAM

A71 Pass Through

A50 Digital Filter (listed as Lo/Df in test log)

A10 Analog Input (listed as channel 1 or 2 front end in test log)

A21 A/D Converter (listed as channel 1 or 2 ADC in test log)

A43 Expanded Memory (listed as Option UFG ROM in test log)

The A10 Analog Input, A21 A/D Converter, and A36 Trigger assemblies send their revision numbers through the A30 Digital Source assembly. The following shows a passing test log entry for the Power-up functional tests.

| ower-up f | functi | onal | . 1 | tes | sts | 5 |  |   |  |  |      |

|-----------|--------|------|-----|-----|-----|---|--|---|--|--|------|

| ult fctn  | perip  | hera | 1   |     |     |   |  |   |  |  | PASS |

| VRAM      |        |      |     |     |     |   |  |   |  |  | PASS |

| eal time  |        |      |     |     |     |   |  |   |  |  |      |

| IN contro |        |      |     |     |     |   |  |   |  |  |      |

| ont pane  |        |      |     |     |     |   |  |   |  |  |      |

| SP/bus .  |        |      |     |     |     |   |  |   |  |  |      |

| dditional |        |      |     |     |     |   |  |   |  |  |      |

| ample RAN |        |      |     |     |     |   |  |   |  |  |      |

|           |        |      |     |     |     |   |  |   |  |  |      |

| SP proces | SSOF   |      |     |     |     |   |  | ٠ |  |  | PASS |

Determine the probable faulty assembly and next test or step by comparing the power-up test results to the following table.

The power-up tests are listed in the order they are ran. If power-up test messages match more than one entry in the table, use the entry closest to the beginning of the table. Assemblies are listed in order of probable failure when more than one assembly can cause the failure.

## Power-up Troubleshooting Guide

| Failing Self Test or M essage Displayed                                                                                                       | Probable Faulty Assembly                           | Next Test or Next Step    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------|--|--|

| M C68030 Processor<br>M C68882 Coprocessor<br>Boot ROM<br>Stack RAM<br>Main RAM                                                               | A40 CPU                                            |                           |  |  |

| Display RAM<br>DSP RAM                                                                                                                        | A47 DSP/ Display Controller                        |                           |  |  |

| Program ROM                                                                                                                                   | A42 Memory                                         |                           |  |  |

| Mult fctn peripheral                                                                                                                          | A40 CPU                                            |                           |  |  |

| NVRAM<br>Real time clock                                                                                                                      | memory battery<br>A42 Memory                       | Memory battery, page 1-93 |  |  |

| DIN controller FP kbd interface on memory board does not respond Failure during keyboard initialization                                       | A42 Memory                                         |                           |  |  |

| Front panel keyboard revision problem                                                                                                         | A80 Keyboard                                       |                           |  |  |

| DSP/ bus                                                                                                                                      | A47 DSP/ Display Controller                        |                           |  |  |

| DSP processor DSP processor information: Failure during Sample RAM/ DSP interface test                                                        | A55/ A56 Sample RAM<br>A47 DSP/ Display Controller |                           |  |  |

| DSP processor                                                                                                                                 | A47 DSP/ Display Controller                        |                           |  |  |

| LAN ROM                                                                                                                                       | A43 Expanded Memory                                |                           |  |  |

| Additional hardware Additional hardware information: Any of the following:                                                                    |                                                    |                           |  |  |

| Digital Source not found Digital Source address read problem! Digital Source revision read problem! Unable to program Digital Source hardware | A30 Digital Source                                 |                           |  |  |

## Power-up Troubleshooting Guide

Internal Control Path 3 open Unable to write/ read Internal Control Path 3 Unable to read Internal Control Path 3 Unable to program Source DC offset

A35 Analog Source A36 Trigger A30 Digital Source

Front-end control, page 1-60-

Extended RAM and Additional I/O not found

Extended RAM Board Bus Error

A43 Expanded Memory

| Failing Self Test or Message Displayed                                                                                                                                                                                     | Probable Faulty Assembly                                     | <b>Next Test or Next Step</b>                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Additional hardware (continued) Additional hardware information: Any of the following:                                                                                                                                     |                                                              |                                                                                                    |

| Trigger Board not found<br>Unable to download default Trigger GA                                                                                                                                                           | A36 Trigger                                                  |                                                                                                    |

| Sample RAM not found<br>Sample/ Capture RAM not found<br>Sample RAM revision read problem!<br>Unable to read Sample RAM hardware ID<br>Unable to program Sample RAM hardware                                               | A55/ A56 Sample RAM                                          |                                                                                                    |

| Pass Thru not found Pass Thru address read problem! Pass Thru revision read problem! Unable to write Pass Thru control register                                                                                            | A71 Pass Through                                             |                                                                                                    |

| Lo/ Df not found Lo/ Df address read problem! Lo/ Df revision read problem Lo/ Df Channel 1 not found Lo/ Df Channel 2 not found Unable to reset Lo/ Df Unable to write Lo/ Df control register IF Trigger RAM test failed | A50 Digital Filter                                           |                                                                                                    |

| Channel 1 Control Path test failed<br>Channel 2 Control Path test failed                                                                                                                                                   | A10 Analog Input<br>A21 A/ D Converter<br>A30 Digital Source | Front-end control, page 1-60                                                                       |

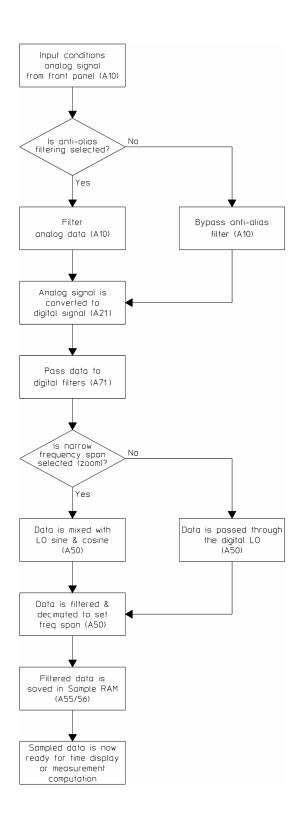

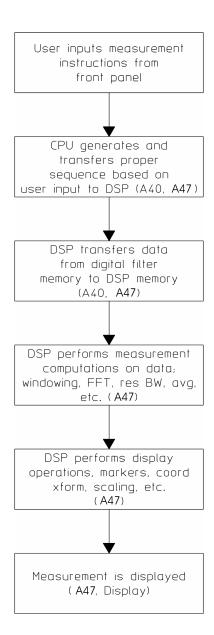

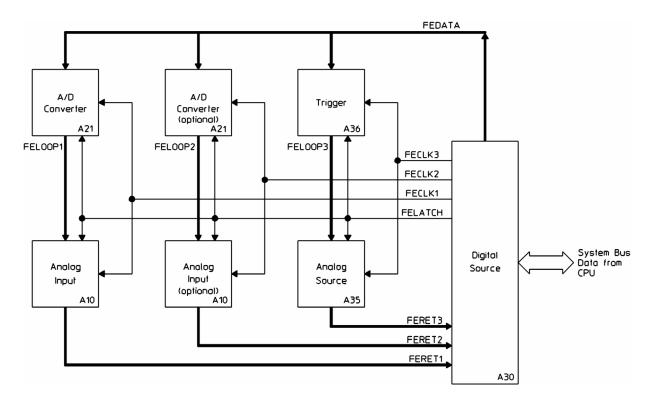

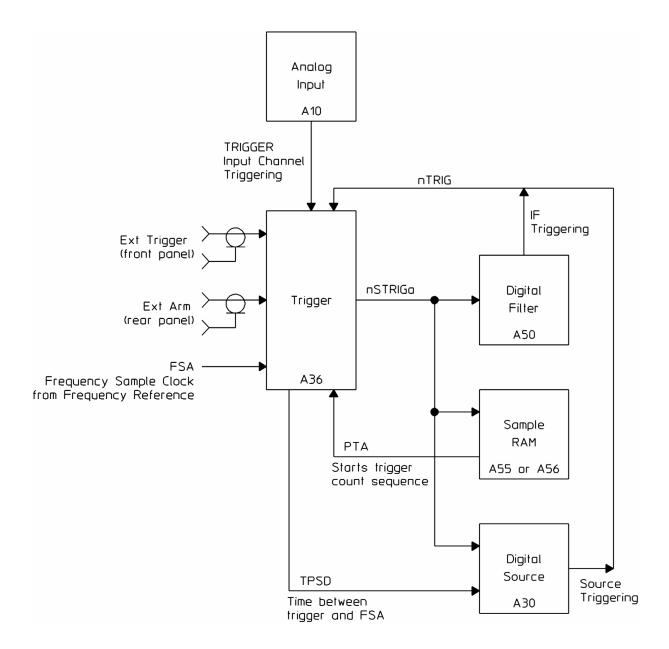

| Channel <i>number</i> ADC not found                                                                                                                                                                                        | A21 A/ D Converter, channel number                           |                                                                                                    |